Fターム[5F083AD04]の内容

半導体メモリ (164,393) | DRAM (5,853) | 読出しトランジスタ (1,433) | 水平方向以外のチャネルを有するもの (541) | トレンチゲートトランジスタ(単孔にゲートを埋込むもの) (266)

Fターム[5F083AD04]に分類される特許

161 - 180 / 266

半導体装置及びその製造方法並びにデータ処理システム

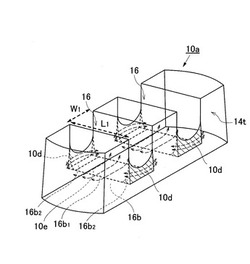

【課題】トレンチゲート型トランジスタのサブスレショルド特性の向上を図りつつ、ゲートトレンチの幅が縮小された高性能な半導体装置を提供する。

【解決手段】ゲートトレンチ16の底部16bは、STI14から相対的に遠い第1の底部16b1と、STI14から相対的に近い第2の底部16b2を有している。そして、活性領域10aのうち、ゲートトレンチの第2の底部16b2を構成する部分は、側壁チャネル領域10dを構成し、ゲート電極18とSTI14との間に挟まれた薄膜SOI構造を有している。一方、ゲートトレンチの第1の底部16b1を構成する部分は、副チャネル領域10eとして機能する。第2の底部16b2の曲率半径は第1の底部16b1の曲率半径よりも大きい。ゲートトレンチ16の幅方向の略中央部分においては、トレンチの底面が略平坦であるのに対し、幅方向の端部においては、トレンチの底面がほぼ全体的に湾曲している。

(もっと読む)

半導体装置、半導体装置の製造方法並びにデータ処理システム

【課題】特別なプロセス、構造、工程を必要とせずに各種使用電圧に対応することのできる縦型SGT構造を備えた半導体装置とその製造方法を提供する。

【解決手段】本発明の半導体装置は、同一基板上に高耐圧トランジスタと低耐圧トランジスタとを混載してなる半導体装置であって、低耐圧トランジスタは、基板1上に立設された半導体の基柱5と、基柱5の外周面に設けられたゲート電極11と、基柱5の上下に設けられたソース拡散層16及びドレイン拡散層9と、を備えた単一の単位トランジスタ50によって形成され、高耐圧トランジスタは、低耐圧トランジスタを構成する単位トランジスタ50の基柱5の高さと同じ高さの半導体の基柱5を有する複数の単位トランジスタ50のソース拡散層16とドレイン拡散層9を直列に接続し、且つ複数の単位トランジスタ50のゲート電極11同士を電気的に接続することによって形成されている。

(もっと読む)

厚さが減少した半導体素子、これを採用する電子製品及びその製造方法

【課題】厚さが減少した半導体素子、これを採用する電子製品及びその製造方法を提供する。

【解決手段】この半導体素子の製造方法は第1及び第2活性領域を有する半導体基板を準備する工程を含む。前記第1活性領域に第1ゲートパターン及び第1不純物領域を含む第1トランジスタを形成する。前記第2活性領域に第2ゲートパターン及び第2不純物領域を含む第2トランジスタを形成する。前記第1トランジスタ上に第1導電性パターンを形成する。前記第1導電性パターンの少なくとも一部と前記第2ゲートパターンの少なくとも一部は前記半導体基板の上部表面から同一距離に配置される。前記第1導電性パターンは前記第2ゲートパターンを形成する間に形成される。

(もっと読む)

スプリット仕事関数ゲートを含むMOSFETを有する集積回路

【課題】ゲート誘起ドレインリーク電流が少ない電界効果トランジスタ、および、ゲート電極とソース/ドレイン領域との間に薄い絶縁体構造物を含む集積回路を提供する。

【解決手段】トランジスタ542のゲート電極は、ゲート電極とチャネル領域512との間の第1のフラットバンド電圧を決定する主部532と第1の側部535とを含む。この第1の側部は、上記主部に接触すると共に、上記ゲート電極と第1のソース/ドレイン領域514,516との間の第2のフラットバンド電圧を決定する。上記第1のフラットバンド電圧および上記第2のフラットバンド電圧は、少なくとも0.1eVだけ異なる。

(もっと読む)

半導体装置及びその製造方法

【課題】活性領域及び素子分離領域に形成される複数のゲートトレンチの溝幅がほぼ設計通りであり、素子の微細化が可能な半導体装置及びその製造方法を提供する。

提供する。

【解決手段】ハードマスク105hを形成する前に第1のポリシリコン膜104を形成し、且つハードマスク105hを除去する前に第1及び第2のゲートトレンチ106及び107内にゲート電極となる第2のポリシリコン膜109を埋め込む。その後、ハードマスク105hを除去するための熱リン酸によるウェットエッチングを行う。このとき、第1のゲートトレンチ106内は第2のポリシリコン膜109で保護され、半導体基板100上は第1のポリシリコン膜104で保護された状態となっている。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチゲートトランジスタにおいて、溝に埋め込まれたゲート電極とゲート絶縁膜との界面にボイドが形成されることを防止する。

【解決手段】半導体基板1に埋め込まれた素子分離絶縁膜3により絶縁分離された活性領域4と、ゲート絶縁膜5を介して活性領域4上を跨ぐように形成されたゲート電極6と、ゲート電極6を挟んだ両側の活性領域4に形成されたソース領域7a及びドレイン領域7bとを有し、活性領域4に溝8が設けられて、この溝8の内側にゲート絶縁膜5を介してゲート電極6の一部が埋め込まれてなるトレンチゲートトランジスタ51を備える半導体装置であって、溝8が少なくとも上端開口部よりも下部側において幅広となる形状を有し、溝8に埋め込まれたゲート電極6内に外殻層13aで覆われた中空部(ボイド)14が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】溝型トランジスタとPNゲートで構成されるプレーナ型トランジスタとが共存する半導体装置において、溝型トランジスタの溝ゲートの空乏化現象によるオン電流の低下を抑制し、溝型トランジスタと異なる導電型のP又はNゲートで構成されるプレーナ型トランジスタの閾値電圧のバラツキ増加を防止する。

【解決手段】溝型トランジスタのゲート電極であるポリシリコン膜中に高濃度不純物拡散材料9が埋設された構造を有する。

(もっと読む)

メモリーデバイス

【課題】本発明は、エラーレートが低く、高速で応答すると共に、低コストで製造することが可能なメモリーデバイスを提供することを目的とする。

【解決手段】メモリーデバイス100Aは、基板101上に、ゲート電極102が絶縁層103で覆われている凸部が形成されており、凸部の頂部に、導電層104bが形成されており、基板101上の凸部に対して一方の側に、ソース電極104aが形成されており、基板101上の凸部に対してソース電極104aが形成されていない側に、ドレイン電極104cが形成されており、導電層104bとソース電極104a及び導電層104bとドレイン電極104cの間に存在する絶縁層103上に半導体層105が形成されているトランジスタを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】十分な信頼性を有しながら微細化に適した素子構造を有する半導体装置を提供する。

【解決手段】半導体基板と、この半導体基板上に設けられた第1の電界効果トランジスタを含むメモリセルを複数有するメモリセルアレーと、前記半導体基板上に設けられた、前記メモリセル内のメモリセルを動作させるための第2の電界効果トランジスタとを有する半導体装置であって、第1の電界効果トランジスタは、第1の溝と、第1の溝内に設けられた第1のゲート絶縁膜と、第1の溝を埋め込むように設けられた第1のゲート電極と、第1の拡散領域とを有し、第2の電界効果トランジスタは、第1の溝と同じ深さをもつ第2の溝と、第2の溝内に設けられた第2のゲート絶縁膜と、第2の溝を埋め込むように設けられた第2のゲート電極と、第2の拡散領域とを有する半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】フィン下部でのVthの上昇が得られると共に、サブチャネルによるソース領域とドレイン領域との間のリーク電流を抑えることを可能とした半導体装置及びその製造方法を提供する。

【解決手段】基板2に埋め込まれた素子分離絶縁膜3により絶縁分離された活性領域4と、活性領域4上に形成されたゲート絶縁膜5と、ゲート絶縁膜5を介して活性領域4上を跨ぐように形成されたゲート電極6とを備え、活性領域4の両側に溝15が設けられ、この溝15の内側にゲート絶縁膜5を介してゲート電極6の一部が埋め込まれることによって、溝15の間で立ち上がり形成されたフィン16をゲート電極6が跨ぐように形成されたフィン型のチャネル構造を有するフィン型FET1において、ゲート絶縁膜5の溝15の底面15aに接する部分の膜厚SBをフィン16の上面16bに接する部分の膜厚STよりも厚くする。

(もっと読む)

半導体装置の製造方法

【課題】素子特性の優れた半導体装置を簡便に製造する。

【解決手段】第1の溝内の素子分離膜と活性領域を有する半導体基板を用意する工程と、この半導体基板上にマスク形成用膜を形成する工程と、活性領域を横切る開口を有する第1のマスクを形成する工程と、第1のマスクを用いて異方性エッチングを行って、前記マスク形成用膜からなる第2のマスクと、活性領域内に、対向する素子分離膜露出面を有し且つ第1の溝より浅い第2の溝を形成する工程と、第2の溝内の半導体基板表面と素子分離膜露出面との境界を含む領域に酸素イオンが照射されるように、第2のマスクを用いて酸素イオンを斜めに注入する工程と、第2の溝内の酸素イオンが注入された領域を酸化して酸化領域を形成する工程と、この酸化領域を除去する工程を有する半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】溝を加工する際に生じるバリを効率的に除去しながら溝の形状を最適化し、寄生チャネルやリーク電流を生じない半導体装置及びその製造方法を提供することを目的とする。

【解決手段】溝11は、活性領域K側に位置し開口部11aと連結している一対の第2内壁11cの断面輪郭線を略直線状に形成し、水素ベーク処理によりバリ11eを除去もしくは低減する第1バリ除去工程と、酸化処理によって溝11の表面に保護膜14を形成する保護膜形成工程と、保護膜14が形成された溝11の表面に水素ベーク処理を行い、第2内壁11cの断面輪郭線を略直線状に保ちながら、残存しているバリ11eを更に除去もしくは低減する第2バリ除去工程とを有することを特徴とする。

(もっと読む)

トランジスタ、集積回路および集積回路形成方法

【課題】トランジスタ、集積回路、および、集積回路形成方法を提供する。

【解決手段】半導体基板1内に形成されたゲート溝27内にゲート誘電体24を介してゲート電極23が配置された構成を有する。該ゲート電極23は、導電性炭素材を有している。

(もっと読む)

メモリセルアレイを備えた集積回路および集積回路の形成方法

【課題】メモリセルアレイを備えた集積回路、および集積回路の形成方法を提供する。

【解決手段】第1方向62に沿って伸びる各ビット線61と、第1方向62とは実質的に直交する第2方向63に沿って伸びる各ワード線60と、各能動領域40と、各ビット線コンタクト57とを提供する。各ビット線コンタクト57は、第2方向63に沿って伸びる各列と、第1方向62に沿って伸びる各行とに配置されている。隣り合う各ビット線61間の距離をdLとし、隣り合う各ビット線コンタクト57間における第1方向62に対して平行な距離をdCとすると、1/2.25≦dL/dC≦1/1.75という関係が成り立っている。

(もっと読む)

自己整合方式でリセスゲートMOSトランジスタ素子を製作する方法

【課題】自己整合方式でリセスゲートMOSトランジスタ素子を製作する方法を提供する。

【解決手段】本発明による方法で製作されたMOSトランジスタ素子は、側壁と底部を有するゲート溝を備える基板と、ゲート溝の側壁に設けられるドレイン/ソースドープ領域と、ゲート溝の底部に設けられるゲートチャネル領域と、ゲート溝の側壁と底部に設けられ、ゲート溝の側壁における第一膜厚とゲート溝の底部における第二膜厚が相違するゲート酸化膜と、ゲート溝に埋め込まれるゲート導体とを含む。

(もっと読む)

リセスチャネル構造を有するトランジスタを含む半導体装置およびその製造方法

【課題】特性異常の発生を低減することのできるリセスチャネル構造を有するトランジスタを含む半導体装置およびその製造方法を提供すること。

【解決手段】半導体シリコン基板の活性領域に設けられた第一のリセスおよび素子分離領域に設けられた第二のリセスと、リセスチャネル構造を有するトランジスタと、を少なくとも有する半導体装置であって、

前記トランジスタは、前記第一のリセス内部に設けられたゲート電極を有し、

前記ゲート電極は、前記第一のリセス内部に設けられた部分に加えて、前記第二のリセス内部に設けられた部分を有し、

前記第一のリセス内部に設けられた前記ゲート電極の部分と、前記第二のリセス内部に設けられた前記ゲート電極の部分とは、前記活性領域と前記素子分離領域との境界面と同一の面で互いに電気的に接続されていることを特徴とする半導体装置およびその製造方法。

(もっと読む)

半導体装置の製造方法

【課題】溝型トランジスタと高耐圧トランジスタのエクステンション領域の形成となるイオン注入工程を同一のフォトリソグラフィ工程中において行える製造方法の提供を目的とする。

【解決手段】溝型セルトランジスタ領域に溝を形成し、半導体基板上にゲート絶縁膜とゲート材料層を形成し、溝型セルトランジスタ領域と、高耐圧トランジスタ領域のエクステンション領域形成部とを露出させたフォトレジスト層を半導体基板上に形成し、溝型セルトランジスタ領域の半導体基板表面と高耐圧トランジスタ領域へイオン注入を行って各領域のエクステンション領域を形成した後、さらにゲートをパターニング後、溝型セルトランジスタ領域と高耐圧トランジスタ領域とをフォトレジスト層で覆って通常耐圧トランジスタ領域へイオン注入を行って該領域のエクステンション領域を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】DRAM等に代表される半導体装置の高集積化、微細構造化が進展した場合であっても、量産に適した構造を有するリセスチャネル構造を有するトランジスタを含む半導体装置を提供すること。

【解決手段】半導体シリコン基板の一部の表面上に成長された選択エピタキシャルシリコン層と、ゲート電極に対応したソース領域およびドレイン領域とを少なくとも有し、

前記ソース領域は、前記半導体シリコン基板の表面領域に形成され、

前記ドレイン領域は、前記選択エピタキシャルシリコン層および前記選択エピタキシャルシリコン層下部の前記半導体シリコン基板の表面領域に形成されているリセスチャネル構造を有する非対称型トランジスタ、を含むことを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極上に積層するポリサイド層、バリアメタル層、メタル層、絶縁膜ハードマスクの膜剥がれを抑制する効果を発揮させた半導体装置およびその製造方法を提供することを目的とする。

【解決手段】トレンチゲート型のMOSトランジスタTr1、Tr2を備えた半導体装置の製造方法であって、半導体基板1の表面にトレンチ12、13を形成してからゲート絶縁膜20を形成する工程と、前記半導体基板1上にゲート電極8用のポリシリコン層を形成する工程と、前記トレンチ12、13上に位置する前記ポリシリコン層の上面に生じた凹部を除くための水素雰囲気中アニールを行なう工程と、前記ポリシリコン層を選択的に除去することによりトレンチ12、13上のポリシリコン層を残してこれをゲート電極8とする工程とを具備してなることを特徴とする半導体装置の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置及びその製造方法

【課題】溝型MISFETを備える半導体装置であって、素子分離絶縁層に形成されたボイドを介したゲート電極間のショートを抑制する。

【解決手段】 半導体装置は、半導体基板上に溝型MISFETを備える。MISFETのゲート電極15が、シリコン基板11の素子形成領域の表面と同じ高さに研磨された素子分離絶縁層13の表面上に延びる第1の部分と、第1の部分から延長し、素子形成領域14の内部に形成されたゲートトレンチ16内にゲート酸化膜を介して埋め込まれた第2の部分とを有する。

(もっと読む)

161 - 180 / 266

[ Back to top ]