Fターム[5F083AD04]の内容

半導体メモリ (164,393) | DRAM (5,853) | 読出しトランジスタ (1,433) | 水平方向以外のチャネルを有するもの (541) | トレンチゲートトランジスタ(単孔にゲートを埋込むもの) (266)

Fターム[5F083AD04]に分類される特許

101 - 120 / 266

半導体装置およびその製造方法

【課題】第1の領域中の層間絶縁膜を湿式エッチングにより除去する際に、使用する薬液が第2の領域に浸透することを防止する。これにより、第2の領域の特性の劣化がない、高性能の半導体装置を提供する。

【解決手段】第1の領域と、第1の領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた第2の領域と、を有する半導体装置。第1の領域は、導電性を有する第1の膜によって構成された第1の電極を有する。第1の領域中の第1の電極の表面は、第2の膜で覆われていない。ガードリングは、凹状の溝の内壁を覆う第1の膜と、凹状の溝の内部において少なくとも第1の膜の表面の一部を覆う絶縁性の第2の膜を有する。

(もっと読む)

半導体ウエハ、半導体ウエハの製造方法、および半導体装置

【課題】ヒューズ素子形成領域の配線を露出させることなく、クラックストップトレンチとボンディングパッド開口部を同時に形成する半導体ウエハ及びその製造方法を提供する。

【解決手段】半導体基板と多層配線構造とを少なくとも具備してなり、前記多層配線構造がチップ領域Aとヒューズ素子形成領域Bおよびダイシング領域Cとに渡って形成されてなる半導体ウエハにおいて、前記チップ領域に位置する前記多層配線構造上には、前記配線で構成されたボンディングパッド170が形成される一方、前記ダイシング領域には、前記多層配線構造が一部除去されることによって形成された二本以上が並行して並ぶダミーリングおよび、前記ダミーリング間に形成された、クラックストップトレンチ152となる溝部が設けられていることを特徴とする半導体ウエハを採用する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明はビット配線と半導体基板上の不純物拡散層とのコンタクト抵抗を低減した構造の提供を目的とする。

【解決手段】本発明は、半導体基板の一面に形成されたトレンチ溝内に、ゲート絶縁膜を介しゲート電極を含む埋込ワード線とその上に位置する埋込絶縁膜とが埋め込まれ、前記トレンチ溝に隣接する半導体基板一面の表面領域に不純物拡散層が形成され、前記不純物拡散層が形成された領域上にビット配線が形成されるとともに、前記不純物拡散層に接続されたビット配線の少なくとも底部側が、不純物をドープした不純物ドープ型のポリシリコンに更に不純物イオンを打ち込みしてなる注入ポリシリコン膜からなることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】工程数を削減することにより、製造コストを低減可能な半導体装置の製造方法を提供する。

【解決手段】メモリセル領域と周辺回路領域とアライメントマーク領域とを有する半導体装置の製造方法であって、素子分離膜8を形成する工程と、メモリセル領域の半導体基板上にシリコン膜121を形成する工程と、ゲート絶縁膜15を形成する工程と、埋め込みゲート電極23Aを形成する工程と、キャップ絶縁膜22を形成する工程と、半導体基板1の上面に層間絶縁膜24を形成する工程と、層間絶縁膜24にビットコンタクト開口部を形成する工程とを備え、半導体基板1の上面に層間絶縁膜24を形成する工程と、層間絶縁膜24にビットコンタクト開口部を形成する工程との間に、周辺回路領域のシリコン膜121及び基板表面を露出させるとともに、アライメントマーク領域にアライメントマーク123を形成することを特徴とする半導体装置の製造方法を選択する。

(もっと読む)

半導体装置の製造方法

【課題】配線層の加工マージンが大きく、微細化に適した半導体装置の製造方法を提供する。

【解決手段】半導体基板1にゲート電極溝を形成する工程と、ゲート電極溝の内壁面にゲート絶縁膜15を形成する工程と、ゲート電極溝の底部に埋め込みゲート電極23Aを形成する工程と、埋め込みゲート電極23Aの上面を覆うようにゲート電極溝の内部に絶縁膜を埋め込んだ後、エッチバックして当該ゲート電極溝の上部にキャップ絶縁膜22を形成する工程と、半導体基板1の上面に層間絶縁膜24を形成する工程と、層間絶縁膜24にビットコンタクト開口部を形成する工程と、を備え、半導体基板1の上面に層間絶縁膜24を形成する工程が、半導体基板1の上面とキャップ絶縁膜22の上面との間に生じた段差を埋め込むように層間絶縁膜24を成膜するとともに当該層間絶縁膜24の上面を平坦とすることを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量コンタクトプラグとキャパシタとの間の重ねマージンを十分に確保して、接続信頼性の高い半導体装置を提供する。

【解決手段】埋め込みゲート電極23Aと、半導体基板1上に設けられてビット線30を有する絶縁層33と、絶縁層33を貫通するように設けられた容量コンタクトプラグ41と、絶縁層33上に設けられて容量コンタクトプラグ41及びキャパシタの下部電極46と接続される容量コンタクトパッド42とを備え、容量コンタクトプラグ41が、半導体基板1側からポリシリコン層38a、シリサイド層39a、金属層からなる積層構造であり、容量コンタクトパッド42の底面と金属層の上面との接続部分以外の当該金属層の上面が、絶縁層33の上面からリセスされるとともに、シリサイド層39aの上面が、金属層によって被覆されていることを特徴とする半導体装置を選択する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】本発明はコンタクト開口をエッチングにより形成した場合にその下に位置する埋込絶縁膜がエッチングされないようにした構造の提供を目的とする。

【解決手段】本発明は、半導体基板の一面に複数のトレンチ溝を隣接形成する工程と、トレンチ溝の内壁にゲート絶縁膜を形成する工程と、トレンチ溝の下部内側のゲート絶縁膜上に埋込ワード線を形成する工程と、トレンチ溝内の埋込ワード線上に硼素リンケイ酸ガラスからなる埋込絶縁膜を形成する工程と、埋込絶縁膜及び半導体基板上に層間絶縁膜を形成する工程と、層間絶縁膜に埋込絶縁膜及びそれに隣接する半導体基板一面に達するコンタクト開口をエッチングにより形成する工程と、コンタクト開口を介して半導体基板一面上に配線を形成することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】短チャネル効果の発生を抑制できる半導体装置及びその製造方法の提供。

【解決手段】本発明の半導体装置は、半導体基板1の活性領域上にゲート絶縁膜5aを介して形成されたゲート電極105と、ゲート電極105側面を覆う第1絶縁膜サイドウォール5bと、ゲート電極105を挟んで形成されたソース領域108S及びドレイン領域108Dにおいて、側面が第1絶縁膜サイドウォール5bに接して半導体基板1上面に形成されたシリコン層109と、第1絶縁膜サイドウォール5bを介してゲート電極105側面と対向し、底面がシリコン層109上面に接して形成された第2絶縁膜サイドウォール5dと、シリコン層109内下層部に設けられたLDD不純物層109aと、シリコン層109内上層部に設けられた高濃度不純物層109bと、LDD不純物層109aの下方、半導体基板1の表面側に形成されたポケット不純物層108aとを具備する。

(もっと読む)

第2のコントロールゲートを絶縁層の下に埋め込んだSeOIDRAMメモリセルをコントロールする方法

【課題】DRAMメモリセルでより小型のトランジスタを使用できる方法を提供する。

【解決手段】ゲート誘電体7によってチャネルから分離されているフロント・コントロール・ゲート8、およびベース基板に配置され、かつ絶縁層(BOX)によってチャネル4から分離されているバック・コントロール・ゲート9と、を有するトランジスタからなるDRAMメモリセルコントロール方法において、セルプログラミング動作において、フロント・コントロール・ゲートおよびバック・コントロール・ゲートが、第1の電圧をフロント・コントロール・ゲートに、第2の電圧をバック・コントロール・ゲートに印加することによって共に使用され、第1の電圧の大きさは、バック・コントロール・ゲートに電圧が印加されない場合にセルをプログラミングするのに必要な電圧の大きさよりも小さい。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応した大容量のキャパシタ素子を形成する。

【解決手段】(1)半導体基板に電気的に接続されたコンタクト上に形成された第1層間絶縁膜15に、コンタクト上面を露出する第1のシリンダ開孔を形成し、第1のシリンダ開孔内にコンタクトに接続されるシリンダ形状の第1下部電極18を形成する工程、(2)第1層間絶縁膜15上に、第1下部電極で囲まれた空間を全て埋め込むことなく第2層間絶縁膜19を形成した後、第1下部電極で囲まれた空間の開口部を全て露出する位置に第1下部電極の内壁面を露出するように、第2の層間絶縁膜に第2のシリンダ開孔を形成する工程、(3)第1下部電極18の内壁から第2のシリンダ開孔内壁に連続して、少なくとも第2のシリンダ開孔内でシリンダ形状を有する第2下部電極22を形成する工程、とを有する。

(もっと読む)

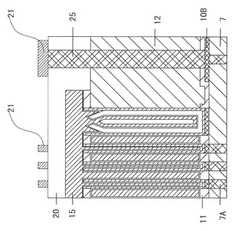

半導体装置の製造方法

【課題】RC型トランジスタのチャネル領域の高さを所望の範囲に調整するとともに、前記チャネル領域に近接して残存する薄皮状のバリ部を完全に除去して、半導体装置を製造するという課題があった。

【解決手段】半導体基板1の一面に、溝部と、溝部に囲まれ、側壁面の少なくとも一部が傾斜面である凸部39とを形成してから、溝部を埋める素子分離用絶縁膜を形成する第1工程と、素子分離用絶縁膜をマスクの一部にして半導体基板1の一面をドライエッチングして凸部39内に凹部27を設けるとともに、凹部27と素子分離用絶縁膜との間にチャネル領域4となる薄肉部41を形成する第2工程と、ウェットエッチングにより、薄肉部41の高さを調整する第3工程と、を有する半導体装置の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体素子及びその形成方法

【課題】格納電極コンタクトおよび格納電極の形成方法を提供する。

【解決手段】半導体素子は、活性領域104上に備えられる多数の導電プラグ116と、前記多数の導電プラグ116のうち、前記活性領域104の中央部に位置する導電プラグ116に接続され、前記活性領域104の上部を通るビットライン123と、前記多数の導電プラグ116のうち、前記活性領域104の両端部に位置する導電プラグ116と接続する格納電極130とを含み、ビットライン123が活性領域104の上部に形成されることにより、活性領域104とビットライン123を電気的に連結させるビットラインコンタクトを別に形成せずとも良く、格納電極130はランディングプラグと直接接続するので、格納電極コンタクトを別に形成せずとも良い。

(もっと読む)

半導体装置及びその製造方法

【課題】金属酸化膜と下部電極との間に発生する剥がれを防止して、キャパシタのリーク電流を低減する。電気特性に優れ、信頼性の高い半導体装置を提供する。

【解決手段】順に設けられた、下部電極と、密着層と、容量絶縁膜と、上部電極とを有するキャパシタを備えた半導体装置。容量絶縁膜は、第1の金属酸化膜が密着層に接するように、第1の金属酸化膜と第2の金属酸化膜を交互に積層した構造を備える。密着層は、膜厚が0.3nm以上で下部電極の構成元素の少なくとも一部を含有する酸化膜である。

(もっと読む)

絶縁膜およびその製造方法、半導体装置、ならびにデータ処理システム

【課題】誘電率が大きく、電極間に挟んで用いてもリーク電流値の小さい絶縁膜を提供する。

【解決手段】結晶化した酸化ジルコニウムからなる酸化ジルコニウム膜の2つと、非晶質であって、前記結晶化した酸化ジルコニウムよりも大きい誘電率を有する材料からなる結晶粒界分断膜とを有し、前記結晶粒界分断膜が、前記2つの酸化ジルコニウム膜に挟まれている絶縁膜を形成する。例えば、上部電極と下部電極の間に容量絶縁膜を有するキャパシタ素子で構成されたメモリセルを備える半導体装置における容量絶縁膜や、コントロールゲート電極とフローティングゲート電極の間にインターゲート絶縁膜を有する不揮発性メモリ素子を備えた半導体装置におけるインターゲート絶縁膜として好適である。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチゲート型FIN−FETにおいて、微細化に対してもFIN型トランジスタの利点を十分に発揮し、また、活性領域において十分なコンタクト面積を確保し、オン電流の低下を抑制したトレンチゲート型FIN−FETを提供する。

【解決手段】チャネル領域のFIN幅(162)を活性領域の幅(161)よりも狭くする。

(もっと読む)

半導体装置およびその製造方法

【課題】電極の支持部にクラックが発生し、電極の保持強度が低下して、電極の側壁を露出させる湿式エッチング工程において、電極の倒壊をさせるという課題があった。

【解決手段】半導体基板1上に立設する複数の電極13と、電極13の立設を保持する支持部14Sと、を備え、支持部14Sが、圧縮応力を有する第1の支持膜14aと引張応力を有する第2の支持膜14bとが積層されてなる積層膜14である半導体装置を用いることにより、上記課題を解決できる。

(もっと読む)

半導体基板、半導体装置及び半導体装置の製造方法

【課題】半導体層の界面に生じるダングリングボンドをフッ素で終端することで、界面準位を低減することができ、また、低熱履歴のプロセスでも活性領域のみへ効率よくフッ素を導入することができる半導体基板を提供する。

【解決手段】フッ素拡散防止膜6と該フッ素拡散防止膜6上に形成されたフッ素を含有するシリコン酸化膜7からなる絶縁層9と、前記絶縁層9上に形成された半導体層8と、を含み、前記半導体層8とフッ素を含有する前記シリコン酸化膜7とが接触していることを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】電極とキャパシタ用絶縁膜(金属酸化膜)との間に発生する気泡状の剥がれの発生を防止することができる半導体装置およびその製造方法を提供する。

【解決手段】基体上にソースガスを供給S1して、ALD法により金属窒化膜を3nm以下の膜厚で堆積S2,S3,S4し、金属窒化膜を酸化S5,S6して金属酸化膜を形成する工程を複数回繰り返して、基体上に、金属酸化膜からなる積層膜を形成する。これにより電極とキャパシタ用絶縁膜(金属酸化膜)との間に発生する気泡状の剥がれを防止することができる。

(もっと読む)

半導体装置の製造方法

【課題】スタックされるプラグ同士の接続を良好に行う。

【解決手段】半導体基板上に第1の層間絶縁膜を形成し、第1の層間絶縁膜に第1のホールを形成し、第1のホール内にバリア膜を形成し、第1のホール内に導電材を充填して第1のプラグを形成し、第1の層間絶縁膜上に第2の層間絶縁膜を形成し、第2の層間絶縁膜に第1のプラグに達する第2のホールを形成し、第2のホール内で前記バリア膜上端部を選択エッチングし、第2のホール内に、第1のプラグに接続する第2のプラグを形成する、半導体装置の製造方法。

(もっと読む)

半導体記憶装置

【課題】静電容量の大きなキャパシタを備え、低コストで製造が可能な、高集積化された半導体記憶装置を提供する。

【解決手段】半導体基板上にY方向に延在しY方向と垂直なX方向に互いに平行に配列されたワード線と、Y方向に互いに平行に配列され二つのワード線と交差する帯状の活性領域と、各活性領域上のその長手方向の両端部にそれぞれ接続する容量コンタクトプラグと、容量コンタクトプラグ上の第1下部電極と第1下部電極上の第2下部電極を含むスタック下部電極と、容量絶縁膜と、上部電極とを有し、第2下部電極の中心位置が第1下部電極の中心位置から所定の方向へシフトしている、半導体記憶装置。

(もっと読む)

101 - 120 / 266

[ Back to top ]