Fターム[5F083AD04]の内容

半導体メモリ (164,393) | DRAM (5,853) | 読出しトランジスタ (1,433) | 水平方向以外のチャネルを有するもの (541) | トレンチゲートトランジスタ(単孔にゲートを埋込むもの) (266)

Fターム[5F083AD04]に分類される特許

61 - 80 / 266

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】Y方向に延在するように半導体基板13に設けられ、底面18c及び対向する第1及び第2の側面18a,18bを有するゲート電極用溝18と、ゲート絶縁膜21を介して、ゲート電極用溝18の下部を埋め込むように配置されたゲート電極22と、ゲート電極用溝18を埋め込むように配置され、ゲート電極22の上面22aを覆う埋め込み絶縁膜24と、第1の側面18aに配置されたゲート絶縁膜21の上部21Aを覆うように、半導体基板13に設けられた第1の不純物拡散領域28と、少なくとも第2の側面18bに配置されたゲート絶縁膜21を覆うように、半導体基板13に設けられた第2の不純物拡散領域29と、を有する。

(もっと読む)

半導体記憶装置の製造方法

【課題】立体構造を有する電極などの部材上に、組成の同じALD膜を形成することの可能な半導体記憶装置の製造方法を提供する。

【解決手段】半導体基板上に、下部電極、上部電極、および下部電極と上部電極に挟まれる容量絶縁膜からなるキャパシタを有する半導体記憶装置の製造方法において、前記下部電極の表面および前記層間絶縁膜の表面に、Alの前駆体とZrの前駆体の前記下部電極に対する各々の被覆特性が一致する条件で、前記Alの前駆体と前記Zrの前駆体を反応室内に供給する工程と、前記Alの前駆体と前記Zrの前駆体を反応室から真空排気する第1の真空排気工程と、酸化剤を反応室に供給する工程と、前記酸化剤を前記反応室から真空排気する第2の真空排気工程と、繰り返すALDフローシーケンスによりZrAlO膜を形成する工程を採用する。

(もっと読む)

キャパシタ、キャパシタの製造方法および半導体装置

【課題】静電容量が大きく、リーク特性に優れたキャパシタを容易に形成する。これにより、データ保持特性にすぐれ、集積度の高いDRAM等の半導体装置を容易に形成する。

【解決手段】キャパシタの容量絶縁膜は、第1領域と第2領域を有する。第1領域は、Sr/Tiの原子組成比が1.2以上1.6以下の範囲であるチタン酸ストロンチウムからなる。第2領域は、Sr/Tiの原子組成比が0.8以上1.2未満の範囲であるチタン酸ストロンチウムからなる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極の幅を十分に確保して、ゲート電極の抵抗値を小さくすることが可能で、かつゲート電極間の容量を小さくすることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板に設けられ、Y方向に延在する第1の溝15と、半導体基板に設けられ、第1の溝15と交差するXの方向に延在する第2の溝25と、第1及び第2の溝15,25に囲まれ、第2の溝25に露出された対向する第1及び第2の側面26a,26bを有するピラー26と、ゲート絶縁膜28を介して、ピラー26の第2の側面26bに接触するように、第2の溝25の下部に設けられた1つのゲート電極29と、ゲート電極29の側面とピラーの第1の側面26aとの間に配置された空隙と、を有する。

(もっと読む)

半導体装置、半導体装置の製造方法およびデータ処理システム

【課題】本発明はコンタクト開口をエッチングにより形成した場合にその下に位置する埋込絶縁膜がエッチングされないようにした構造の提供を目的とする。

【解決手段】本発明は、半導体基板と、半導体基板の主面に形成され活性領域を横断して素子分離領域まで延在するトレンチと、トレンチの下部側に形成された埋込型ゲート電極と、活性領域において埋込型ゲート電極の上方のトレンチ内を充填し、かつ、素子分離領域において埋込型ゲート電極の上方のトレンチ内を完全には充填せずにトレンチの内側面に接して配置されるサイドウォールを構成するキャップ絶縁膜と、素子分離領域においてサイドウォールの内側のトレンチを埋めて埋込型ゲート電極に接続形成されたパッドコンタクトプラグと、パッドコンタクトプラグおよびキャップ絶縁膜上を覆う層間膜と、パッドコンタクトプラグに接続するゲートコンタクトプラグとを具備してなる。

(もっと読む)

半導体装置の製造方法

【課題】高アスペクト比のホール内に、良好なステップカバレッジを有する均一な膜厚の窒化シリコン層を形成する。

【解決手段】ホールを形成後、1回の第1サイクルと、1回以上の第2サイクルを行う。第1サイクルでは、ホールの上部内壁上に2原子層の第1のシリコン層、ホールの下部内壁上に1原子層の第1のシリコン層を形成後、ホール上部のシリコン層の表面を1分子層の第1の酸化シリコン層とする。ホールの下部内壁上の第1のシリコン層に更に、1原子層の第2のシリコン層を形成後、窒化処理によりホールの内壁全面に第1の窒化シリコン層を形成する。第2サイクルでは、ホール上部の窒化シリコン層上に1分子層の第2の酸化シリコン層を形成後、ホール下部の第1の窒化シリコン層上に1原子層の第4のシリコン層を形成する。この後、窒化処理により、ホールの内壁全面に第2の窒化シリコン層を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、トランジスタを容易にOn(オン)させることが可能で、かつ良好なデータ保持特性を実現することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板12に形成され、第1の方向に延在する第1の素子分離用51、及び第1の素子分離用溝51を埋め込む第1の素子分離用絶縁膜53よりなり、複数の素子形成領域Rを有した活性領域16を区画する第1の素子分離領域14と、半導体基板12に、第1の方向と交差する第2の方向(Y方向)に延在するように形成され、第1の素子分離領域14の一部を分断する第2の素子分離用溝54、及び第2の素子分離用溝54を埋め込む第2の素子分離用絶縁膜56よりなり、複数の素子形成領域Rを区画する第2の素子分離領域17と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

半導体装置の製造方法

【課題】本発明は半導体装置に関する。

【解決手段】本発明は、半導体基板上のセル領域のセルトランジスタ上の層間膜を貫通してコンタクトプラグが形成され、周辺回路領域のトランジスタ上の層間膜を貫通してコンタクトプラグが形成されてなる半導体装置の製造方法であり、セルトランジスタ上の層間膜にコンタクトホールを形成し、その底部側にシリコン膜の下部導電プラグを形成する工程と、その上に金属膜を積層して積層構造のセルコンタクトプラグを形成する工程と、周辺回路用トランジスタ上の層間膜にコンタクトホールを形成し、その内部に金属膜を形成してコンタクトプラグを形成する工程とを具備し、前記セル領域のコンタクトホール内のシリコン膜上に金属膜を形成する工程と前記周辺回路領域のコンタクトホール内に金属膜を形成する工程を同時に行うことを特徴とする。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】メモリセル領域に埋め込みゲート電極を有し、周辺回路領域にプレーナ型ゲート電極と貫通電極を有する半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板50のメモリセル領域の溝部内に第一のゲート絶縁膜を介して、ワード線を埋め込み形成する工程と、周辺回路領域の前記半導体基板50上に、第二のゲート絶縁膜を介して周辺ゲート電極を形成する工程と、前記半導体基板50の主面上に層間絶縁膜と金属膜とを形成したのちに、前記金属膜をパターニングして、前記メモリセル領域の容量コンタクトパッドと前記周辺回路領域の局所配線127とを同時に形成する工程と、前記局所配線127の下面127a側を露出する開口151を形成したのちに導電体を充填することにより貫通プラグを形成する工程と、を採用する。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】ワード線とコンタクトプラグとの短絡や、ワード線とビット配線との短絡を防ぐことが可能な半導体装置を提供する。

【解決手段】本発明の半導体装置100は、半導体基板50と、前記半導体基板50の表層に、形成された複数の活性領域Kと、前記活性領域Kの表層から深さ方向に形成された不純物拡散層22,24と、前記複数の活性領域Kを横切るように形成された複数の溝部7に、セルゲート絶縁膜7Aを介して前記半導体基板50の上面50aよりも下方に位置するように埋め込まれたワード9線と、前記ワード線9上を埋め込むように形成された窒化シリコンからなる埋込絶縁膜11と、前記不純物拡散層22,24に接続するビット配線と容量コンタクトプラグと、を具備し、前記ビット配線15と容量コンタクトプラグ19の少なくとも一方が、前記埋込絶縁膜11上の一部に重なるように配置されていることを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】トランジスタの電流駆動能力の低下を防止可能な半導体装置を提供する。

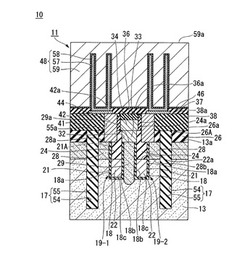

【解決手段】本発明の半導体装置10は、半導体基板1の表層に第一の方向に延在するように形成された複数の活性領域1aと、前記活性領域1aの表層から深さ方向に形成されたn型不純物拡散層15と、前記複数の活性領域1aを横切り第二の方向に延在するように形成された複数の埋め込みゲート用の溝部13a,bと、ゲート絶縁膜25a,bを介して前記活性領域1a上を跨ぐように前記埋め込みゲート用の溝部13a,bに埋め込まれたゲート電極31およびダミーゲート電極32とを構成すると共に、前記半導体基板1の面上において前記第二の方向に延在する複数のワード配線層と、を具備し、前記ダミーゲート電極32の上面32cが、前記n型不純物拡散層15と前記活性領域1aとの界面よりも下方に位置していることを特徴とする。

(もっと読む)

半導体装置

【課題】半導体装置の省スペース化を実現する。

【解決手段】半導体基板5に、センスアンプが備えられた周辺回路領域Sとメモリセル領域Mとが区画形成され、メモリセル領域Mにおいて、半導体基板5の一面に形成されたトレンチ溝内に、ゲート絶縁膜を介しゲート電極を含む埋込ワード線9とその上に位置する埋込絶縁膜とが埋め込まれ、前記トレンチ溝に隣接する半導体基板5一面の表面領域に不純物拡散層が形成され、前記不純物拡散層が形成された領域上にはビット配線15が形成されており、ビット配線15が周辺回路領域Sまで延長され、周辺回路領域Sにおいてビット配線15が前記センスアンプを構成するMOSトランジスタのゲート電極Gとされていることを特徴とする半導体装置を採用する。

(もっと読む)

半導体装置およびその製造方法

【課題】活性領域をライン上に形成することで、コンタクト領域のばらつきを抑制し、リセスゲート電極を用いて隣接するトランジスタ間の分離を行う構造を提供する。

【解決手段】半導体基板中に第1の方向に延在して形成される素子分離領域で分離された活性領域と、第1の方向と交差する第2の方向に延在し、素子分離領域及び活性領域に連通する溝内に形成されたリセスゲート電極と。リセスゲート電極で分断された活性領域であって、リセスゲート電極の底面より浅い領域に形成されるMOSトランジスタのソース/ドレイン領域とを備えた半導体装置であって、リセスゲート電極は、MOSトランジスタのゲート電極を構成する制御ゲート電極162tと、第1の方向に隣接するMOSトランジスタを素子分離する補助ゲート電極162iで構成される。

(もっと読む)

半導体装置の製造方法

【課題】容量コンタクトパッドと容量コンタクトプラグが一体となった構造を形成する。これにより、従来は2回、必要だったフォトリソグラフィ工程を1回に削減して、製造コストを低減する。

【解決手段】半導体装置の製造方法では、層間絶縁膜上に、開口を有するマスクパターンを形成する。このマスクパターンを用いて、層間絶縁膜をエッチングすることにより、開口の下の層間絶縁膜内に容量コンタクトホールを形成する。湿式エッチングにより、マスクパターン内の開口を大きくした後、開口内に導電材料を埋め込むことにより、それぞれ容量コンタクトプラグ及び容量コンタクトパッドを形成する。この後、容量コンタクトパッド上にキャパシタを形成する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜の形成を1000℃以上で行う場合に、Grow−in欠陥の発生の抑制と、BMDを用いたゲッタリング効果の向上を両立させる。

【解決手段】初期状態での酸素濃度が5×1017atoms/cm3以下の半導体基板に素子分離領域3を形成し、ゲート絶縁膜5aを1000℃以上の熱酸化により形成した後、酸素をイオン注入して熱処理することで、BMD層30を素子分離領域3の底面よりも下方に形成する。

(もっと読む)

キャパシタの製造方法および半導体装置の製造方法

【課題】高温相の結晶構造の容量絶縁膜を電極上に直接形成可能なキャパシタの製造方法を提供する。

【解決手段】本発明のキャパシタCapの製造方法は、第一の電極3を形成する工程と、成膜温度が低い順に、非晶質相、低温相の結晶構造、高温相の結晶構造を形成し得る金属酸化物の形成工程であって、前記第一の電極3上に、前記低温相の結晶構造の成膜温度よりも低い第一の温度で前記非晶質相からなる前記金属酸化物を形成する工程と、前記第一の温度から、前記高温相の結晶構造の成膜温度である第二の温度まで、10℃/秒以上の昇温速度で昇温し、前記第二の温度で前記金属酸化物をアニールすることにより、前記金属酸化物に前記高温相の結晶構造を析出させて容量絶縁膜4とする工程と、前記容量絶縁膜4上に第二の電極5を形成する工程を採用する。

(もっと読む)

半導体装置の製造方法

【課題】隣接する活性領域の間で電気的な短絡(ショート)が発生することを防止した半導体装置の製造方法を提供する。

【解決手段】ゲート電極6aを挟んだ両側の活性領域5上にシリコン膜12を選択的にエピタキシャル成長させる工程と、複数のワード配線層WLの各間に反射防止膜を埋め込んで平坦化した後、この平坦化した面上に、互いに隣接する活性領域5の各間において第1の方向Xに延在する開口部を有するマスクパターンを形成する工程と、マスクパターンの開口部から露出した部分を半導体基板の表面が露出するまでドライエッチングにより除去する工程とを含む。これにより、互いに隣接する活性領域5の間でシリコン膜12が横方向にエピタキシャル成長することによって連結された部分を、ドライエッチングにより切断し除去することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】フィールドシールド用トランジスタのゲート長を、背景技術と比べて長く取れるようにする。

【解決手段】半導体装置1は、底面並びに第1及び第2の側面を有するセル用ゲートトレンチ10と、トレンチ10より幅の狭いフィールドシールド用ゲートトレンチ11と、トレンチ10とトレンチ11の間に設けられた上部拡散層と、トレンチ10を挟んで第1の上部拡散層の反対側に設けられた第2の上部拡散層と、トレンチ11を挟んで第1の上部拡散層の反対側に設けられた第3の上部拡散層と、トレンチ10の底面に設けられた下部拡散層と、それぞれ第1及び第2の上部拡散層と電気的に接続された第1及び第2の記憶素子と、下部拡散層と電気的に接続されたビット線BLと、ゲート絶縁膜を介して第1及び第2の側面をそれぞれ覆うワード線WLと、ゲート絶縁膜を介してトレンチ11に埋め込まれたフィールドシールド用ゲート電極DWLとを備える。

(もっと読む)

DRAMアクセス・トランジスタ及び形成方法

【課題】自己整列リセス・ゲート構造及び形成方法の提供。

【解決手段】最初に,絶縁用のフィールド酸化物領域20を半導体基板10内に形成する。半導体基板の上に形成された絶縁層内に複数のコラムを画定し,それに続いて,薄い犠牲酸化物層を半導体基板の露出領域の上に形成するが,フィールド酸化物領域の上には形成しない。次に,各コラムの側壁上,並びに犠牲酸化物層及びフィールド酸化物領域の一部分の上に誘電体を設ける。第1エッチングを行い,それにより,半導体基板内に第1組のトレンチを,またフィールド酸化物領域内に複数のリセスを形成する。第2エッチングを行い,それにより,コラムの側壁上に残っている誘電体残留部を除去し,かつ第2組のトレンチを形成する。次に,第2組のトレンチ内及びリセス内にポリシリコンを堆積させ,それにより,リセス導電性ゲートを形成する。

(もっと読む)

61 - 80 / 266

[ Back to top ]