Fターム[5F083AD04]の内容

半導体メモリ (164,393) | DRAM (5,853) | 読出しトランジスタ (1,433) | 水平方向以外のチャネルを有するもの (541) | トレンチゲートトランジスタ(単孔にゲートを埋込むもの) (266)

Fターム[5F083AD04]に分類される特許

141 - 160 / 266

半導体装置及び半導体装置の製造方法

【課題】閾値電圧が制御されて、且つ特性のばらつきが抑制された半導体装置を提供する。

【解決手段】基板2と、STI素子分離領域3と、活性領域4と、活性領域4に形成された第1ゲートトレンチ5と、第1ゲートトレンチ5の底部に設けられた第2ゲートトレンチ6と、第1及び第2ゲートトレンチ5,6にゲート絶縁膜7を介して埋め込み形成されたゲート電極8と、第1ゲートトレンチ5の幅方向両側の活性領域4にイオンを注入することによって形成されたソース/ドレイン領域9とを備え、第2ゲートトレンチ6と第2ゲートトレンチ6の長手方向に位置するSTI素子分離領域3との間に、チャネルを構成するシリコン薄膜部10が設けられていることを特徴とする半導体装置1。

(もっと読む)

窪み付きゲート構造を有するメモリデバイス及びその製造方法

【課題】本発明は、IC(integrated circuit)の集積度が向上し、しかもショートチャネル効果を防止することができるMOS半導体デバイスを形成する方法を提供する。

【解決手段】DRAMアクセストランジスタのようなメモリデバイスであって、窪み付きゲート構造を有するメモリデバイスを形成する方法が開示されている。まず、絶縁用のフィールド酸化物領域(21)が半導体基板上に形成され、ついで、窒化シリコン層(18)にパターン形成が行われ、エッチングによりトランジスタトレンチ(22)が得られる。その後にデポジットされたポリシリコンであって、ゲート構造形成のためのポリシリコンを、隣接し隆起した窒化シリコン構造に対して研磨できるようにするため、このトランジスタトレンチに隣接するフィールド酸化物領域に窪みが設けられる。

(もっと読む)

半導体装置およびその製造方法

【課題】同じ導電型を有するトランジスタであっても、用途に応じて特性を好ましいものにする。

【解決手段】半導体装置100は、半導体基板102上に形成された同じ導電型を有する第1のトランジスタ210および第2のトランジスタ212を含む。第1のトランジスタ210は、ゲート絶縁膜としてHf含有ゲート絶縁膜106を含み、第2のトランジスタ212は、ゲート絶縁膜としてシリコン酸化膜124を含むとともにHf含有膜を含まない。

(もっと読む)

半導体装置及びその製造方法、並びに、データ処理システム

【課題】異なる特性を有するリセスチャネル型のトランジスタを同一工程で同時に形成する。

【解決手段】ハードマスク71〜73を用いて半導体基板2をエッチングし、ハードマスク71〜73の側面にサイドウォール絶縁膜38を形成し、ハードマスク71,72の側面に形成されたサイドウォール絶縁膜38を選択的に除去し、ハードマスク71〜73とサイドウォール絶縁膜38を用いて半導体基板2をさらにエッチングし、ハードマスク71〜73に覆われていた半導体基板2の一部にそれぞれゲートトレンチ12,22,32を同時に形成する工程と、ゲートトレンチ12,22,32の内部にゲート電極13,23,33を形成する工程と備える。これにより、フィン状領域21f,31fの高さが異なる複数のリセスチャネル型トランジスタを同時に形成することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ビットコンタクトと容量コンタクトとの接触を防止する。

【解決手段】拡散層領域121,122を有するトランジスタ111と、層間絶縁膜151に埋め込まれ、それぞれ拡散層領域121,122に接続されたセルコンタクト131,141と、層間絶縁膜152に埋め込まれ、セルコンタクト131に接続されたビットコンタクト132と、層間絶縁膜153に埋め込まれ、ビットコンタクトと接続されたビット線130と、層間絶縁膜152,153に埋め込まれ、セルコンタクト141と接続された容量コンタクト142とを備える。ビット線130の側面130aは、ビット線130の延在方向に沿ったビットコンタクト132の側面132aと一致している。これにより、ビットコンタクトと容量コンタクトが直接短絡することがなくなるため、容量コンタクトの形成マージンが拡大する。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造を有するRC型トランジスタにおいて、しきい値電圧の低下を防止でき、さらに、しきい値電圧の制御や調整が容易にできる。

【解決手段】電界効果トランジスタを備えた半導体装置であって、電界効果トランジスタは、半導体基板1に形成された素子分離領域3によって仕切られた拡散層領域と、

その拡散層領域と交差するように設けられ、少なくとも一部が半導体基板1に形成されたゲート溝内に埋め込まれたゲート電極5と、拡散層領域内において、一方の側面がゲート電極5のうちゲート溝内に埋め込まれた部分と対向し、他方の側面が素子分離領域3の側面と接触するように形成されたSOI構造のチャネル層4とを有し、ソース・ドレイン領域として機能する不純物拡散層5がチャネル層4よりも上部に配置され、不純物拡散層5とチャネル層4とが離間して形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ型キャパシタと接続する拡散層ソースの幅のばらつきを抑制する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板11表面に垂直に形成されたキャパシタ用トレンチ12の半導体基板11表面側に形成されたn型の埋め込み多結晶シリコン19と、半導体基板11に埋め込まれて溝状をなし、埋め込み多結晶シリコン19を被う素子分離領域25の曲面22に連接する側面とほぼ面一な垂直面を内側表面とするゲート絶縁膜31と、底面及び底面側の対向する両側面をゲート絶縁膜31と接する埋め込み型のゲート電極40と、埋め込み多結晶シリコン19とゲート絶縁膜31との間及び下方にあり、n型の不純物を有する半導体基板11に形成された埋め込み拡散層47と、埋め込み拡散層47と対向する側にあり、ゲート絶縁膜31の側面に接し、半導体基板11の表面から内側にn型の不純物を有する表面拡散層45とを有する。

(もっと読む)

半導体装置の製造方法及び半導体製造装置

【課題】シリコンエピタキシャル層と配線材料との間でショートが発生しない半導体装置の製造方法、コンタクトプラグの形成においてコンタクトホールの径の拡大を抑制する半導体装置の製造方法、これらの目的を効果的に達成できる半導体製造装置を提供する。

【解決手段】シリコン表面に形成された第1の酸化シリコン膜2と、第1の酸化シリコン膜2とは形成方法の異なる第2の酸化シリコン膜3とを有し、各々の酸化シリコン膜2,3の少なくとも一部が露出して共存するシリコン基板1を前処理する前処理工程を備えた半導体装置の製造方法であって、前記前処理工程は、第1の酸化シリコン膜2を除去して前記シリコン表面を露出させるエッチング工程を有し、前記エッチング工程は、第1の酸化シリコン膜2と第2の酸化シリコン膜3とを同じエッチングレートでエッチングすることを特徴とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】半導体装置の製造安定性を向上させる。

【解決手段】半導体装置100においては、シリコン基板101にメモリ領域とロジック領域が混載されている。メモリ領域においてシリコン基板101に溝部111が設けられ、メモリ領域にメモリセルトランジスタ120が設けられるとともにロジック領域にロジックトランジスタ130が設けられる。メモリセルトランジスタ120は金属材料により構成された第一ゲート電極115を含む。第一ゲート電極115は溝部111に埋設されるとともに溝部111の外部に突出して設けられる。ロジックトランジスタ130は第一ゲート電極115と同一材料により構成された第二ゲート電極127を含む。

(もっと読む)

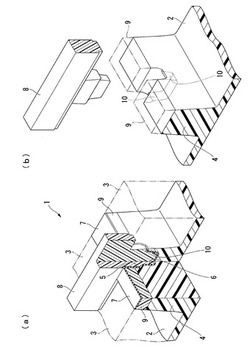

半導体装置及び半導体装置の製造方法

【課題】動作特性の制御が容易で微細化に有利なトランジスタを有する半導体装置およびその製造方法を提供する。

【解決手段】活性領域K内に設けられたトレンチ100と、トレンチ100と素子分離領域Sとの間の活性領域Kに形成されたフィン型チャネル領域185と、トレンチ100に埋設され、ゲート絶縁膜191を介してフィン型チャネル185と接するゲート電極225と、フィン型チャネル185と接続され、活性領域K内においてゲート電極225を挟んでトレンチ100の両側に位置するソース/ドレイン拡散領域241と、を具備してなり、ソース/ドレイン拡散領域241と半導体基板101の接合部241aは、フィン型チャネル領域185の最下端部185aより深い位置にあることを特徴とする。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】DRAMセルのキャパシタに適用できる膜厚まで薄膜化しても、高い誘電率を得るのに十分な結晶性を確保する誘電体膜を提供する。

【解決手段】トランジスタとワード線3、ビット線6がシリコン基板1上に形成されており、そのトランジスタの拡散層15の片側から、ポリシリコンで形成された導電性プラグ5が引き出されている。その上部に、さらに第2の導電性プラグ8が接続されており、これは反応バリア層9を介して円筒型のキャパシタ下部電極10につながっている。下部電極10の表面には、ニッケルまたはコバルトを0.5%から10%の範囲で添加した二酸化チタン11が形成されており、上部電極12と下部電極10、および二酸化チタン11でキャパシタが構成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法並びにデータ処理システム

【課題】動作特性の制御が容易で微細化に有利なトランジスタを有する半導体装置およびその製造方法並びにデータ処理システムを提供する。

【解決手段】活性領域K内に設けられたトレンチ100と、トレンチ100と第1素子分離領域S1との間の活性領域Kに形成されたフィン型チャネル領域185と、第1素子分離領域S1に埋設され、第1ゲート絶縁膜141を介してフィン型チャネル185と接する第1ゲート電極151と、トレンチ100に埋設され、第2ゲート絶縁膜191を介してフィン型チャネル185と接する第2ゲート電極225と、フィン型チャネル185と接続され、活性領域K内において第2ゲート電極225を挟んでトレンチ100の両側に位置するソース/ドレイン拡散領域241とを具備してなるトレンチゲート型MOSトランジスタTrを有する半導体装置1を採用する。

(もっと読む)

半導体装置及びその製造方法

【課題】改良された縦型のMOSトランジスタを備える半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板10の主面に対してほぼ垂直に延在するチャネル領域22と、チャネル領域22の下部に設けられた第1の拡散層領域22aと、チャネル領域の上部に設けられた第2の拡散層領域22bと、半導体基板10の主面に対してほぼ垂直に延在し、ゲート絶縁膜30を介してチャネル領域22の側面に設けられた第1のゲート電極34と、半導体基板10の主面とほぼ平行に延在し、第1のゲート電極34の上部に接続された第2のゲート電極35aと、第1の拡散層領域22aに接続され、第2のゲート電極と交差する埋め込み配線21を備えている。第2のゲート電極35aの平面的な位置は、第1のゲート電極34の平面的な位置に対してオフセットされている。

(もっと読む)

半導体装置及びその製造方法

【課題】深さに応じて素子分離領域の断面積を自由に制御すると共に、微細化や多様な装置設計に効果的に対応可能とする。RC型トランジスタの活性領域中に含まれる凹部の側部の形状ばらつきを抑制する。また、この凹部の側部をトランジスタのチャネル領域として使用することにより、トランジスタの特性ばらつきを防止する。

【解決手段】深さ方向に垂直な段差面を有する段差構造を有し、上部素子分離領域と、下部素子分離領域とを有する素子分離領域。また、この素子分離領域によって囲まれたRC型トランジスタ。

(もっと読む)

半導体素子のリセスゲート及びその製造方法

【課題】リセスゲート及びこれを含む半導体素子の製造方法を提供する。

【解決手段】半導体素子のリセスゲートは、基板110と、金属層165と、ポリシリコン層と、ポリシリコン層に隣接し、金属層165から離隔され、形成されたソース領域及びドレーン領域と、を含む。半導体素子の形成方法は、基板110の上にソース/ドレーン120層を形成する段階と、リセス112を形成し、第1導電層パターン145を形成する段階と、第1導電層パターン145上に第2導電層を形成する段階、ソース/ドレーン層120と重畳されるように第2導電層パターン156を形成する段階と、前記第2導電層パターン156と、前記ソース/ドレーン層120上に絶縁層を蒸着する段階と、第2導電層パターン156上にキャップを形成するように絶縁層を平坦化する段階と、を含む。

(もっと読む)

半導体装置、及びその製造方法

【課題】リソグラフィー工程を削減して、製造コストを約4%、削減する。リセス部に対してソース/ドレイン領域を自己整合的に形成して、トランジスタのVt(閾値電圧)、Ion(オン電流)等の特性バラツキを低減する。

【解決手段】(1)第1マスクを設ける工程と、(2)第1マスクをマスクに用いて不純物を注入することにより不純物拡散領域を形成する工程と、(3)全面に第2マスクを堆積させる工程と、(4)エッチバックを行って第2マスクを残留させると共に、不純物拡散領域の一部を露出させる工程と、(5)第1及び第2マスクをマスクに用いてエッチングを行い、半導体基板内に溝部を形成する工程と、(6)第1及び第2マスクをマスクに用いて、溝部内に不純物を注入する工程と、(7)ゲート絶縁膜を形成する工程と、(8)ゲート電極を形成する工程と、を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】工程数を削減しながらも、所望の不純物プロファイルおよびデバイス特性が得られる半導体装置の製造方法を提供する。

【解決手段】半導体基板1に溝6を形成する工程と、溝6の内部にゲート絶縁膜7を形成した後、溝6にゲート電極12を形成する工程と、半導体基板1およびゲート電極12を覆うように絶縁膜15を形成するとともに、ゲート電極12の幅方向両側に位置する絶縁膜15にセルコンタクト孔16を形成する工程と、セルコンタクト孔16を介して第1の不純物を半導体基板1に注入し、ゲート電極12の両側に前記第1の不純物を拡散させることによりソース・ドレイン拡散層13を形成する工程と、セルコンタクト孔16を介して第2の不純物を半導体基板1に注入し、溝6の底部6aおよび底部近傍の側面6bに前記第2の不純物を拡散させてチャネルドープ層9を形成する工程とを順に具備してなる。

(もっと読む)

半導体装置の製造方法

【課題】溝の形状を維持しながらバリを除去するとともに、溝内壁におけるシリコン表面のダメージを除去することが可能な半導体装置の製造方法、及び該製造方法によって製造された半導体装置を提供する。

【解決手段】基板1に埋設領域Mを形成して素子分離を行なう工程と、基板1に溝7a,7b,7cのパターンを形成する工程と、溝7a,7b,7c内壁に保護膜8を形成する工程と、異方性の強い条件でエッチバックすることにより、溝7a,7b,7cのゲート垂直方向側壁7dの一部に保護膜8を残しながら、溝7a,7b,7cのゲート平行方向内壁7eの保護膜8を除去する工程と、保護膜8の除去によってシリコンが露出した領域に水素ベーク処理を行って、溝7a,7b,7cのパターン形成の際に副生されたバリ1a,1aを除去する工程と、を少なくとも有することを特徴とする。

(もっと読む)

集積回路の製造方法

【課題】異なる基材領域又はいくつかのトレンチの底部及び各側壁部を覆う異なる酸化被膜の形成に異なる酸化処理を備える、集積回路を製造する方法を提供する。

【解決手段】表面を有する半導体基板10を準備するステップと、少なくとも一つの注入種が、前記表面の第二の部分区域14と比較すると前記表面の第一の部分区域12に近接して特に注入されるようなイオン注入処理を実行するステップと、前記表面の前記第一の部分区域を覆う第一の膜厚を有する第一の酸化被膜32と前記表面の前記第二の部分区域を覆う第二の膜厚を有する第二の酸化被膜36とを形成するように、単一の酸化処理を実行するステップであって、前記第一の膜厚が前記第二の膜厚と異なるステップと、を備える。

(もっと読む)

DRAM素子

【課題】DRAM周辺回路の低電圧P+ゲートMOSトランジスタ素子の性能と、高電圧N+ゲートMOSトランジスタ素子のゲート酸化膜の信頼性とを兼ね備えたNMOSトランジスタ素子を提供する。

【解決手段】DRAM素子は、第一リセスゲートが設けられたメモリアレイ領域、及び第二リセスゲートが設けられた周辺回路領域を有しており、前記第一リセスゲート及び第二リセスゲートがはめ込まれている半導体基板と、前記第一リセスゲートと前記半導体基板との間に設けられた、均一な厚さの第一ゲート酸化膜と、前記第二リセスゲートと前記半導体基板との間に設けられた、不均一な厚さの第二ゲート酸化膜とを含む。

(もっと読む)

141 - 160 / 266

[ Back to top ]