Fターム[5F083BS46]の内容

Fターム[5F083BS46]の下位に属するFターム

転送トランジスタと駆動トランジスタの接続 (57)

駆動トランジスタと負荷素子との接続配線 (117)

Fターム[5F083BS46]に分類される特許

41 - 60 / 74

半導体記憶装置および半導体集積回路装置

【課題】SRAMセルのダイナミックスタビリティを考慮して、メモリセルの安定性をさらに増大させる。

【解決手段】フラッシュメモリセルのフローティングゲート(FG)およびコントロールゲート(CG)を製造する工程を利用して、容量素子(C1,C2)を、記憶ノード(SN,/SN)に接続する。すなわち、SRAMセルの負荷トランジスタ(PT1,PT2)およびドライバトランジスタ(NT1,NT2)のゲート電極を、フローティングゲートと同一層の配線で形成し、コントロールゲートと同一の配線層の配線を、負荷およびドライバトランジスタのゲート電極と整列して配置するキャパシタ電極として形成する。

(もっと読む)

半導体装置

【課題】SRAMセルに必要な配線層を減らすことができる半導体装置及びその設計方法を提供すること。

【解決手段】半導体装置は、ビットライン22が容量素子31より下方にあるスタック型の構成を有するDRAMとSRAMとが混載されてなる。そして、SRAMのノード間接続24は、DRAMの容量下部電極32が形成される層以下であって、ビットライン22が形成される層以上の層の、例えば容量コンタクト23と同じ層に形成されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】セル面積の縮小化とともに、シェアードコンタクト形成時のゲート電極側部に形成されたサイドウォールの膜減りによる半導体基板への突き抜けを防止する。

【解決手段】半導体基板上にゲート絶縁膜を介してゲート電極13が形成され、その両側にサイドウォール15,16が形成され、ゲート電極13両側の半導体基板にソース・ドレイン17,18が形成されている半導体基板上に、ゲート電極13、ソース・ドレイン17,18等を被覆する犠牲膜23を形成する工程と、犠牲膜23にゲート電極13上から一方側のソース・ドレイン18上を開口するシェアードコンタクト24を形成する工程と、シェアードコンタクト24の内部にゲート電極13と一方側のソース・ドレイン18に接続する導電性プラグ26を形成する工程と、犠牲膜23を除去する工程とを備えたことを特徴とする。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】電流駆動能力を向上させ、リーク電流を防止する半導体記憶装置とその製造方法を提供する。

【解決手段】第1Nチャネルトランジスタと第1Pチャネルトランジスタを構成する第1ゲート電極が延伸して第2P型ソースドレインに接続され、第2Nチャネルトランジスタと第2Pチャネルトランジスタを構成する第2ゲート電極が延伸して第1P型ソースドレインに接続され、第2P型ソースドレインと接続される領域の第1ゲート電極の上面と第2P型ソースドレインの表面との段差は、第1Nチャネルトランジスタにおける第1ゲート電極の上面と第1N型ソースドレインの表面との段差よりも低く、第1P型ソースドレインと接続される領域の第2ゲート電極の上面と第1P型ソースドレインの表面との段差は、第2Nチャネルトランジスタにおける第2ゲート電極の上面と第2N型ソースドレインの表面との段差よりも低い。

(もっと読む)

半導体装置

【課題】nチャネルMISトランジスタとpチャネルMISトランジスタとが接続するドレイン領域において、トランジスタ特性を悪化させる不具合が生じないCMOSデバイスを含む半導体装置を提供する。

【解決手段】基板11上の半導体領域に形成されたソース領域18Aと、ドレイン領域17Aとを有するnチャネルMISトランジスタと、半導体領域に形成されたソース領域18Bと、ドレイン領域17Bと有するpチャネルMISトランジスタとを具備する。ドレイン領域17Aと17Bとが接続するように配置されると共に、同一の材料で形成され、ソース領域18A,18Bの少なくともいずれかがドレイン領域17A,17Bと異なる材料で形成されている。

(もっと読む)

半導体装置

【課題】MIM構造の容量素子の容量膜や下部電極のダメージを軽減することができる構造の半導体装置を提供する。

【解決手段】上部電極330と容量膜320との共通の端面Fから外側に下部電極310が突出している。その端面Fから外側の部分の上面に、容量膜320とは材料が相違する保護膜340が積層されている。端面Fから所定距離だけ内側の位置まで保護膜340が容量膜320と下部電極310との間に形成されている。従って、保護膜340により容量膜320の端面Fの近傍に段差が発生しており、上部電極330と容量膜320がエッチングされるときのダメージの進行が段差で抑制されている。さらに、下部電極310にダメージが発生することも保護膜340により防止されている。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を減少しつつ、2つの配線層間を電気的に接続すること。

【解決手段】2つの配線11C、11D間の下層部にて、数珠繋ぎ形状に形成されるとともに、2つの配線11C、11Dを電気的に接続するコンタクトプラグ9cを備える。2つの配線11C、11Dは、互いに離間して同一の層に形成されている。コンタクトプラグ9cは、配線4bに接続されるコンタクトプラグ9bと、ソース/ドレイン領域6に接続されるコンタクトプラグ9aと同時に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】エクステンション領域がゲート電極の下側に広がることがなく且つシェアードコンタクトを形成する際に接合リーク電流が発生するおそれがない半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板10における素子分離領域11に囲まれた部分に形成された活性領域12と、活性領域12の上に形成されたゲート絶縁膜21A及び第1のゲート電極膜22Aを有する第1のゲート構造23Aと、第1のゲート構造23Aの側面上に形成され、第1のゲート構造23Aよりも高さが低い第1のオフセットスペーサ24Aと、第1のゲート構造23Aの側面上に、第1のオフセットスペーサ24Aの側面及び上端面を覆うように形成された第1のサイドウォール25Aとを備えている。

(もっと読む)

半導体装置の製造方法及び半導体記憶装置

【課題】フィン状の構造を有するSRAM等を微細な構造にし、寸法的なばらつきを抑える半導体装置及びその半導体装置を容易に製造すること半導体装置の製造方法及び半導体記憶装置を提供する。

【解決手段】基板32を酸化して、その上にポリシリコン44を形成し、通常のゲート加工工程でポリシリコン44を微細なラインとし、その後、通常の工程どおりにサイドウォール46を形成する。この後、ポリシリコン44を除去し、サイドウォール46のみ残し、このサイドウォール46をマスクとして、矩形状の二本が対となる構造を形成し、次に、イオン注入をある角度をもって行うことで、二本のフィン39をそれぞれp/n−MOSトランジスタ35、39の1対を製造する。

(もっと読む)

半導体装置

【課題】バックゲート型のフィンFETを使いながらも十分なSNMを得ることのできるSRAMセルを有する半導体装置を提供する。

【解決手段】複数のフィンフィールドエフェクトトランジスタで構成され、前記複数のフィンフィールドエフェクトトランジスタの中の少なくとも1つの前記トランジスタが、第1ゲート電極と第2ゲート電極を持ち、前記第1ゲート電極の電位を制御してチャネルを形成し、前記第2ゲート電極の電位を制御してデータの書き込み時に閾値電圧を低下させるセパレートゲート型のダブルゲートフィールドエフェクトトランジスタであるSRAMセルを有する半導体装置による。

(もっと読む)

半導体記憶装置

【課題】 高機能の半導体記憶装置を高集積化を図りつつ少ない配線層で実現する。

【解決手段】 TCAM(Ternary Content Addressable Memory)セルアレイMA1は、検索データの1ビット分を入力する検索入力ノード(SL0)と、複数の記憶データに対してそれぞれ設けられ、検索データの1ビット分に対応するビットを入力する複数のデータ入力ノード(DI0A,DI0B)と、行列状に配列される複数のメモリセルMC0♯0〜3,MC1♯0〜3とを備える。複数のメモリセルの各々は、記憶データの1ビット分を記憶する第1のセルと、検索データと記憶データとが一致するか否かを演算する論理演算セルとをさらに含む。各メモリセルを構成するトランジスタのゲートは、行方向に沿って延在する。メモリアレイ形成領域の複数のウェルの各々は、列方向に隣接するメモリセルの対応するウェルと連続するように形成される。

(もっと読む)

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上部から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在するゲート絶縁膜と、前記半導体凸部に設けられたソース/ドレイン領域とを有するMIS型電界効果トランジスタ、このトランジスタを含む基体上に設けられた層間絶縁膜、及びこの層間絶縁膜に形成された埋め込み導体配線を有し、この埋め込み導体配線は、前記半導体凸部のソース/ドレイン領域と、前記層間絶縁膜下の他の導電部とに接続されていることを特徴とする半導体装置。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の配線方法

【課題】 負荷容量のアンバランスを軽減でき、さらには実装面積を削減できる半導体装置を提供する。

【解決手段】 半導体装置は、拡散領域A1と、ゲートG1と、拡散領域A2と、ゲートG2と、拡散領域A3とで2個のトランジスタを構成する第1回路1と、拡散領域B1と、ゲートG1と、拡散領域B2と、ゲートG2と、拡散領域B3とで2個のトランジスタを構成する第2回路2とを備える。拡散領域A1とB3、拡散領域A2とB2、拡散領域A3とB1とを接続、または拡散領域A1とA3とB2、拡散領域A2とB1とB3を接続して使用すると、製造過程で拡散層とゲートの位置関係がずれたとしても、負荷容量のアンバランスが生じることがない。

(もっと読む)

半導体記憶装置

【課題】 スタティック型半導体記憶装置においてメモリセル列単位で、ドライバトランジスタのソース電圧レベルを制御する。

【解決手段】 メモリセル(MC)内において、ドライバトランジスタソースコンタクト(DV1,DV2)を、内部の金属配線(9b)により短絡する。この金属配線(9b)は、隣接列のメモリセルとは分離され、メモリセル列方向にジグザグ状に延在する。各列ごとに、ドライバトランジスタソース電圧を伝達する線を個々に配設することができ、シングルポートメモリセル構造においても、メモリセル列単位でドライバトランジスタソース電圧の調整を行なうことができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 簡単な構成で、製造工程上でも大きな変更をすることなく、ノード部に高抵抗を付加して、ソフトエラー対策を施すことを可能とする。

【解決手段】 本発明の半導体装置は、SRAMメモリセルを構成する第1および第2のCMOSインバータ回路と、これらCMOSインバータ回路の一方の入力端子と他方の出力端子との間を互いに接続するように設けた第1および第2の抵抗要素とを備え、前記2つのCMOSインバータ回路のゲート電極パターン7a、7bと、前記2つのCMOSインバータ回路のノードNb、Naを接続するポリシリコンパターン11a、11bを設け、このポリシリコンパターン11a、11bに下地の段差形状を利用して自己整合的に高抵抗部分11a1を形成し、この高抵抗部分11a1で第1および第2の抵抗要素を構成したものである。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】総工程数を低減することができ、コストを低廉なものにする半導体記憶装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体記憶装置10は、半導体基板13と、第1不純物領域17と、第2不純物領域15と、第1不純物領域17と第2不純物領域15との間に形成されたチャネル領域75と、チャネル領域75が位置する半導体基板13の主表面上のうち、第1不純物領域17側の主表面上に形成された第1ゲート42と、チャネル領域75が位置する半導体基板13の主表面上にうち、第2不純物領域側15の主表面上に第2絶縁膜44を介して形成された第2ゲート45と、第1ゲート45に対して第2ゲート42と反対側に位置する半導体基板の主表面上に位置し、第1ゲート42の側面上に形成された第3絶縁膜46と、第3絶縁膜46とその直下に位置する半導体基板13との界面が、第2絶縁膜44とその直下に位置する半導体基板の主表面との界面より上方に位置する。

(もっと読む)

半導体集積回路

【課題】 表示デバイスを駆動するためにMPUから入力される画像データを一時的に記憶するSRAMを内蔵した半導体集積回路において、チップ面積を低減する。

【解決手段】 この半導体集積回路は、X方向に長手方向を有するP型半導体基板と、半導体基板内に形成され、Y方向に長手方向を有するN型ウエルと、N型ウエル内に形成されたソース・ドレインを有するPチャネルトランジスタQP1〜QP2、及び、P型半導体基板内に形成されたソース・ドレインを有するNチャネルトランジスタQN1〜QN4によって構成されるメモリセルMC00〜MC11と、メモリセルに接続され、Y方向に延在するビットラインBL0、BL0バー、BL1、BL1バーと、メモリセルに接続され、X方向に延在するワードラインWL0、WL1とを具備する。

(もっと読む)

半導体記憶装置

【課題】6トランジスタ型SRAMメモリセルにおいて、横型メモリセルレイアウトが多く用いられる様になってきが、形状が横長であるが故に、例えばビット線を第2層目の配線にした場合、横方向に走るワード線とVSS電源が同層で近接して並走し、ワード線の寄生容量負荷の増大や、配線パーティクルによる歩留低下という課題があった。

【解決手段】第2層目配線にて、列方向に並んで配置された複数のワード線351と、第3層目配線にて、行方向に並んで配置された複数の対をなすビット線352,353と、それぞれ対をなすビット線の間に配置された複数のVDD電源配線354と、第4層目配線にて、ビット線より1層上の配線層で形成されたVSS電源配線とを設けた。ビット線と並走するVSS電源の並走距離が短くなるので、ビット線容量が軽くなるとともに、ショート不良に至る確率が減少し歩留が向上する。

(もっと読む)

半導体装置

【課題】アクセスをより高速化する。

【解決手段】nMOSトランジスタQN1のゲートとpMOSトランジスタQP1のゲートがポリシリコン配線G10により構成され、nMOSトランジスタQN2のゲートとpMOSトランジスタQP2のゲートがポリシリコン配線G20により構成され、nMOSトランジスタQN3及びQN4のゲートがそれぞれポリシリコン配線W10及びW20により構成され、ポリシリコン配線G10とポリシリコン配線W20がnMOS領域13AからnMOS領域13Bへ延びる第1の方向に並べて配置され、ポリシリコン配線G20とポリシリコン配線W10が第1の方向に並べて配置されているので、第1の方向に対して垂直な第2の方向に延在するビット線の長さがトランジスタ2個分となる。

(もっと読む)

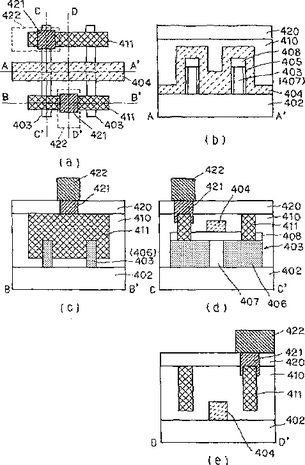

半導体装置の製造方法

【課題】SRAMを有する半導体装置の信頼性を向上させることのできる技術を提供する。

【解決手段】CMOSインバータを構成する負荷用MISと駆動用MISとに共通するゲート電極の引き出し部GM2の側壁に形成する第2サイドウォール9a1によって素子分離2の端部を覆うことにより、負荷用MIS(Ld1)のドレイン(p+型半導体領域13)と上記引き出し部GM2との両者に接する配線溝HM1を形成する際の素子分離2を構成する酸化シリコン膜の削れを、負荷用MIS(Ld1)のp+型半導体領域13の深さよりも小さく抑える。

(もっと読む)

41 - 60 / 74

[ Back to top ]