Fターム[5F083CR03]の内容

半導体メモリ (164,393) | ROM(EPROM、EEPROMを除く) (635) | マスクROM (119) | 配線接続の有無によるマスクROM (74)

Fターム[5F083CR03]の下位に属するFターム

配線接続部がダイオードを構成するもの (15)

Fターム[5F083CR03]に分類される特許

1 - 20 / 59

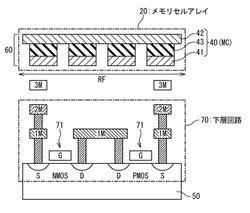

半導体装置

【課題】抵抗変化素子を備える半導体装置(半導体チップ)のチップ面積を削減すること。

【解決手段】半導体装置(1)は、半導体基板(50)上に形成されたトランジスタ(71)を含む下層回路(70)と、半導体基板(50)の上方の配線層(60)に形成されたメモリセルアレイ(20)と、を備える。メモリセルアレイ(20)の各メモリセル(MC)は、配線層(60)に形成された抵抗変化素子(40)を記憶素子として備る。メモリセルアレイ(20)は、メモリセル(MC)の直下に当該メモリセル(MC)との電気的接続用のビアが形成されていない第1領域(RF)を有している。下層回路(70)は、第1領域(RF)の少なくとも一部とオーバーラップするように配置されている。

(もっと読む)

半導体装置

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。

【解決手段】薄膜トランジスタ119と、薄膜トランジスタ上に第1の層間絶縁膜156と、第1の層間絶縁膜上の、ソース領域またはドレイン領域の一方に電気的に接続される第1の電極114と、ソース領域またはドレイン領域の他方に電気的に接続される第2の電極110と、第1の層間絶縁膜、第1の電極、及び第2の電極上に形成された第2の層間絶縁膜135と、第2の層間絶縁膜上の、第1の電極または第2の電極の一方に電気的に接続される第1の配線177と、第2の層間絶縁膜上の、第1の電極または第2の電極の他方に電気的に接続されない第2の配線178とを有し、第2の配線と前記第1の電極または第2の電極の他方は、第2の層間絶縁膜中の分断領域169によって、電気的に接続されない半導体装置及びその作製方法に関するものである。

(もっと読む)

半導体装置

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。また信頼性の高い半導体装置を提供する。

【解決手段】チャネル形成領域と、ソース領域またはドレイン領域を有する島状半導体膜131と、ゲート絶縁膜と、ゲート電極103とを有する薄膜トランジスタと、層間絶縁膜と、層間絶縁膜中に形成され、ソース領域またはドレイン領域の一方に達する複数のコンタクトホールを含む第1のコンタクトホール142と、ソース領域またはドレイン領域の他方に達する第2のコンタクトホール141とを有し、第2のコンタクトホール141の径は、第1のコンタクトホール142に含まれる複数のコンタクトホール142のそれぞれの径より大きく、第1のコンタクトホールの底面積の合計と、第2のコンタクトホール141の底面積は等しい半導体装置に関する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法とデータ書き換え方法

【課題】データ保持時間を、マスクROMと同様の無限大とすることができる、長期にわたりデータを保持できる信頼性の高いEEPROMを提供する。

【解決手段】不揮発性半導体記憶装置は、所定のセンスレベルに対して熱平衡状態しきい値電圧が正方向である第1の不揮発性半導体記憶素子100に正のデータを記憶し、熱平衡状態しきい値電圧が負方向である第2の不揮発性半導体記憶素子200に負のデータを記憶することでデータ保持時間を無限大にする。

(もっと読む)

半導体記憶装置

【課題】ゲート面積に依存するトランジスタばらつきを抑制し、読み出し動作を高速化した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ロウ方向に延びるワード線WL、カラム方向に延びる複数のビット線BL0,BL1,BL2で構成されたビット線グループ、並びに、トランジスタからなりワード線及びビット線グループの交差部に設けられたメモリセル、を有するメモリセルアレイと、ビット線を介してメモリセルからデータを読む読み出し回路とを備え、メモリセルは、トランジスタのソース又はドレインを、ビット線グループに属する複数のビット線BL0,BL1,BL2のいずれとも接続しないか又はいずれか1本とだけ接続するかの異なる接続状態を有し、トランジスタのゲートとなるアクティブ領域AAは、ビット線グループの複数のビット線BL0,BL1,BL2の配置領域及び各ビット線間のスペースに連続的に形成されている

(もっと読む)

半導体装置

【課題】メモリの大容量化と図りつつ、消費電力を軽減でき、且つ、消費電力を一定にす

る。

【解決手段】メモリを、複数のメモリブロックを対称に配置して構成する。また、メモリ

に供給されるアドレス信号のうち、特定の信号の組み合わせにより、データ読み出しまた

は書き込みの対象となるメモリセルを含むメモリブロックを一意に特定する。さらに、当

該メモリブロック以外のメモリブロックに供給される信号を一定値に保つ。このようにす

ることで、メモリアレイにおけるビット線の配線長を短縮し、負荷容量を軽減すると同時

に、メモリ内のあらゆるアドレスのメモリセルに対するデータ読み出しもしくは書き込み

において、消費電流を一定にできる。

(もっと読む)

多値ROMセル及び半導体装置

【課題】集積度が高く、製造ばらつきの影響が小さく、製造歩留まりの高い多値ROMセルを提供する。

【解決手段】多値ROMセルは、ROMセルトランジスタTrと、複数のビット線BT1〜BT3と、第1金属配線31〜44とを具備している。ROMセルトランジスタTrは、基板表面の領域に設けられている。複数のビット線BT1〜BT3は、基板表面の上方に設けられ、Y方向に伸び、Z方向に並んで配置されている。第1金属配線31〜44は、ROMセルトランジスタTrのソース・ドレイン22の一方に接続され、複数のビット線BT1〜BT3の各々の近傍にまで連なる。第1金属配線31〜44は、複数のビット線BT1〜BT3のうちのいずれかに接続されているか、又は、いずれにも接続されていない。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

半導体記憶装置の製造方法及び半導体記憶装置

【課題】メモリセルアレイの保持内容に起因するリーク電流による誤読み出しを抑制可能な半導体記憶装置を製造する。

【解決手段】接地電位制御要否判定部3が、設計対象のメモリセルアレイの保持内容から、メモリセルのトランジスタの接地電位の制御の要否を判定し、接地電位の制御が必要と判定された場合、接地電位制御回路生成部4が、読み出し動作時に非選択となるトランジスタの接地電位を引き上げる接地電位制御回路を生成する。

(もっと読む)

半導体記憶装置

【課題】電力消費をより低減可能な新たなビット線階層化方式を備えた半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、行列状に設けられた複数のメモリブロックBと、複数のメモリブロックBに対応して設けられた複数の主ビット線GLとを具備する。メモリブロックBは、行列状に設けられた複数のメモリセルCと、列ごとに設けられた複数の副ビット線BLと、列及び行ごとに設けられ、複数のメモリブロックBに共通である複数のワード線WLと、対応する主ビット線GLを複数の副ビット線BLのいずれかに接続するスイッチ回路SCとを備える。読出し対象の対象セルC1の読出し動作時に、対象セルC1に対応する主ビット線GL1を選択し、対象セルC1の列に対応する副ビット線BL1をスイッチ回路SC1により選択し、複数のワード線WLのうち、対象セルC1の列及び行に対応するワード線WL1を選択する。

(もっと読む)

記憶装置、集積回路装置及び電子機器

【課題】製造コストの増加を抑止して不揮発性メモリーセルとマスクROMメモリーセルとを混在できる記憶装置、集積回路装置及び電子機器等を提供すること。

【解決手段】記憶装置は、複数のメモリーセルME1、ME2、MR1、MR2と、複数のワード線WL1、WL2と、複数のビット線BL1、BL2と、複数のソース線SL1、SL2とを含む。複数のメモリーセルのうちの第1のグループのメモリーセルは、電気的にデータの書き込み及び消去が可能な不揮発性メモリーセルME1、ME2である。複数のメモリーセルのうちの第2のグループのメモリーセルは、マスクによりデータが設定されるマスクROMメモリーセルMR1、MR2である。マスクROMメモリーセルMR1、MR2は、ソースと対応するソース線SL2とを電気的に接続するためのコンタクトCN1、CN2の有無によってデータが設定される。

(もっと読む)

歪み材料を有する半導体デバイス

歪み材料を有する半導体デバイスが開示される。特定の実施形態では、半導体デバイスは、第1ドレインと第1ソースとの間に第1ゲートを含む第1セルを含む。半導体デバイスはまた、第1セルに隣接する第2セルを含む。第2セルは、第2ドレインと第2ソースとの間に第2ゲートを含む。半導体デバイスはさらに、第1ソースと第2ソースとの間にシャロートレンチ分離領域を含む。第1ソースおよび第2ソース上の第1量の歪み材料は、第1ドレインおよび第2ドレイン上の第2量の歪み材料より多い。  (もっと読む)

(もっと読む)

複数ビット値を格納するための読み出し専用メモリセル

【課題】複数ビット値を格納するための読み出し専用メモリセルを開示する。

【解決手段】該読み出し専用メモリセルは、少なくとも3本の出力線であって、該少なくとも3本の出力線のそれぞれは、異なる複数ビット値を表す、少なくとも3本の出力線と、該3本の出力線のうちの1本と電圧源との間に接続される切り替え装置とを含む。該切り替え装置は、切り替え信号に応答して、該電圧源と該3本の出力線のうちの1本との間の電気接続を提供し、該接続された出力線の電圧は、既定の電圧への接続に応答して値を切り替え、それによって、該出力線によって表される該複数ビット値が選択される。該選択された複数ビット値を出力するための、出力装置も提供する。

(もっと読む)

マスクROMおよびその製造方法

【課題】マスクROMのメモリセルアレイ領域の面積増加を防ぎ、製造コストの低減を実現する。

【解決手段】

メモリセルアレイ領域10と、周辺回路領域を含むコンタクト方式のマスクROMであって、所定の配線層間を接続する複数のビア104A〜R、102A〜H、を含み、プログラミングに使用されるメモリセルアレイ領域10のビア102A〜Hと、前記周辺回路領域のビア104A〜Rとでは、径の大きさが異なるマスクROM。

(もっと読む)

密封型半導体記録媒体及び密封型半導体記録装置

【課題】 密封型半導体記録媒体及び密封型半導体記録装置に関し、無線により電力を給電するとともに、相互干渉なしに無線でデータ通信を高速に行うことが可能な密封された高信頼性の半導体メモリを低コストで提供する。

【解決手段】 少なくとも1枚の半導体基板に最大辺が20mm以下のサイズの複数の読出専用メモリブロックを互いに電源配線を共有しない状態で設け、前記各読出専用メモリブロックに電力受給用コイルとデータ通信用コイルを備えるとともに、前記各読出専用メモリブロックに互いに異なったデータを書き込む。

(もっと読む)

不揮発性半導体記憶装置

【課題】製造技術の限界によりトランジスタの最小サイズが決まるため、ROMの高容量化にも限界があるという課題があった。

【解決手段】本発明の不揮発性半導体記憶装置は、EEPROMとマスクROMとを一体とした不揮発性半導体記憶装置であり、メモリトランジスタの電荷蓄積膜に蓄える電荷の有無によりデータを記憶するEEPROMと選択コンタクトホールの有無によりデータを記憶するマスクROMとを同一平面上に構成する。これにより、トランジスタサイズを小さくすることなく、ROM容量を増やすことが可能となる。

(もっと読む)

半導体集積回路

【課題】マスクROMを内蔵した半導体集積回路において、トランジスタのリーク電流の増加や不純物拡散領域の抵抗値の増加等を招くことなく、メモリセルアレイのレイアウト面積を削減する。

【解決手段】この半導体集積回路は、マスクROMを内蔵した半導体集積回路であって、該マスクROMが、第1の方向において隣接する2つのNチャネルトランジスタのソースが共通化され、第1の方向と直交する第2の方向において隣接する複数のNチャネルトランジスタのソースが分離されているようにした複数のメモリセルと、各々のポリシリコンが第2の方向に並んだ1行のメモリセルに含まれている全てのNチャネルトランジスタのゲートを構成すると共に、所定の位置において第1の方向及び第1の方向と反対の方向に凸部を有するようにした複数のワード線とを具備する。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

半導体記憶装置

【課題】マスクROMとEEPROMとは、その構造が著しく異なることら、マスクROM領域をEEPROM領域に、あるいはEEPROM領域をマスクROM領域に変更することは難しい。各メモリのメモリ容量は固定化され、結果として、システムの自由度が制限されるという問題が生じていた。

【解決手段】本発明の半導体記憶装置は、半導体基板上のチャネル領域に同一構造のメモリ絶縁膜を備える複数のメモリ素子を有し、メモリ絶縁膜の所定の領域に電荷を注入することで情報を記憶する第1のメモリ素子と、ソースとドレインとの間に電流を流さないことで情報を記憶する第2のメモリ素子とからなる。このような構造とすることで、第1のメモリ素子と第2のメモリ素子との変更が容易となる。

(もっと読む)

半導体装置

【課題】異なる構造の半導体メモリセルを備えた半導体メモリ領域を縮小化するための半導体装置を提供する。

【解決手段】半導体層に形成されるRAMの第1のトランジスタと、第1のトランジスタの第1のソース/ドレイン17に電気的に接続される第1電極を有するキャパシタQと、第1のトランジスタに隣接する領域の半導体層に形成されるROMの第2、第3のトランジスタと、第1のトランジスタの第2のソース/ドレイン16と第2のトランジスタの第1のソース/ドレイン20に電気的に接続されるビット線60とを有する。

(もっと読む)

1 - 20 / 59

[ Back to top ]