Fターム[5F083CR13]の内容

半導体メモリ (164,393) | ROM(EPROM、EEPROMを除く) (635) | PROM(Programmable ROM) (484) | PN接合破壊型ROM (22)

Fターム[5F083CR13]に分類される特許

1 - 20 / 22

不揮発性半導体記憶装置及びその製造方法

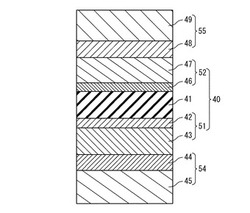

【課題】比較的高い抵抗率を持つ導電体を電極に用いた場合でも、高信頼な抵抗変化素子を実現する。

【解決手段】不揮発性半導体記憶装置は、第1配線54と、第2配線55と、一端を前記第1配線54に、他端を前記第2配線55にそれぞれ電気的に接続されたメモリセル40とを具備する。メモリセル40は、抵抗値の変化で情報を記憶する抵抗変化層41と、抵抗変化層41の両端にそれぞれ接続され、貴金属を含まない第1電極51及び第2電極52とを備える。第1電極51は、外側電極43と、外側電極43と抵抗変化層41との間に設けられた界面電極42とを含む。界面電極42の膜厚は、外側電極43の膜厚よりも薄い。界面電極42の抵抗率は、外側電極43の抵抗率よりも高い。第1電極51の抵抗値Rsは、抵抗変化層52の低抵抗状態の抵抗値Ronよりも低い。

(もっと読む)

積層した接続レベルを有する集積回路装置用マスク数の低減法

【課題】3D積層メモリ装置は、各接続レベル毎に別個のマスクが使用されるので必要なマスク数は多くなるが、パターンを工夫して必要マスク数を減らす。

【解決手段】3次元積層集積回路装置は配線領域に接続レベルの積層部を有する。接続レベルの積層部で2のN乗個のレベルまで含む配線接続領域を形成するためのN個のエッチングマスクの組だけが必要とされる。幾つかの例によれば、2のX−1乗(2X−1)個の接続レベルは、連続番号Xのエッチングマスクでエッチングされ、1つのマスクがX=1であり、他の1つのマスクがX=2であり、X=Nまで付与される。当該方法は接続レベルでの形成領域に整合した配線接続領域を形成する。

(もっと読む)

半導体装置およびその動作方法

【課題】省面積化を図ることが可能な半導体装置およびその動作方法を提供する。

【解決手段】各記憶素子21は、P型の半導体層211Pと、半導体層211P内で互いに分離するように配設されたN型の半導体層212N,213Nと、半導体層211P上の半導体層212N,213N間に対応する領域に設けられた下層側の誘電体膜216および上層側の導電体膜217と、半導体層212Nと電気的に接続された電極215Aと、半導体層213Nと電気的に接続された電極215Bと、導電体膜217と電気的に接続された電極215Cとを有する。駆動対象の記憶素子21に対して、電極215B,215C間に所定の閾値以上の電圧V1を印加して、誘電体膜216の少なくとも一部分を絶縁破壊させて導電体膜217,半導体層213N間に電流を流し、半導体層212N,213N間の領域にフィラメント210を形成することにより、情報の書き込み動作を行う。

(もっと読む)

半導体装置およびその動作方法

【課題】省面積化を図ることが可能な半導体装置およびその動作方法を提供する。

【解決手段】各記憶素子21は、P型の半導体層211Pと、半導体層211P内で互いに分離するように配設されたN型の半導体層212N,213Nと、半導体層212Nと電気的に接続された電極215Aと、半導体層213Nと電気的に接続された電極215Bとを有する。駆動対象の記憶素子21に対して、電極215Aと電極215Bとの間に所定の閾値以上の電圧V1を印加して、半導体層212Nと半導体層213Nとの間の領域にそれらの半導体層同士を電気的に繋ぐ導電パスであるフィラメント210を形成することにより、情報の書き込み動作を行う。

(もっと読む)

ストリング選択線及びビット線の改善されたコンタクトレイアウトを有する3次元メモリアレイ

【課題】インターコネクト及びコンタクト用の実装面積が小さい3次元集積回路メモリ用の構造を低製造コストで提供する。

【解決手段】3次元メモリデバイスは、絶縁材料21,22,23,24で分離され、復号化回路を介してセンスアンプに結合可能なビット線BLnとして導電材料の複数の帯片の形状をしている。導電材料帯片11,12,13,14は、スタック横面に側面を有する。ワード線WLn,WLn+1の複数の導電線16,17は行デコーダに結合でき、複数のスタック上で直交して延びる。導電線は、スタックの表面に共形である。記憶素子は、スタック上の半導体材料帯片の側面と導電線の間の交点の界面領域の多層アレイに設けられる。3次元メモリは、複数層に対する2つの最小線幅のマスクで作られる。半導体材料帯片の端部に階段構造が含まれる。半導体材料帯片に平行な金属層上と、ワード線に平行な上部金属層上にSSLインターコネクトを含む。

(もっと読む)

3Dメモリアレイの製造のためのX線用の共用マスクとY線用の共用マスク

デバイス層の数より少ない数のビット線マスクを用いて3次元メモリを製造する構造および方法を開示する。第1のビット線層を第1のデバイスレベルに形成するために第1のビット線マスクが使用される。第1のビット線層は複数の第1のビット線を含む。第1のビット線マスクは、第2のビット線層を第2のデバイスレベルに形成するためにも使用される。第2のビット線層は複数の第2のビット線を含む。第1のビット線および第2のビット線は、同じマスクパターンを使用するにもかかわらず、ビット線接続レベルへの異なる電気的接続を有する。  (もっと読む)

(もっと読む)

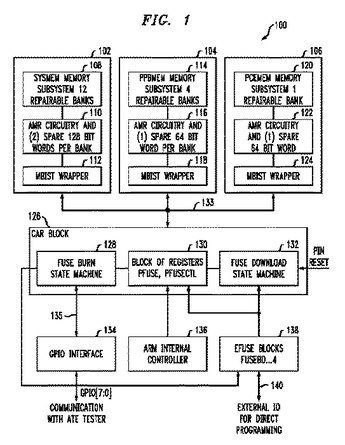

不揮発性でプログラム可能なメモリセルおよびメモリアレイ

不揮発性1回限りプログラム可能メモリセルは、2端子ヒューズおよび3端子アンチヒューズを、直列に結合する。複数のそのようなメモリセルが、1つの不揮発性プログラム可能メモリアレイの中に含まれうる。また、再プログラム可能な不揮発性プログラム可能メモリセルが、記述される。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置およびその書き込み方法と読み出し方法

【課題】 読み出し時の電圧を書き込み時の電圧まで上げても誤書き込みの起きない半導体装置を提供する。

【解決手段】 オン耐圧の異なるMOSトランジスタを同一基板上に形成し、オン耐圧の低い方のMOSトランジスタを記憶素子として用い、ゲートオン状態でドレイン耐圧が低いことを利用してオン耐圧の低い方のMOSトランジスタのドレイン/基板間のPN接合を短絡せしめることによってデータの書き込みを行う。

(もっと読む)

非線形導体メモリ

高速で低電力のメモリ素子は、非線形導体のアレイを備え、格納、アドレスデコーディング、および出力検出はすべて、ダイオードまたは他の非線形導体によって達成される。様々な実施形態において、行抵抗器および列抵抗器は、選択されていない行または列に接続されているときの高抵抗と、選択された行および列に接続されたときの低抵抗との間で切り替え可能である。電子メモリ素子は、情報回路と、複数の行スイッチと、複数の列スイッチと、選択回路とを含む。  (もっと読む)

(もっと読む)

電子装置の製造方法、メモリ回路の動作方法、および電子装置

半導体基板(10)上に形成された誘電体層(12)を備える、電子装置。誘電体層(12)上には、代表長さを有するポリシリコンヒューズ構造(14)が形成される。ポリシリコンのヒューズ構造の第1部分(141)と第2部分(143)は、シリサイド化さる。ポリシリコンヒューズ構造(114)のうち、第1部分(141)と第2部分(143)の両方に隣接する第3部分(142)は、シリサイド化されない。  (もっと読む)

(もっと読む)

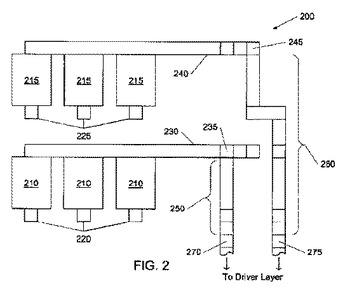

ヒューズ焼付け状態機械及びヒューズダウンロード状態機械に基づく内蔵メモリ修理方法

内蔵メモリ内の1以上の不良を修理するためのメモリ修理回路は少なくとも1つのヒューズレジスタ及び当該ヒューズレジスタに結合された状態機械回路を含む。状態機械回路は、(i)内蔵メモリ内の1以上の不良に関するステータス情報を受信し、(ii)ステータス情報に基づいてメモリが修理可能かを判断し、(iii)メモリが修理可能であるとみなされるときは、メモリの不良メモリセルに対応するアドレスを記憶し、(iv)メモリ修理回路に供給された電圧源を用いて、不良メモリセルに対応するアドレスをヒューズレジスタに焼き付け、及び(v)不良メモリセルに対応するアドレスがヒューズレジスタに焼き付けられたことを確認するように動作する第1の状態機械を実装する状態機械回路を備える。状態機械回路がさらに、(i)少なくとも1つのヒューズレジスタに記憶された情報を内蔵メモリに関連する少なくとも1つの修理レジスタにダウンロードし、及び(ii)アドレスが内蔵メモリ内の不良メモリ部分に対応する回路で受信されると、不良メモリ部分へのアクセスを少なくとも1つの修理レジスタに再ルーティングするように動作する第2の状態機械を実装する。  (もっと読む)

(もっと読む)

不揮発メモリ、その製造方法及び、当該メモリの書き込み読み出し方法

【課題】大幅な製造装置の更新等が無くともメモリの集積度を向上させ、チップ面積縮小によるコストダウンを図ること。

【解決手段】本発明による不揮発性メモリのメモリセルは、上部電極および下部電極と、当該上部電極から下部電極までの間に、一度だけ状態変化が可能な状態変化部を含む。この状態変化部は、P型半導体またはN型半導体のいずれか一方の半導体からなる第1半導体層と、前記P型半導体またはN型半導体の他方の半導体からなり前記第1半導体層の上下それぞれでPN接合部を介して設けられた第2半導体層を備えて構成される。

(もっと読む)

半導体装置

【課題】半導体装置に搭載された不揮発性記憶装置に格納された情報を読み出す時、アドレス信号などを入力し、センスアンプなどを用いて情報を読み出す。このとき所定の時間を要するので、その遅れを考慮した半導体装置の設計が必要である。また、センスアンプは消費電流が膨大である。さらに、読み出しビット数が決められているので、1ビットのみ読み出す場合にも、他の不要な情報も読み出す必要がある。

【解決手段】電気的に導通または絶縁する手段を有する電気素子と、リセット素子と、ラッチ素子と、から構成される記憶素子により、不揮発性記憶回路を構成する。記憶素子では、無線チップのリセット時に、電気素子が電気的に絶縁か導通かにより、異なる情報をラッチ素子に格納する。このような構成とすることで、不揮発性記憶装置を搭載した低消費電力の無線チップを安価に提供することができる。

(もっと読む)

トリミング回路、半導体装置、データ書き込み方法および電子機器

【課題】電気的に不可逆変化をする二つの異なるフューズ素子を用いるという最小限の回路構成とすることで、書き込みデータの書き換えを複数回行うことを可能にする。

【解決手段】導通状態から非導通状態に電気的に不可逆変化するフューズ素子2と、前記フューズ素子2と直列に接続された非導通状態から導通状態に電気的に不可逆変化するアンチフューズ素子1とで構成され、前記フューズ素子2と前記アンチフューズ素子1との間に電気信号を入出力するためのスイッチ端子Sが接続されていることを特徴とするトリミング回路であり、このトリミング回路を備えたブロックBを複数接続して構成されるフューズ回路で構成されたことを特徴とする半導体装置である。

(もっと読む)

半導体装置

【課題】2つのバイポーラトランジスタを用いたアンチヒューズにおいて、書込み電圧を低減する。

【解決手段】第1エミッタ電極8と、第1ベース電極6と、第1コレクタ電極7とを第1領域の上方に有する第1トランジスタQ1を具備し、第1ベース電極6と第1ベース領域の間を接続するベース引出しポリシリコン9は、第1領域の外に設けられる第2領域の上方を通過させ、抵抗値を付加する。

(もっと読む)

半導体装置

【課題】D-Aコンバータの性能を向上させることができる。

【解決手段】複数の第1メモリセルを含むメモリマットと、複数の第1メモリセルに接続される複数の出力線とを具備するDACであって、複数のメモリセルの夫々は、バイポーラトランジスタを含み前記バイポーラトランジスタの接合を破壊するか否かで情報を不揮発で記憶する第1メモリ部と、第1メモリ部に接続され複数の出力線のうち対応する一つに情報を出力する第2メモリ部とを有し、第2メモリ部へ情報を書き込む場合に、第1メモリ部から第2メモリ部へ情報を転送する第1モードと、第2メモリ部を外部から特定して情報を書き込む第2モードとを有する。

(もっと読む)

データ記憶・演算装置、及びその製造方法

【課題】ROM及び/又はWORM及び/又はREWRITABLEメモリモジュール及び/又は演算モジュールを基板上に備えたデータ記憶・演算装置であり、低温適応の有機材料及び/又は低温で処理された無機膜を備えている。

【解決手段】メモリ及び/又は演算モジュールは、層を順次蒸着することによって、基板上に備えられる。層の蒸着及び処理は、すでに蒸着されて処理された下にある単数又は複数の層、特に有機材料を、安定のための限界を超える過度な静的又は動的温度に晒さないような熱的条件下で行われる。

(もっと読む)

分子電子素子のための複合有機分子

電子素子において導電経路として有用な複合分子が提供される。この複合分子は、電子流に方向付けを提供するために、少なくとも一のp/n接合を含み、そして素子における集合の間にこの分子に自己配向を与える一末端ワニ口クリップ基を含み、この分子の構造を非対称にする。この複合分子は、ダイオード、分子スイッチ、トランジスタにおいて、およびメモリー素子の製造において使用され得る。 (もっと読む)

アンチフューズセル及びその製造方法

アンチフューズセルは、ケイ素化金属膜(12,13)で覆われたソース(7)及びドレイン(8)領域を有する集積回路の標準的MOSトランジスタと、前記MOSトランジスタを少なくとも部分的に囲む、抵抗性膜の少なくとも1つトラック(24)とを備え、前記ケイ素化金属の金属がドレイン及び/又はソース接合通して拡散するように加熱用の電流を通過させるのに適合している。  (もっと読む)

(もっと読む)

半導体装置

【課題】不揮発性であって、作成が簡単であり、追記が可能な記憶回路を有する半導体装置及びその作製方法の提供を課題とする。

【解決手段】一対の導電層間に有機化合物層が挟まれた単純な構造の記憶素子を有する半導体装置及びその作製方法を提供する。また、不揮発性であり、作製が簡単であり、追記が可能な記憶回路を有する半導体装置及びその作製方法を提供する。絶縁層上に設けられた複数の電界効果トランジスタと、複数の電界効果トランジスタ上に設けられた複数の記憶素子とを有する。複数の電界効果トランジスタは、単結晶半導体層をチャネル部とした電界効果トランジスタである。複数の記憶素子の各々は、第1の導電層と、有機化合物層と、第2の導電層が順に積層された素子である。

(もっと読む)

1 - 20 / 22

[ Back to top ]