Fターム[5F083EP17]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 電荷蓄積機構 (5,261) | トラップ蓄積型 (2,146)

Fターム[5F083EP17]の下位に属するFターム

MNOS型(MONOS型を含む) (1,550)

Fターム[5F083EP17]に分類される特許

201 - 220 / 596

半導体記憶装置

【課題】電荷蓄積層に蓄積された電荷の抜けを抑制し、データの保存安定性に優れた半導体記憶装置を提供する。

【解決手段】シリコン基板10の表層領域に形成され、シリコン基板10上のゲート絶縁膜14に対向するチャネル領域16とソース領域18との間及び/又はチャネル領域16とドレイン領域20との間に設けられた抵抗変化部22、24と、抵抗変化部22、24上に形成された電荷蓄積部40、60と、を有する半導体記憶装置100であって、電荷蓄積部34、54は、第1酸化膜26、46、データが記憶される前に該データとは電気的に異なる電荷が注入されている電荷蓄積層34、54、及び第2酸化膜30、50が順次積層されてなり、第1酸化膜26、46中に少なくとも1層の電荷抜け防止層28、48が設けられている。

(もっと読む)

半導体メモリ

【課題】一様性の高い電荷蓄積層を備えた半導体メモリを実現する。

【解決手段】n型シリコンからなる基板1に対して、Al2O3からなる第1の障壁層4、SiをドープしたAl過剰のAl2O3からなる電荷蓄積層5、Al2O3からなる第2の障壁層6、n型ポリシリコンからなるゲート電極7を順次積層して構成する。

(もっと読む)

不揮発性半導体メモリ及び不揮発性半導体メモリの製造方法

【課題】不揮発性半導体メモリの動作の安定化を図ることができる。

【解決手段】本発明の例に関わる不揮発性半導体メモリは、メモリセル形成領域101内に設けられる2つの拡散層8Aと、拡散層8A間の半導体基板1表面に設けられるゲート絶縁膜3Aと、ゲート絶縁膜3A上に設けられる電荷蓄積層4Aと、電荷蓄積層4A上に設けられブロック絶縁膜6Aと、ブロック絶縁膜6A上に設けられるゲート電極7Aとを有するメモリセルMCと、セレクトゲート形成領域102内に設けられる2つの拡散層8B,8Cと、拡散層8B,8C間の半導体基板1表面に設けられるゲート絶縁膜5Aと、ゲート絶縁膜5A上に直接接触して設けられるブロック絶縁膜6Aと同一構成の中間絶縁膜6Bと、中間絶縁膜6B上に設けられるゲート電極7Bとを有するセレクトゲートトランジスタSTと、を備える。

(もっと読む)

プログラム飽和に対する改良された耐性を有する拡張可能なポリシリコン間誘電体スタック

【課題】コスト効率の高い製造プロセスと、これにより得られた電荷蓄積層と制御ゲートとの間の誘電体の絶縁特性が改良された不揮発性デバイスとを提供する。

【解決手段】不揮発性メモリデバイス20の製造方法において、電荷が蓄積される層3の上部層の上に、DyScOのシリコン酸化物消費材料の層を成長させる工程を含む。また、ポリシリコン間/ブロッキング誘電体41,42が、電荷が蓄積される層3の上部層の上に、DyScOのシリコン酸化物消費材料の層を含み、シリコン酸化物消費材料が上部層の少なくとも一部を消費した不揮発性メモリデバイス。

(もっと読む)

不揮発性記憶素子及びその製造方法

【課題】熱的安定性に優れた不揮発性記憶素子を提供する。

【解決手段】不揮発性記憶素子は、半導体領域11と、半導体領域11内に互いに離間して設けられたソース領域12及びドレイン領域13と、ソース領域12及びドレイン領域13間の半導体領域11上に設けられたトンネル絶縁膜14と、トンネル絶縁膜14上に設けられた電荷蓄積層15と、電荷蓄積層15上に設けられたブロック絶縁膜16と、ブロック絶縁膜16上に設けられた制御ゲート電極17とを含む。電荷蓄積層15は、Hf、Al、Zr、Ti、及び希土類金属のうち少なくとも1つを含む、全部又は一部が結晶化した酸化物、窒化物、或いは酸窒化物を含む。ブロック絶縁膜16は、希土類金属のうち少なくとも1つを含む酸化物、酸窒化物、シリケート、或いはアルミネートを含む。

(もっと読む)

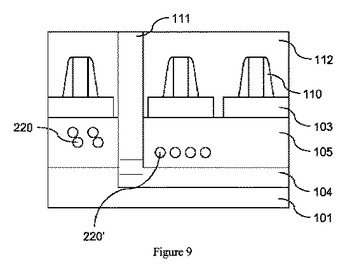

埋め込み型トラッピング層によるトランジスタの閾値電圧の調整方法

方法は、電子サブアセンブリの形成について、調整可能な閾値電圧を有する少なくとも1つの第1のトランジスタ(110)を担持する半導体層(103)が絶縁層(102、105)に接合される組み立てステップと、半導体層および第1のトラッピングゾーンが容量結合されるように、第1のトラッピングゾーン(220)が所定の第1の深さで絶縁層に形成される形成ステップであって、前記第1のトラッピングゾーンが、前記第1のトランジスタのチャネルの少なくとも下に延び、かつ前記第1のトラッピングゾーンの外側のトラップの密度より高い密度のトラップを有する形成ステップとを含み、前記第1のトランジスタからの有用な情報はこのトランジスタ内の電荷移動である。具体的な実施形態において、第2のトランジスタのチャネルの少なくとも下に延びる第2のトラッピングゾーンが、第1のトラッピングゾーンに使用されるのとは異なるエネルギーおよび/または用量および/または原子の第2の注入によって形成される。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】本発明は、制御電極からのリーク電流を抑制しつつ、制御電極と電荷蓄積層との間の所定のカップリング比を確保することができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板に形成されたトレンチ内に設けられた素子分離絶縁領域と、前記半導体基板と前記素子分離絶縁領域に対向して設けられた制御電極と、前記半導体基板と前記制御電極との間に設けられた電荷蓄積層と、前記半導体基板と前記電荷蓄積層との間に設けられたトンネル絶縁膜と、前記電荷蓄積層と前記制御電極との間に設けられた第1のブロック層と、前記第1のブロック層に隣接し、前記素子分離絶縁領域と前記制御電極との間に設けられた第2のブロック層とを備え、前記第2のブロック層の比誘電率は、前記素子分離絶縁領域の比誘電率よりも大きいことを特徴とする半導体装置が提供される。

(もっと読む)

フラッシュメモリ及びその製造方法

【課題】30nm以下の微細化に適応できるフラッシュメモリ及びその製造方法を提供する。

【解決手段】基板101に接続された上部にスペーサ絶縁膜116を有するフィン構造のビットラインから形成されたメモリセル部の最小加工寸法をFとするとき、独立に書き込み/消去可能なビットライン2本が対になって4F周期に配置されてメモリセル部が形成され、一対のフィンの上部を覆うように記憶絶縁膜が形成されている。

(もっと読む)

絶縁膜、およびこれを用いた半導体装置

【課題】リーク電流を減少させることのできる絶縁膜を提供することを可能にする。

【解決手段】金属と、水素と、窒素とを含む非晶質の酸化物誘電体膜を有し、前記酸化物誘電体膜内の前記窒素の含有量[N]および前記水素の含有量[H]は、

{[N]−[H]}/2≦1.0×1021cm−3

を満たす。

(もっと読む)

フラッシュメモリ及びその製造方法

【課題】隣接ワードラインの間をシームレスに埋め込み、セル間干渉が抑制された良好な素子特性を有するフラッシュメモリ及びその製造方法を提供することを目的としている。

【解決手段】フラッシュメモリの隣接ワードライン間を埋め込む絶縁膜としてO3−TEOS膜が埋め込まれており、特にビットライン上の隣接ワードライン間が下地依存性を有するO3−TEOS膜109によってシームレスに埋め込まれていることを特徴としている。

(もっと読む)

不揮発性半導体記憶素子及びその製造方法並びに表示装置

【課題】複雑な工程を経ることなく不揮発性半導体記憶素子を製造する。

【解決手段】不揮発性半導体記憶素子10は、絶縁基板11と、絶縁基板11上に設けられ、ソース領域13s、チャネル領域13c、及びドレイン領域13dが形成された半導体層13と、半導体層13を覆うように設けられたゲート絶縁膜14と、ゲート絶縁膜14内に、半導体層13のチャネル領域13cに対応するように埋設されたメモリ用金属粒子層15と、ゲート絶縁膜14上に、半導体層13のチャネル領域13cに対応するように設けられたゲート電極16と、を備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 ゲート絶縁膜にかかる電界を増大させるとともに、ホットエレクトロン発生数を増加させることにより、書き込み効率の向上を実現することができる。

【解決手段】 本発明の不揮発性半導体記憶装置は、第1導電型の半導体基板1内に互いに離間して形成された第2導電型のソース領域2及びドレイン領域3の間に、ソース領域2及びドレイン領域3と離間形成されるように第2導電型の半導体領域4を備える。そして、このソース領域2と半導体領域4との間、及びドレイン領域3と半導体領域4との間の半導体基板1上には、第1及び第2の浮遊ゲート6a、6bが互いに隔てられ、かつ第1のゲート絶縁膜5を介してそれぞれ形成されている。また、第1及び第2の浮遊ゲート6上、並びに第1及び第2の浮遊ゲート6a、6b間の第1のゲート絶縁膜5上に、ゲート間絶縁膜7及び第2のゲート絶縁膜8をそれぞれ介して制御ゲート9が設けられている。

(もっと読む)

半導体素子及び半導体装置

【課題】短チャネル効果が抑制され高い電流駆動力を有する細線半導体素子を実現する。

【解決手段】半導体基板上に設けられた絶縁領域と、絶縁領域上に略平行に整列して設けられた第一導電型の複数の線状半導体層と、各線状半導体層に離間して設けられた第二導電型のソース・ドレイン領域と、ソース・ドレイン領域の間に設けられたチャネル領域と、各線状半導体層の上面と側面上に設けられた第一の絶縁膜と、第一の絶縁膜上に設けられ、複数の線状半導体層と交差するように連続的に設けられたゲート電極とを有し、線状半導体層を線方向に流れる電流に垂直、且つ基板表面に平行に測ったチャネル領域の長さが、チャネル領域中の不純物濃度で決まる最大空乏層幅の二倍以下であり、複数の線状半導体層の間隔が、線状半導体層の上面とゲート電極との間隔の二倍以下であり、絶縁領域の表面の少なくとも一部に於ける誘電率が、酸化シリコンの誘電率よりも低い。

(もっと読む)

不揮発性半導体記憶装置

【課題】YUPIN効果を抑えるようなセルの配置デザインを実現することができ、メモリセルの微細化及び高集積化をはかる。

【解決手段】ストライプ状の素子形成領域11が並列配置され、各々の素子形成領域11に電荷蓄積層12と制御ゲート13を有する不揮発性メモリセルが複数個設けられた不揮発性半導体記憶装置であって、電荷蓄積層12は、互いに異なる素子形成領域11間で隣接するもの同士が、ストライプ方向にずらして配置されている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】信頼性が高い不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】シリコン基板2上に、それぞれ複数の絶縁膜3及び電極膜4を交互に積層して積層体5を形成する。次に、積層体5に積層方向に延びる貫通ホール7を形成する。次に、選択窒化処理を施し、貫通ホール7の内面のうち電極膜4に相当する領域に、窒化シリコンからなるチャージ層12を選択的に形成する。次に、高圧酸化処理を行い、チャージ層12と電極膜4との間に、酸化シリコンからなるブロック層13を形成する。次に、貫通ホール7の内側面上に、酸化シリコンからなるトンネル層11を形成する。これにより、チャージ層12が電極膜4ごとに分断されたフラッシュメモリ1が製造される。

(もっと読む)

不揮発性半導体記憶素子、不揮発性半導体記憶装置、不揮発性半導体記憶素子のデータ書き込み方法、および、不揮発性半導体記憶装置のデータ書き換え方法

【課題】スケーラビリティが高く、ビットまたはバイト単位の書き換えが可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶素子をマトリックスに配列し、Y側にページバッファを設ける。1本のワード線に接続されたメモリセルのデータをページバッファに読み出したのち、これらのメモリセルのデータを消去する。そして、ページバッファに読み出したデータのうち1または複数のデータを書き換え、書き換えられたページバッファの内容を前記1本のワード線に接続された各メモリセルに書き戻す。これを高速に行うことにより、ビットまたはバイト単位の書き換えをエミュレートする。

(もっと読む)

不揮発性半導体記憶素子、及び不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置が備える不揮発性半導体記憶素子を標準的なCMOSプロセスで製造するトランジスタを用いて構成する。

【解決手段】標準的なCMOSプロセスによるトランジスタ二個を一組とし備える記憶部200は、ソース・半導体基板間に発生するバンド間トンネル電流が流れる際に発生する正孔と電子を、半導体基板とゲート酸化膜の境界付近にある結晶欠陥にトラップさせる。結晶欠陥に正孔又は電子をトラップしたトランジスタは閾値が変化するので、記憶部200が備えるNMOSトランジスタ201とNMOSトランジスタ202の閾値の変化によるドレイン電流の差をSRAM部100が備えるセンスアンプ回路で検出することにより記憶されたデータの読み出しを行う。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体基板、および半導体基板の製造方法

【課題】容易にかつ低コストで従来のようなゲッタリング効果を得られるゲッタリングサイトを形成する半導体装置を得ることを目的とする。

【解決手段】本発明の一実施形態における半導体装置の製造方法は、(a)半導体基板1を準備する工程と、(b)半導体基板1の表面側からイオン注入し、半導体基板1の表層部にアモルファス層2を形成する工程と、(c)半導体基板1に熱処理を行ってアモルファス層2を再結晶化した再結晶層3を形成し、半導体基板1と再結晶層3との界面近傍に微少結晶欠陥4を形成する工程と、(d)再結晶層3に半導体素子5を形成する工程と、を備える。

(もっと読む)

半導体装置の作製方法

【課題】より高集積化され、薄型化及び小型化された半導体装置を作製することを目的の一とする。また、半導体装置において、高性能化、低消費電力化を目的の一とする。

【解決手段】剥離層を用いて基板から剥離された半導体素子層を、他基板に形成され、平坦化された無機絶縁層に覆われた半導体素子層上に積層する。上層の半導体素子層を基板より剥離後、剥離層を除去し半導体素子層下に形成される無機絶縁膜を露出する。平坦化された無機絶縁層及び無機絶縁膜を密着させて接合する。また、半導体素子層の有する半導体層は半導体基板より分離され、作製基板に転置された単結晶半導体層である。

(もっと読む)

不揮発性半導体メモリ

【課題】メモリセルの駆動電圧及びリーク電流を低減ができ、さらに、カップリング比を向上できる。

【解決手段】本発明の例に関わる不揮発性半導体メモリは、半導体基板内の素子分離領域によって分離される素子領域と、前記素子領域上に設けられるゲート絶縁膜2Aと、前記ゲート絶縁膜上に設けられる電荷蓄積層3Aと、電荷蓄積層3A上に設けられる多層絶縁体4Aと、多層絶縁体4A上に設けられるコントロールゲート電極5Aとを具備し、ゲート絶縁膜2Aは、第1トンネル膜21と、第1トンネル膜21よりも誘電率が高い第1高誘電率膜22と、第1トンネル膜21と同一構成の第2トンネル膜22を含み、多層絶縁体4Aは、第1絶縁膜41と、第1絶縁膜41よりも誘電率が高い第2高誘電率膜42と、第1絶縁膜41と同一構成の第2絶縁膜42とを含んでいることを備える。

(もっと読む)

201 - 220 / 596

[ Back to top ]