Fターム[5F083EP17]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 電荷蓄積機構 (5,261) | トラップ蓄積型 (2,146)

Fターム[5F083EP17]の下位に属するFターム

MNOS型(MONOS型を含む) (1,550)

Fターム[5F083EP17]に分類される特許

581 - 596 / 596

ナノ対応可能なメモリデバイスおよび異方性電荷運搬アレイ

ナノ対応可能なメモリデバイスおよび異方性電荷運搬アレイ用の方法および装置が、記載される。一局面において、メモリデバイスは、基板と、基板のソース領域と、基板のドレイン領域とを含む。ナノエレメントの集団が、基板上のチャネル領域より上に堆積される。このナノエレメントの集団は、一実施形態において、金属量子ドットを含む。トンネル誘電体層が、チャネル領域の上に横たわる基板上に形成され、金属マイグレーションバリア層が、誘電体層全体にわたって堆積される。ゲートコンタクトは、ナノエレメントの薄膜全体にわたって形成される。ナノエレメントは、横への電荷移動を低減できる。メモリデバイスは、シングルステートまたはマルチステートのメモリデバイスであり得る。複数の離散的なエネルギレベルを有する1つ以上の量子ドットまたは分子を備えるマルチステートメモリデバイスにおいて、そのデバイスを充放電する方法が開示される。  (もっと読む)

(もっと読む)

縦型EEPROMNROMメモリデバイス

【課題】電荷捕獲領域の重なりがなく、過消去特性が改善された、より狭い素子間隔の高密度なNROMメモリアレイを製造する方法及び構造体を提供する。

【解決手段】NOR又はNAND型高密度メモリ構成において縦型NROMメモリセル及び縦型選択ゲートを有効に利用するNROM EEPROMメモリデバイス及びアレイが開示される。本発明に係るメモリの実施形態では、縦型選択ゲート及び縦型NROMメモリセルを用いて、NOR及びNAND型NROM構成のメモリセル列、メモリセグメント及びメモリアレイを形成する。これらNROMメモリセル構成によって、構成要素として選択ゲートを有するメモリデバイス又はメモリアレイをより高密度にすることが可能となる。これらメモリデバイス又はメモリアレイにおいては、半導体製造プロセスによって作製可能な加工寸法を利用することができ、かつ、典型的なマルチビットNROMセルにおいて存在する電荷分離に関する問題を被ることがない。さらに、上述のメモリセル構造体は、NROMメモリセルからそれらに関連したビット/データ線及び/又はソース線とを絶縁する選択ゲートの後ろに、NROMメモリセルを配置することによって、擾乱及び過消去問題を軽減することが可能となる。

(もっと読む)

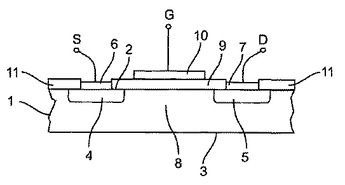

トンネル層に量子ドットを有するトランジスタ

本発明は、半導体本体(1)内に配置された半導体部品を記述したもので、前記半導体部品は、第1の導電型である少なくとも1つのソース領域(4)及び少なくとも1つのドレイン領域(5)を有し、ソース領域とドレイン領域の間に配置された第2の導電型である少なくとも1つの本体領域(8)を有し、絶縁層(9)により半導体本体から絶縁された少なくとも1つのゲート電極(10)を有し、前記絶縁層(9)は好ましくは焼結された一体化量子ドット含有層である。本発明は更に、量子ドット含有誘電性懸濁液が半導体本体に塗布され、次に例えば焼結によって一体化される上記の半導体部品の作製方法を記述する。  (もっと読む)

(もっと読む)

ブリッジ電界効果トランジスタメモリセル、上記セルを備えるデバイス、および、ブリッジ電界効果トランジスタメモリセルの製造方法

本発明は、第1および第2の各ソース/ドレイン領域、第1および第2の各ソース/ドレイン領域の間に配置されたチャネル領域とを備え、これらの各ソース/ドレイン領域とチャネル領域とが半導体ブリッジに形成されている、ブリッジ電界効果トランジスタメモリセルに関するものである。

本発明のメモリセルは、さらに、半導体ブリッジの少なくとも部分上に堆積されている電荷記憶層と、電荷記憶層の少なくとも一部上の金属性で導電性のゲート領域とを備え、電荷記憶層は、ブリッジ電界効果トランジスタメモリセルに所定の電気的電圧を印加することにより、選択的に、電気的な電荷キャリアが、電荷記憶層に対し導入されるように、または、電荷記憶層から除去されるように配置されている。  (もっと読む)

(もっと読む)

縦型スプリットゲートNROMメモリ装置及びその形成方法

【課題】NROMセルの利点と縦型メモリセルの利点とを備えるメモリデバイスを提供する。

【解決手段】スプリットゲート縦型NROMメモリセル(1890)は、複数の酸化物柱状体(1830、1831)から構成される。複数の酸化物柱状体の各々の上部にはソース/ドレイン領域(1840、1841)が形成される。溝部が、酸化物柱状体の各対の間に形成される。ポリシリコン制御ゲート(1800)が、酸化物柱状体の対の間の溝部に形成される。ポリシリコンプログラムゲート(1805、1806)が、制御ゲートと各酸化物柱状体との間に形成される。プログラムゲートは、各酸化物柱状体の側壁に沿って延在する。ゲート絶縁層(1802、1803)が、各プログラムゲートとその近傍の酸化物柱状体との間に形成される。各ゲート絶縁層は、少なくともひとつの電荷を捕獲する電荷捕獲構造を有する。一実施形態において、ゲート絶縁構造は、酸化物−窒化物−酸化物の層である。中間絶縁層(1822、1824)が、プログラムゲートと制御ゲートとの間に形成される。

(もっと読む)

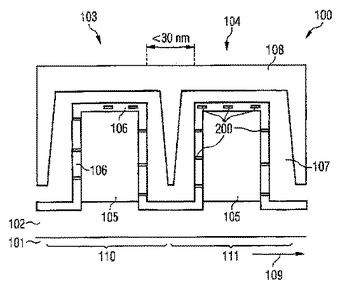

極薄シリコンにおけるNROM型フラッシュメモリデバイス

【課題】SOI技術を取り入れたCMOSデバイスにおける浮遊ボディの影響を抑制可能とする。

【解決手段】極薄シリコン・オン・インシュレータ構造においてNROMフラッシュメモリセルを実現する。平面型デバイスでは、ソース/ドレイン領域間のチャネルが通常時に完全空乏化されている。ソース/ドレイン領域と上方のゲート絶縁層との間に酸化物層を形成することで絶縁層を設ける。制御ゲートがゲート絶縁層の上部に形成される。縦型デバイスでは、ソース/ドレイン領域に側面が接する酸化物柱状体を基板から延伸させる。エピタキシャル再成長により、酸化物柱状体の側面に沿って極薄シリコンボディ領域が形成される。本構造の上部には、第2のソース/ドレイン領域が形成される。さらにその上部にゲート絶縁層及び制御ゲートが形成される。

(もっと読む)

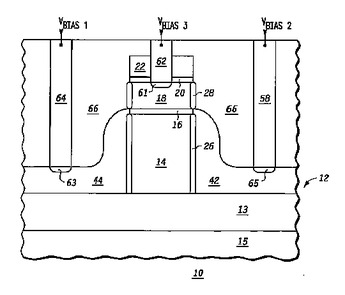

3つの電気絶縁電極を有するトランジスタ及びトランジスタの形成方法

トランジスタ(10)は別々に制御することができるゲート(44,42,18)を有するように形成される。3つのゲート領域は異なる電位でバイアスすることができ、かつこれらのゲート領域は異なる伝導特性を持つことができる。チャネルサイドウォール上の誘電体はチャネル上部の上の誘電体と異ならせることができる。ソース、ドレイン、及び3つのゲートとの電気コンタクトは別々に取る。ナノクラスター(143,144)のような電荷蓄積層をトランジスタのチャネルに隣接するように設け、そして電荷蓄積層を3つのゲート領域を通して制御することにより、揮発性メモリセル及び不揮発性メモリセルの両方を同じプロセスを使用して実現することにより世界共通のメモリプロセスを提供する。揮発性セルとして用いる場合、トランジスタの高さ、及びチャネルサイドウォール誘電体の特性によって記憶保持特性を制御する。不揮発性セルとして用いる場合、トランジスタの幅、及びチャネルを覆う誘電体の特性によって記憶保持特性を制御する。  (もっと読む)

(もっと読む)

過剰消去されたセルを復旧させるために、正のゲートストレスを使用したメモリデバイスおよびそのための方法

複数のメモリセルから構成されたフラッシュ電気的消去可能読出し専用メモリ(EEPROM)デバイス(10)の消去方法は、複数のメモリセル(10)をプリプログラミングするステップ(100)と、複数のメモリセル(10)に消去パルスを印加するステップ(110)と、を有し、これに消去検証(120)が続く。この消去検証(120)の後に、スレッショルド電圧が所定の最小レベル(VTMIN)を下回るメモリセルのソフトプログラミング(135)と、複数のメモリセル(10)への正のゲートストレスの印加(130)が続く。この消去方法は、過剰消去を防止し、スレッショルド電圧分布を低減する。  (もっと読む)

(もっと読む)

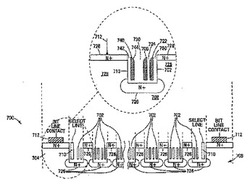

スタガー式ローカル接続構造を持つメモリセルアレイ

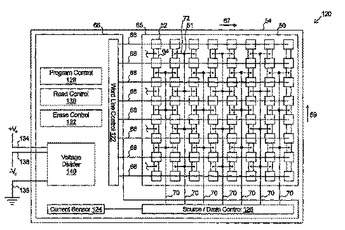

メモリセルアレイ(50)は、半導体基板(54)に製造された、2次元アレイのメモリセル(52)を含む。メモリセル(52)は、行方向(67)を形成する複数の行と、列方向(69)を形成する複数の列で並べられている。メモリセル(52)の各列は、複数の交互に配置されたチャネル領域(58)及びソース/ドレイン領域(64)を含む。各ソース/ドレイン領域(64)上には導電性インターコネクト(72)が配置されており、この導電性インターコネクト(72)はただ1つのその他のソース/ドレイン領域(64)に結合する。この1つのソース/ドレイン領域(64)とは、その列に隣接する第2の列に存在する領域である。導電性インターコネクト(64)は、1つおきの導電性インターコネクト(64)がその列の右側に隣接する列に接続するように、また、1つおきの導電性インターコネクトが、その列の左側に隣接する列に接続するように、配置される。複数のソース/ドレインコントロールライン(70)は、隣接するメモリセル(52)の列間に延在し、また、その隣接する列と列との間を結合する各導電性インターコネクト(72)に電気的に結合する。  (もっと読む)

(もっと読む)

不揮発性メモリデバイス

選択的な横方向の電導率を有する活性層を含むことができるメモリデバイスである。活性層は複数のナノ粒子を含む。 (もっと読む)

ナノクラスターを備えた半導体デバイス

ナノクラスターを備えたデバイスを形成するプロセス。本プロセスは、ナノクラスター(例えばシリコンナノ結晶)を形成する段階と、デバイスの誘電体を形成する次の段階中に酸化剤によるナノクラスターの酸化を抑制するためにナノクラスターを覆って酸化バリア層を形成する段階とを含む。酸化バリア層の少なくとも一部は、誘電体の形成後に除去される。1つの実施例では、本デバイスは、ナノクラスターがメモリの電荷蓄積トランジスタの電荷蓄積位置として利用されるメモリである。この実施例では、酸化バリア層が、メモリの高電圧トランジスタ用のゲート誘電体を形成することにより、ナノクラスターを酸化剤から保護する。 (もっと読む)

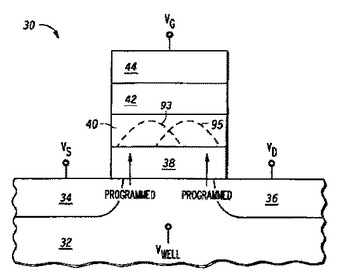

個別電荷蓄積素子を有するメモリのプログラミング

不揮発性メモリ(100)は、個別電荷蓄積素子(40)を有するトランジスタ群(30)から成るアレイを含む。トランジスタに対しては、2ステップ書き込み方法(60)を使用して書き込みを行ない、この方法では、第1ステップ(68)が低ゲート電圧によるホットキャリア注入(hot carrier injection:HCI)書き込みである。第2ステップ(78)を幾つかのメモリセルに対して選択的に利用して注入電荷分布を変え、トランジスタメモリセル内部の各メモリビットの間の電荷分布間隔を大きくする。書き込みを行なう第2ステップは、書き込み操作に長い余分な時間が加わることなく行われる。一の例では、第1ステップにおいて電子を注入し、そして第2ステップにおいてホールを注入する。2つのステップを実行して分布が形成される結果、蓄積媒体の中心部分の電子電荷が取り除かれる。  (もっと読む)

(もっと読む)

不揮発性メモリおよびその製造方法

トランジスタの制御ゲート(28)およびウェル領域(12)に、それぞれ、第1および第2の電圧を印加するステップを含む不揮発性メモリのトランジスタ(10)の電荷蓄積場所から放電するための方法。第1の電圧はトランジスタの制御ゲートに印加され、制御ゲートは、トランジスタの選択ゲート(18)に隣接して位置する一部を少なくとも有する。トランジスタは、制御ゲートの下に位置するトランジスタの構造の誘電体(22,26)内に配置されたナノクラスタ(24)を有する電荷蓄積場所を含む。最後に、第2の電圧が、制御ゲートの下に位置するウェル領域(12)に印加される。第1の電圧および第2の電圧の印加により、電荷蓄積場所のナノクラスタから電子を放出するために前記構造の両端に電圧差が発生する。  (もっと読む)

(もっと読む)

電界効果トランジスタ及びその製造方法

SiC基板1と、SiC基板1表面に形成されたソース3a及びドレイン3bと、SiC表面に接して形成され厚さが1分子層以上のAlN層5と、その上に形成されたSiO2層とを有する絶縁構造と、この絶縁構造上に形成されたゲート電極15とを有しており、SiCとの間の界面状態を良好に保ちつつ、リーク電流を抑制することができる。 (もっと読む)

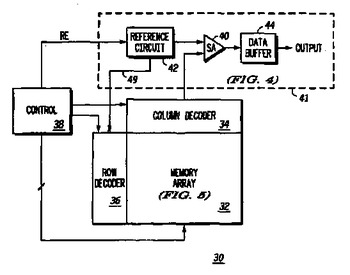

不揮発性メモリにおける基準トランジスタ用可変ゲート・バイアス

不揮発性メモリ(30)はナノクリスタルメモリセル(50、51、53)を備える。メモリセルトランジスタ(50、51、53)のプログラム及び消去閾値電圧は、プログラム/消去動作の回数の関数として上昇する。読み出し動作の間、基準トランジスタ(46)がセル電流と比較するための基準電流を供給する。基準トランジスタ(46)がナノクリスタルを含まないことを除いて、基準トランジスタ(46)は、メモリセルトランジスタ(50、51、53)を製造する際に用いるのと同様のプロセスで製造される。同様のプロセスを用いて基準トランジスタ(46)及びメモリセルトランジスタ(50、51、53)双方を製造することにより、基準トランジスタ(46)の閾値電圧は、メモリセルトランジスタ(50、51、53)の閾値電圧のずれに追従する。基準トランジスタ(46)のゲートにバイアスをかけるために、読み出し制御回路(42)が設けられている。読み出し制御回路(42)は、基準トランジスタ(46)のドレイン電流を検知し、基準電流をセル電流に対して実質的に一定値に維持するように、ゲートバイアス電圧を調節する。  (もっと読む)

(もっと読む)

電荷蓄積場所を有するメモリ

メモリは、チャネル領域(1725)を含む半導体構造(1105)の対向する側壁に隣接するゲート構造と、ゲート構造と対向する側壁との間にある複数の電荷蓄積場所(1713、1715、1709及び1711)とを有する。チャネル領域は、2つの電流端子領域間に配置され、それらの電流端子領域は一例ではソース/ドレイン領域としての役割を果たす。メモリセルは、メモリセルのアレイ(1801)内に実装することができ、一方のゲート構造が1つのワード線に結合され、他方のゲート構造が別のワード線に結合される。一例では、各セルは、それぞれが1ビットのデータを記憶する、4つの電荷蓄積場所を含む。  (もっと読む)

(もっと読む)

581 - 596 / 596

[ Back to top ]