Fターム[5F083EP56]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 絶縁膜 (4,144) | CG・FG間絶縁膜 (2,372) | 材料 (899)

Fターム[5F083EP56]に分類される特許

201 - 220 / 899

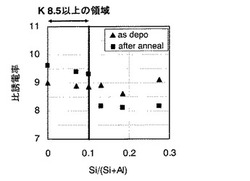

誘電体膜の製造方法

【課題】比誘電率の低下を軽減しつつリーク電流値を低減し、スパッタ率の低下による堆積速度の減少を抑制し、かつ、面内均一性に優れた誘電体膜の製造方法を提供すること。

【解決手段】本発明の一実施形態に係る誘電体膜の製造方法は、基板上に、AlとSiとOを主成分とする金属酸化物である誘電体膜を形成する誘電体膜の製造方法であって、Al元素とSi元素のモル比率Si/(Si+Al)が0<(B/(A+B))≦0.1であり、非晶質構造を有する金属酸化物を形成する工程と、該非晶質構造を有する金属酸化物に1000℃以上のアニール処理を施し、結晶相を含む金属酸化物を形成する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】不揮発性メモリを用いた半導体装置において、消去動作の高速化及び低消費電力化を実現する。

【解決手段】チャネル形成領域、トンネル絶縁膜及び浮遊ゲートを順に積層した不揮発性メモリにおいて、チャネル形成領域を酸化物半導体層により構成する。さらに、チャネル形成領域の下側に、浮遊ゲートと対向する位置に消去用の金属配線を設けた構造とする。上記構造により、消去動作において、浮遊ゲートに蓄積された電荷はチャネル形成領域を介して金属配線に引き抜かれる。これにより、半導体装置の消去動作を高速化し、低消費電力化を実現できる。

(もっと読む)

電界効果型トランジスタ、半導体メモリ、表示素子、画像表示装置及びシステム

【課題】比誘電率が高くリーク電流の少ない絶縁膜を提供する。

【解決手段】基板と、前記基板上に形成されたソース電極、ドレイン電極、及びゲート電極と、前記ゲート電極に所定の電圧を印加することによりソース電極とドレイン電極との間にチャネルが形成される半導体層を有し、前記ゲート電極と前記半導体層の間にゲート絶縁層と、を備え、前記ゲート絶縁層は、アルカリ土類金属の中から選ばれた1または2種類以上の元素と、Ga、Sc、Y、及びCeを除くランタノイドの中から選ばれた1または2種類以上の元素とを含むアモルファス複合金属酸化物絶縁膜により形成されていることを特徴とする電界効果型トランジスタを提供することにより上記課題を解決する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】

本発明は、コンタクトホールのアスペクト比の低減可能な半導体記憶装置及びその製造

方法を提供する。

【解決手段】

半導体基板11a上に形成された所定の間隔を隔てて設けられ、直列接続された複数の

メモリセルトランジスタM、複数の前記メモリセルトランジスタMの両端に形成された選

択ゲートトランジスタTを有する複数のNANDストリングと、隣接する前記NANDス

トリングの前記選択ゲートトランジスタT間に設けられたコンタクトプラグ18とを備え

、隣接する前記選択ゲートトランジスタT間の第1の方向における幅が前記メモリセルト

ランジスタMの前記ゲート長のk倍(kは自然数)と前記所定の間隔の(k+1)倍の総

和と等しい場合には、第1の方向における前記コンタクトプラグ18の幅は、前記メモリ

セルトランジスタMの前記ゲート長のk倍と前記所定の間隔の(k−1)倍の総和よりも

長いことを特徴とする半導体記憶装置。

(もっと読む)

半導体装置

【課題】記憶容量の大容量化に伴うメモリ誤動作の発生を抑制できる不揮発性メモリを含む半導体装置を提供すること。

【解決手段】半導体基板と、その表面に埋め込まれた素子分離絶縁膜と、該基板上の複数の不揮発性のメモリセルを備え、該メモリセルは、該基板上の第1絶縁膜、第1絶縁膜上の電荷蓄積層、電荷蓄積層上方の制御ゲート電極及び制御ゲート電極と電荷蓄積層の間の第2絶縁膜を備え、該メモリセルのチャネル幅方向の断面において、素子分離絶縁膜上面は該基板表面よりも高く且つ電荷蓄積層上面よりも低く、第2絶縁膜は素子分離絶縁膜上面及び電荷蓄積層上面上に設けられ、素子分離絶縁膜上面上の第2絶縁膜は電荷蓄積層上面上の第2絶縁膜よりも誘電率が低く且つ電荷蓄積層上面上の第2絶縁膜とは組成が異なる領域を含み及び複数の該メモリセルの隣接する該メモリセル間の素子分離絶縁膜上面上の制御ゲート電極は下に向かって突出している。

(もっと読む)

不揮発性メモリ

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】不揮発性メモリは、第1のトランジスタ20及び第2のトランジスタ21を有するメモリセルを有し、第1のトランジスタ20は第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタ21は酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタ160と、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】隣接メモリセル間の距離が縮小したときに、隣接メモリセル間で発生する問題を解決して信頼性を向上させる。

【解決手段】 半導体基板2上にゲート絶縁膜5を形成し、ゲート絶縁膜5上に電荷蓄積層6、中間絶縁膜7、および導電層8を順次形成し、導電層8、中間絶縁膜7および電荷蓄積層6に電極分離用の溝9を形成し、導電層8の上面及び側面、中間絶縁膜7の側面、電荷蓄積層6の側面、並びに、ゲート絶縁膜5の上面に窒化膜11を形成し、ゲート絶縁膜5の上面に形成された窒化膜11を除去し、電極分離用の溝9に絶縁膜10を埋め込むようにした。

(もっと読む)

半導体装置およびその製造方法

【課題】データ保持特性の良好な不揮発性メモリおよびその製造技術を提供する。

【解決手段】ゲート絶縁膜6上に多結晶シリコン膜7および絶縁膜8を順次堆積し、これら多結晶シリコン膜7および絶縁膜8をパターニングしてゲート電極7A、7Bを形成した後、ゲート電極7A、7Bの側壁に酸化シリコン膜からなるサイドウォールスペーサ12を形成する。その後、基板1上にプラズマCVD法で窒化シリコン膜19を堆積することにより、ゲート電極7A、7Bと窒化シリコン膜19とが直接接しないようにする。

(もっと読む)

MOS型半導体メモリ装置、その製造方法およびコンピュータ読み取り可能な記憶媒体

【課題】 電荷蓄積領域として機能する絶縁膜積層体のバンドギャップ構造を長期間維持し、優れたデータ保持特性と、高速でのデータ書換え性能と、低消費電力での動作性能と、高い信頼性と、を同時に兼ね備えたMOS型半導体メモリ装置を提供する。

【解決手段】 MOS型半導体メモリ装置601は、大きなバンドギャップを持つ第1の絶縁膜111および第5の絶縁膜115と、最も小さなバンドギャップを持つ第3の絶縁膜113との間に、両者の中間の大きさのバンドギャップを持つ第2の絶縁膜112および第4の絶縁膜114を備えている。第2の絶縁膜112と第3の絶縁膜113との間には、第1のブロック層112Bが設けられ、第3の絶縁膜113と第4の絶縁膜114との間には、第2のブロック層113Bが設けられている。

(もっと読む)

半導体装置の製造方法

【課題】素子分離絶縁膜上に引き出したワード線がシリサイド層形成時に断線するのを防止する。

【解決手段】メモリセルトランジスタを形成する領域の外側では、広い範囲にわたり素子分離絶縁膜2aが形成されている。素子分離絶縁膜2aの表面に、ワード線WLと直交する方向に溝状の凹部2bを複数本形成する。この上部にワード線WLを形成すると、凹部2b内にワード線WLを構成する第2導電膜である多結晶シリコン膜が埋め込まれる。ワード線WLを形成後に、ワード線上部にシリサイド層を形成する。このとき、シリサイド反応に必要なシリコンは凹部2b内から不足分が供給できるので、断線の発生を防止できる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタ160と、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成される。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置の特性の低下を抑制しつつ、メモリセルの微細化をはかった半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、基板101と、基板上に形成され、FN(Fowler-Nordheim)トンネル膜として機能するゲート絶縁膜111と、ゲート絶縁膜上に形成された第1の浮遊ゲート112と、第1の浮遊ゲート上に形成され、FNトンネル膜として機能する第1のゲート間絶縁膜113と、第1のゲート間絶縁膜上に形成された第2の浮遊ゲート114と、第2の浮遊ゲート上に形成され、電荷ブロック膜として機能する第2のゲート間絶縁膜115と、第2のゲート間絶縁膜上に形成された制御ゲート116とを備える。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能するp型の半導体層11と、チャネル領域を少なくとも囲み、活性領域21Bを定義する素子分離絶縁膜21と、活性領域21Bの一方に設けられたn型の第1主電極領域12と、活性領域21Bの他方に設けられたn型の第2主電極領域13と、活性領域21B上に設けられたゲート絶縁膜22と、ゲート絶縁膜22上において、第1主電極領域12と第2主電極領域13との間のチャネル領域を流れるキャリアの流路に直交する方向に伸延するゲート電極24とを備え、チャネル領域への前記キャリアの注入口が素子分離絶縁膜21から離間して設けられている。

(もっと読む)

半導体装置

【課題】素子特性の劣化を可及的に防止することのできる半導体装置を提供する。

【解決手段】半導体基板51と、半導体基板上に設けられたゲート絶縁膜53と、ゲート絶縁膜上に設けられた第1ゲート電極54aと、第1ゲート電極上に設けられ金属および酸素を含む電極間絶縁膜55と、電極間絶縁膜上に設けられた第2ゲート電極54bと、第1および第2ゲート電極の両側の半導体基板に設けられたソース/ドレイン領域58a、58bと、を備え、電極間絶縁膜55は、リン、砒素、アンチモン、ビスマスのうちから選択された少なくとも1つの添加元素を含み、その含有量が0.1at%以上3at%以下である。

(もっと読む)

トランジスタ,面状素子およびこれらの製造方法

【課題】トランジスタを比較的低温で製造する。

【解決手段】下部ゲート絶縁膜44をコントロールゲート42を構成する金属(アルミニウム)の酸化物により形成された下部酸化物層44aと自己組織化単分子膜により形成された下部SAM層44bとにより構成し、上部ゲート絶縁膜48をフローティングゲート46を構成する金属(アルミニウム)の酸化物により形成された上部酸化物層48aと自己組織化単分子膜により形成された上部SAM層48bとにより構成した。これにより、メモリセル40を比較的低温で製造することができる。

(もっと読む)

選択的プラズマ窒化処理方法及びプラズマ窒化処理装置

【課題】 シリコン表面とシリコン化合物層とが露出した被処理体に対して、選択的にシリコンを高い窒化レートと高い窒素ドーズ量でプラズマ窒化処理する方法を提供する。

【解決手段】 選択的プラズマ窒化処理は、処理圧力を66.7Pa以上667Pa以下の範囲内に設定し、載置台2の電極42に高周波電源44から被処理体の面積当り0.1W/cm2以上1.2W/cm2以下の高周波電力を供給して行う。この高周波電力によってウエハWへバイアス電圧が印加され、高いSi/SiO2選択比が得られる。

(もっと読む)

不揮発性半導体記憶装置及びその書き込み方法

【課題】書き込み速度の遅れや書き込み不良等を招くことなく、更なる微細化を実現し得る不揮発性半導体記憶装置及びその書き込み方法を提供する。

【解決手段】選択トランジスタとメモリセルトランジスタとを有する複数のメモリセルと、選択トランジスタのドレインに接続されたビット線と、メモリセルトランジスタのコントロールゲートに接続された第1のワード線と、選択トランジスタのセレクトゲートに接続された第2のワード線と、メモリセルトランジスタのソースに接続されたソース線とを有し、第1の電圧Vstep(1)を第1のワード線に印加しながら、ソース線に第2の電圧Vpulse(1)をパルス状に印加する第1のステップと、第1の電圧より高い第3の電圧Vstep(2)を第1のワード線に印加しながら、ソース線に第2の電圧より低い第4の電圧Vpulse(2)をパルス状に印加する第2のステップとを少なくとも実行することにより、メモリセルに情報を書き込む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】半導体基板の素子分離溝内の絶縁膜をエッチバック処理したときに側壁に残存する絶縁膜を除去して容量カップリングのロスを低減する。

【解決手段】シリコン基板1に、ゲート絶縁膜4、浮遊ゲート電極用の多結晶シリコン膜5、シリコン窒化膜8を積層形成する。所定間隔で複数のトレンチ1aを形成し、トレンチ1a内に素子分離絶縁膜2を埋め込み形成する。トレンチ1a内の素子分離絶縁膜2を所定深さまでエッチバックする。フォトレジストを全面に塗布してトレンチ1a底部が露光されにくい条件で露光し、トレンチ1aの底面部にレジスト10aを残す。レジスト10aをマスクとしてウェットエッチングでシリコン酸化膜をエッチングしてトレンチ1a内の側壁に残存する素子分離絶縁膜を除去する。

(もっと読む)

抵抗素子を有する半導体装置及びその製造方法

【課題】基準電圧を調整する回路を構成する抵抗素子を有するフラッシュ記憶素子である半導体装置及びその製造方法を提供する。

【解決手段】フラッシュ記憶素子である半導体装置の製造方法は、半導体基板上にトレンチを定義する鋳型パターンMLDPを形成し、鋳型パターンMLDP上にトレンチを横切る抵抗パターンRPを形成し、抵抗パターンRP上に互いに離隔された第1及び第2導電パターン210、220を形成し、第1及び第2導電パターン210、220に各々接続する第1及び第2配線UL1,UL2を形成する段階を有し、第1及び第2導電パターンUL1,UL2は鋳型パターンMLDPの上部に各々形成される。

(もっと読む)

201 - 220 / 899

[ Back to top ]