Fターム[5F083EP56]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 絶縁膜 (4,144) | CG・FG間絶縁膜 (2,372) | 材料 (899)

Fターム[5F083EP56]に分類される特許

161 - 180 / 899

不揮発性半導体記憶装置

【課題】ゲート電極間絶縁膜のリーク電流を抑制し、電気的信頼性を向上した不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板上に行列状に形成された複数のメモリ素子と、同一列方向のメモリ素子に選択的に接続される複数のビット線と、同一行方向のメモリ素子に接続される複数のワード線とを具備し、各メモリ素子は、半導体基板上に順次形成された第1のゲート絶縁膜、電荷蓄積層、第2のゲート絶縁膜、制御電極と、電荷蓄積層の対向する側面に沿って、前記シリコン基板上面に形成された1対の不純物注入層とを具備し、ビット線に垂直な方向に沿った断面における電荷蓄積層の上部コーナー部が曲面を有し、上部コーナー部が前記第1のゲート絶縁膜の上方にある。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、半導体装置の小型化を図ること。

【解決手段】第1の領域IにフラッシュメモリセルFLを形成する工程と、第2の領域IIにキャパシタQの第1の電極11aを形成する工程と、第2の絶縁膜14として第1の酸化シリコン膜14a、窒化シリコン膜14b、及び第2の酸化シリコン膜14cをこの順に形成する工程と、第1の電極11aの一部領域CRにおける窒化シリコン膜14bと第2の酸化シリコン膜14cとを除去する工程と、第3の領域IIIHにおける第1の絶縁膜10と第2の絶縁膜14とをウエットエッチングする工程と、キャパシタQの第2の電極30aを形成する工程と、一部領域CRにおける第1の酸化シリコン膜14aをエッチングして除去する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置

【課題】キャパシタを形成する領域の占有面積を縮小する。

【解決手段】本実施形態の半導体装置は、半導体基板10内に設けられた半導体領域AACと、半導体領域AAC内に設けられる複数のキャパシタCm,Cnを含むキャパシタ群と、を具備し、キャパシタCm,Cnのそれぞれは、半導体領域AAC上のキャパシタ絶縁膜42Aと、キャパシタ絶縁膜42A上のキャパシタ電極34Am,34Amと、キャパシタ電極34Am,34Amに隣接する拡散層32Aとを有し、を有し、キャパシタ電極34Am,34Anに接続される配線29m,29nのそれぞれは、キャパシタCm,Cn毎に電気的に分離され、キャパシタ電極Cm,Cnのそれぞれに異なる電位Vm,Vnが印加されている。

(もっと読む)

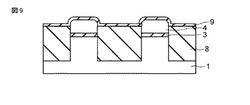

不揮発性半導体記憶装置とその製造方法

【課題】シリサイド層をゲート電極の一部に含む不揮発性半導体記憶装置において、シリサイド層の膜厚を制御することができる不揮発性半導体記憶装を提供する。

【解決手段】不揮発性半導体記憶装置は、チャネル半導体層上に、ゲート絶縁膜12、浮遊ゲート電極膜13、電極間絶縁膜14および制御ゲート電極15が順に積層されるメモリセルトランジスタMTを有する。制御ゲート電極15は、電極間絶縁膜14上に、半導体膜151、シリサイド相変化抑制膜152およびシリサイド膜154を順に積層した構造を有する。また、シリサイド相変化抑制膜152は、C,F,Nのうちの少なくともいずれか1つの元素が、1×1020〜5×1021[atom/cm3]の濃度範囲で添加された多結晶シリコン膜によって構成される。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル領域でシリサイドの成長速度を抑制しつつ、周辺回路領域では十分な量のシリサイドを形成することのできる不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板と、メモリセル領域に形成されたメモリセルトランジスタと、周辺回路領域に形成された電界効果トランジスタとを備える。メモリセルトランジスタは、半導体基板上に第1のゲート絶縁膜を介して形成された浮遊ゲート電極と、浮遊ゲート電極上に配置される第1の電極間絶縁膜と、第1の電極間絶縁膜上に配置される制御ゲート電極とを有する。制御ゲート電極は、積層された複数の導電膜により形成される。制御ゲート電極は、積層された複数の導電膜間の界面のうちの少なくとも1つに形成され金属原子の拡散を抑制するバリア膜を有する。制御ゲート電極は、その一部がシリサイド化されている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】半導体記憶装置を微細化した場合であっても、十分にカップリング比を高くする。

【解決手段】半導体記憶装置は、マトリクス状に配置されたメモリセルと複数のワード線16とを有する。メモリセル13は、行方向に複数個直列接続される。ワード線16は、複数のメモリセル13の制御ゲートを行方向と直交する列方向にそれぞれ接続する。メモリセル13の行方向の間隔は、第1の間隔と第1の間隔より広い第2の間隔とが交互に繰り返されている。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】第1のトランジスタと第2のトランジスタを有し、第1のトランジスタと第2のトランジスタとは少なくとも一部が重畳する第1のメモリセルと、第3のトランジスタと第4のトランジスタを有し、第3のトランジスタと第4のトランジスタとは少なくとも一部が重畳する第2のメモリセルと、駆動回路と、を有し、第2のメモリセルは、第1のメモリセル上に設けられ、第1のトランジスタは、第1の半導体材料を含んで構成され、第2のトランジスタ、第3のトランジスタ、および第4のトランジスタ、は、第2の半導体材料を含んで構成される半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】フローティングゲートとコントロールゲートとが積層されたスタック構造のゲート電極を有する半導体装置に関し、隣接メモリセル間やメモリセルとビット線との間における短絡不良を防止しうる半導体装置及びその製造方法を提供する。

【解決手段】トンネルゲート絶縁膜22上に、第1の幅を有する導電膜24、ONO膜28、コントロールゲート40を形成する。コントロールゲート40をマスクとして導電膜24をエッチングしてフローティングゲート26を形成した後、層間絶縁膜80を形成し、第1の方向の幅が第1の幅よりも広いコンタクトホール84を形成する。その後、コンタクトホール84の内壁に、サイドウォールスペーサ88を形成する。

(もっと読む)

フラッシュメモリアレイのワード線構造を保護するためのワード線保護装置およびフラッシュメモリアレイのためのワード線構造

【課題】製造中に、プロセスに関連する帯電からフラッシュメモリのワード線およびメモリセルを保護するための方法と構造とを与える。

【解決手段】ドープされたポリシリコンのワード線110aの端部にドープされていないポリシリコン110bが形成され、抵抗110bが生成される。これを通じて、プロセスにより生じる電荷が、基板に結合された、ドープされたポリシリコン放電構造110cへ放電される。ワード線抵抗110b、および、放電構造110cは、単一のパターニングされたポリシリコン構造として形成される。ワード線110aおよび放電部分110cは導電性になるように選択的にドープされ、また、抵抗部分110bは、製造後に通常のセル動作が可能なほどに十分高い抵抗が与えられる一方で、製造中にプロセスに関連する電荷に対しては放電路を供給するように、実質的にドープされない。

(もっと読む)

半導体記憶装置

【課題】本発明の実施形態は、ビット線の配線抵抗を低減させることができる半導体記憶装置を提供する。

【解決手段】実施形態によれば、それぞれが複数のメモリセルを有し第1方向に所定の間隔で設けられた複数のメモリセルユニットを有し、前記第1方向と交差する第2方向に配置された複数のメモリセルブロックと、前記第2方向に延在するとともに、前記第1方向に所定の間隔で設けられた複数の第1配線と、前記第1配線の上方、及び前記第1配線の下方の少なくともいずれかに設けられた第2配線と、前記第2配線の前記第2方向の両端部に設けられた前記第1配線と前記第2配線とを接続するコンタクトと、を備え、前記第2配線の前記第1方向に沿った幅寸法は、前記第1配線の前記第1方向に沿った幅寸法よりも長いことを特徴とする半導体記憶装置が提供される。

(もっと読む)

不揮発性記憶装置

【課題】基板の活性領域と制御ゲート電極との間の高い耐電圧特性を有する不揮発性記憶装置を提供する。

【解決手段】素子分離絶縁溝を有する基板と、前記基板上の前記素子分離溝の両側に形成された第1および第2のトンネル絶縁膜、第1および第2の浮遊ゲート電極と、前記第1および第2の浮遊ゲート電極の上面を覆い、かつ前記第1の浮遊ゲート電極と第2の浮遊ゲート電極との間、前記第1のトンネル絶縁膜と第2のトンネル絶縁膜との間、および前記素子分離絶縁溝の少なくとも上部を埋めるように形成されたゲート間絶縁膜と、前記ゲート間絶縁膜上に形成された制御ゲート電極と、を有する不揮発性記憶装置を提供する。前記ゲート間絶縁膜は、電子トラップ性を有する第1の絶縁材料からなる電子トラップ層と、前記第1の材料よりも電子トラップ性が低い第2の絶縁材料からなり、前記電子トラップ層を挟む第1および第2の絶縁層とを含む。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、ゲート絶縁層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

半導体記憶装置

【課題】動作信頼性を向上出来る半導体記憶装置を提供すること。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板10上に第1絶縁膜13を介在して形成された電荷蓄積層14と、電荷蓄積層14上に第2絶縁膜15を介在して形成された制御ゲート16とを具備し、制御ゲート16は、その少なくとも一部領域16−2において、その側面が外側に向かって膨らんだ形状を有し、制御ゲート16において側面が膨らみ始める部分から該制御ゲート16の頂上までの高さH1は、膨らみ始める部分より上の領域における制御ゲート16の最大幅W2_max2よりも大きい。

(もっと読む)

半導体装置

【課題】正確な抵抗値を有する抵抗素子を備える半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に配置された第1導電体と、第1方向における前記第1導電体の両端の上面に形成されたゲート間絶縁膜と、前記ゲート間絶縁膜が除去された第1接続領域を介して前記第1導電体に接続する第2導電体とを備える第1抵抗素子3−1と、前記半導体基板上に配置された第3導電体と、前記第1方向における前記第3導電体の両端の上面に形成された前記ゲート間絶縁膜と、前記ゲート間絶縁膜が除去された第2接続領域を介して前記第3導電体に接続する第4導電体とを備える第2抵抗素子3−2とを具備し、前記第1方向に沿った前記第2接続領域の長さは、前記第1接続領域の長さよりも長い(LEI2>LEI1)。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】書込・消去特性が高く、動作の信頼性が高い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板と、前記半導体基板上に設けられたトンネル絶縁膜と、前記トンネル絶縁膜上に設けられた第1電極と、前記第1電極上に設けられた電極間絶縁膜と、前記電極間絶縁膜上に設けられた第2電極と、を備える。前記電極間絶縁膜は、積層絶縁層と、前記積層絶縁層上に設けられ、前記積層絶縁層よりもバリアハイトが低い電荷蓄積層と、前記電荷蓄積層上に設けられ、前記電荷蓄積層よりもバリアハイトが高いブロック絶縁層と、を有する。前記積層絶縁層は、第1絶縁層と、前記第1絶縁層上に設けられ、前記第1絶縁層よりもバリアハイトが低い量子効果層と、前記量子効果層上に設けられ、前記量子効果層よりもバリアハイトが高い第2絶縁層と、を有する。

(もっと読む)

不揮発性記憶素子

【課題】本発明は、中間絶縁膜、半導体層、及びトンネル絶縁膜のうちの少なくとも1つが酸化ガリウムを含まない場合に比べて、動作安定性の向上した不揮発性記憶素子を提供する。

【解決手段】不揮発性記憶素子10は、基板30上と、ソース電極34S及びドレイン電極34Dと、半導体層36と、トンネル絶縁膜38と、電荷蓄積層40と、中間絶縁膜42と、ゲート電極44Gと、を備えており、半導体層36、トンネル絶縁膜38、及び中間絶縁膜42が、酸化ガリウムを含んでいる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜に酸素ドープ処理を行って、第1の絶縁膜に酸素原子を供給し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルに書き込み用のトランジスタ、読み出し用のトランジスタおよび選択用のトランジスタを備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】各メモリセルの書込消去特性を極力一定にできる不揮発性半導体記憶装置を提供する。

【解決手段】複数のメモリセルトランジスタMTは、活性領域Saが素子分離溝2によって互いに分離している。これらのメモリセルトランジスタMTは、それぞれ、活性領域Saの上面上または上方にトンネル絶縁膜3を介して電荷蓄積機能を有する電荷トラップ膜4を備えている。積層絶縁膜Bは、トンネル絶縁膜3および電荷トラップ膜4を少なくとも含んで構成され、トンネル絶縁膜3が素子分離溝2の内面に沿って形成されると共に電荷トラップ膜4がトンネル絶縁膜3の上面に沿って積層されており、素子分離溝2内の全領域に埋込まれている。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】多層配線構造を使って、キャパシタンスが大きく、かつキャパシタンス値が安定なキャパシタ素子を半導体基板上に集積化する。

【解決手段】多層配線構造18は、少なくとも第1層目の層間絶縁膜16と、第1層目の層間絶縁膜中に埋設された第1配線層と、を含み、第1配線層は、第1の電源に接続され前記第1の層間絶縁膜中に埋設された第1の配線パタ―ン15C1と、第2の電源に接続され前記第1の層間絶縁膜中に埋設された第2の配線パタ―ン15C2と、を含み、第1の配線パタ―ンと前記第2の配線パタ―ンとは容量結合して第1のキャパシタを形成し、第1の配線パタ―ンは積層配線パタ―ン13C上に形成されて、前記第4の電極パターン13Gと容量結合して第2のキャパシタを形成し、第4の電極パターンは第2の配線パタ―ンに電気的に接続されている。

(もっと読む)

161 - 180 / 899

[ Back to top ]