Fターム[5F083EP56]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 絶縁膜 (4,144) | CG・FG間絶縁膜 (2,372) | 材料 (899)

Fターム[5F083EP56]に分類される特許

881 - 899 / 899

半導体不揮発性記憶装置の製造方法

【課題】消去電圧などの動作電圧について低電圧化が可能であり、低コスト化が可能である半導体不揮発性記憶装置の製造方法を提供する。

【解決手段】電荷蓄積層を有するメモリトランジスタが接続された半導体不揮発性記憶装置の製造方法であって、ガラスあるいはプラスチックからなる絶縁性基板上にチャネル形成領域を有する半導体層を形成する工程と、前記半導体層の上層に電荷蓄積層を形成する工程と、前記電荷蓄積層の上方にコントロールゲートを形成する工程と、前記チャネル形成領域に接続するソース・ドレイン領域を形成する工程とを有し、前記メモリトランジスタとなる薄膜トランジスタを形成する。

(もっと読む)

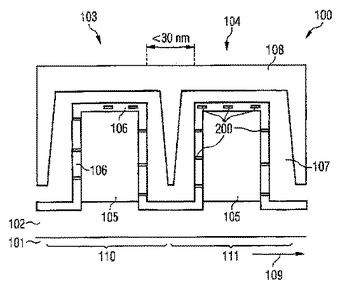

半導体装置の配線構造体及びその形成方法

【課題】 半導体装置の配線構造体およびその形成方法を提供する。

【解決手段】 この半導体装置は半導体基板100上に配置された層間絶縁膜、前記層間絶縁膜を貫通する第1コンタクト構造体181および第2コンタクト構造体182、前記層間絶縁膜上に配置されて前記第1コンタクト構造体と前記第2コンタクト構造体に連結される金属配線220を具備する。この際、前記第1コンタクト構造体は順次に積層された第1プラグおよび第2プラグ200を含み、前記第2コンタクト構造体は前記第2プラグを含む。

(もっと読む)

半導体装置及びその作製方法

【課題】本発明は、低コストで大量生産が可能である半導体装置及びその作製方法を提供する。また、非常に膜厚の薄い集積回路を用いた半導体装置、及びその作製方法を提供する。更には、低消費電力である半導体装置及びその作製方法を提供する。

【解決手段】本発明は、絶縁表面上に半導体不揮発性記憶素子トランジスタを有し、メモリトランジスタのフローティングゲート電極が、複数の導電性粒子又は半導体粒子で形成されていることを特徴とする半導体装置である。

(もっと読む)

スプリットゲート型のフラッシュメモリ素子及びその製造方法

【課題】 スプリットゲート型のフラッシュメモリ素子及びその製造方法を提供する。

【解決手段】 フローティングゲート及びコントロールゲートを形成する前に半導体基板上にマスクパターンを形成した後、マスクパターンの側壁によって自己整列されるようにフローティングゲート及びコントロールゲートを順次形成するスプリットゲート型のフラッシュメモリ素子。メモリセルを構成するフローティングゲートは、基板の主面に平行な第1面と、基板の主面に垂直である第2面と、第1面と第2面との間に延びているカーブ面を有する。コントロールゲートは、フローティングゲートの第1面の延長線とフローティングゲートの第2面の延長線との間で90゜より小さな角度範囲に限定される領域内で、前記フローティングゲートのカーブ面上に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】 マスクの枚数を増加することなく、かつ、汚染することなく膜厚の異なるゲート絶縁膜を備えた半導体装置の製造方法を提供する。

【解決手段】 メモリセル領域Mに複数のアシストゲート電極部21が互いに間隔を隔てて形成される。周辺回路領域Pでは平坦な半導体基板1の表面が露出する。次に、所定の条件のもとで、露出している半導体基板1の表面に酸化処理が施される。平坦な周辺回路領域Pに露出する半導体基板1の表面に供給される酸素ラジカルの量と比べると、メモリセル領域Mでは、アシストゲート電極部21によって挟まれていることで、露出している半導体基板1の表面にまで供給される酸素ラジカルの量は少なくなる。その結果、メモリセル領域Mに形成されるフローティングゲート酸化膜8aの膜厚は、周辺回路領域Pに形成されるゲート酸化膜10の膜厚よりも薄くなる。

(もっと読む)

不揮発性半導体記憶装置

【課題】 複数のスタックゲート型メモリセルを含むフラッシュメモリにおいて、消去前書込動作を不要とすることにより一括消去動作に要する時間を短縮し、データの書換動作に要する時間も短縮することである。

【解決手段】 消去時に、複数のメモリセルのソース1003からフローティングゲート1005に同時に電子を注入する。それにより、複数のメモリセルのしきい値電圧が上昇する。プログラム時に、選択されたメモリセルのフローティングゲート1005からドレイン1002に電子を放出する。それにより、選択されたメモリセルのしきい値電圧が下降する。

(もっと読む)

半導体装置及びその製造方法

【課題】リーク電流を改善した高誘電率絶縁膜を電極間絶縁膜として使用する半導体装置及びその製造方法を提供することである。

【解決手段】半導体装置は、半導体基板上に形成された第1の絶縁膜と、前記第1の絶縁膜上に形成された第1のゲート電極と、前記第1のゲート電極の上方に形成された第2のゲート電極と、前記第1のゲート電極と第2のゲート電極との間に挟まれた結晶化した第2の絶縁膜を具備することを特徴とする。

(もっと読む)

不揮発性半導体メモリ装置

【課題】 正負両極のいずれの高電界においてもリーク電流を低減することができ、且つ単独の高誘電体膜では困難な低電界から高電界の広い電界領域でリーク電流を抑制する。

【解決手段】 第1導電型の半導体基板10の主面上にトンネル絶縁膜11を介して選択的に形成されたフローティングゲート電極12と、フローティングゲート電極12上に電極間絶縁膜13を介して形成されたコントロールゲート電極14と、各ゲート電極12,14に対応して基板の主面に形成された第2導電型のソース・ドレイン領域15とを備えた不揮発性半導体メモリ装置であって、電極間絶縁膜13は、2種類以上の高誘電体材料13a,13b,13cによる3層以上の積層構造を有する。

(もっと読む)

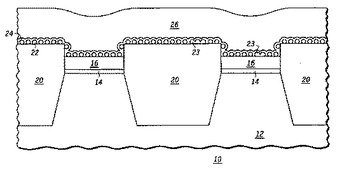

分離領域上に消去ゲートを有する不揮発性メモリ

本発明は、不揮発性メモリ装置及びそのような装置の製造方法を提供する。この装置は、浮遊ゲート(16)と、制御ゲート(19)と、分離した消去ゲート(10)とを備える。消去ゲート(10)は、基板(1)内に設けられた分離領域(2)中に、又はその上に設けられる。そのため消去ゲート(10)は、セル・サイズを増加させない。消去ゲート(10)と浮遊ゲート(16)との間の容量は、制御ゲート(19)と浮遊ゲート(16)との間の容量に比べて小さく、消去ゲート(10)と浮遊ゲート(16)との間の酸化物層を介してファウラー・ノルドハイム・トンネルによって浮遊ゲート(16)の帯電が消去される。  (もっと読む)

(もっと読む)

ナノ構造単層の形成方法および形成デバイスならびにかかる単層を含むデバイス

ナノ構造配列の形成またはパターニング法が提供される。この方法は、ナノ構造会合基を含んでなるコーティング上での配列形成、レジストを使用するパターニングおよび/または配列形成を促進するデバイスの使用を含む。またナノ構造配列を含むデバイス(例えばメモリーデバイス)のように、ナノ構造配列の形成のための関連デバイスも提供される。 (もっと読む)

改良された表面形状を用いるメモリ構造の形成方法及びその構造。

半導体装置10のゲートカップリング比を増大させるため、超微細結晶等の個別素子22が浮遊ゲート16上に析出される。一実施形態において、個別素子22は、蒸気相中で予め形成され、静電気力によって半導体装置10に吸着される。一実施形態において、個別素子22は、それらが吸着されるチャンバとは異なるチャンバ内で予め形成される。更に別の実施例において、同じチャンバが全ての析出工程に使用される。界面層17は、必要に応じて、浮遊ゲート16と個別素子22との間に形成される。  (もっと読む)

(もっと読む)

ブリッジ電界効果トランジスタメモリセル、上記セルを備えるデバイス、および、ブリッジ電界効果トランジスタメモリセルの製造方法

本発明は、第1および第2の各ソース/ドレイン領域、第1および第2の各ソース/ドレイン領域の間に配置されたチャネル領域とを備え、これらの各ソース/ドレイン領域とチャネル領域とが半導体ブリッジに形成されている、ブリッジ電界効果トランジスタメモリセルに関するものである。

本発明のメモリセルは、さらに、半導体ブリッジの少なくとも部分上に堆積されている電荷記憶層と、電荷記憶層の少なくとも一部上の金属性で導電性のゲート領域とを備え、電荷記憶層は、ブリッジ電界効果トランジスタメモリセルに所定の電気的電圧を印加することにより、選択的に、電気的な電荷キャリアが、電荷記憶層に対し導入されるように、または、電荷記憶層から除去されるように配置されている。  (もっと読む)

(もっと読む)

高K誘電体膜

誘電体層(14,22,24,32)は、ランタン、ルテチウム、及び酸素により構成され、かつ2つの導体の間、または導体(14,20,34)と基板(12,26,30)との間に形成される。一の実施形態では、誘電体層は基板を覆って形成され、境界層を追加する必要がない。別の実施形態では、誘電体層(22,42,46)に含まれる元素の分布は、ランタン含有量またはルテチウム含有量に関して傾斜する、または誘電体層(22,42,46)は別の構成として、アルミニウムを含むことができる。更に別の実施形態では、絶縁層を導体または基板と誘電体層との間、または導体及び基板の両方と誘電体層との間に形成する。誘電体層は、分子ビームエピタキシー法によって形成することが好ましいが、原子層化学気相成長、物理気相成長、有機金属化学気相成長、またはパルスレーザ堆積によって形成することもできる。  (もっと読む)

(もっと読む)

半導体装置と半導体装置の製造方法

バリア性を有する絶縁膜サイドウォールスペーサを有する半導体装置を提供する。 半導体装置は、半導体基板の上に形成されたゲート酸化膜とゲート電極と;半導体基板内に形成されたソース/ドレイン領域と;ゲート電極側壁上に形成された2層以上の積層サイドウォールスペーサであって、最外層以外の層として窒化膜を含み、最外層は、酸化膜又は酸化窒化膜で形成され、下面が半導体基板またはゲート酸化膜、又は窒化膜以外の他のサイドウォールスペーサ層と接している第1積層サイドウォールスペーサと;を有する。さらに、不揮発性メモリの積層ゲート電極構造と;積層ゲート電極構造の側壁上に形成され、中間層として半導体基板に接しない窒化膜を含む3層以上の第2積層サイドウォールスペーサと;を有することもできる。  (もっと読む)

(もっと読む)

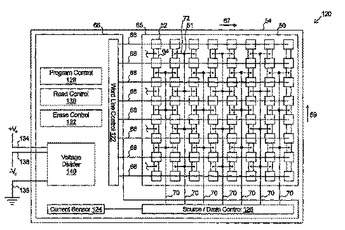

スタガー式ローカル接続構造を持つメモリセルアレイ

メモリセルアレイ(50)は、半導体基板(54)に製造された、2次元アレイのメモリセル(52)を含む。メモリセル(52)は、行方向(67)を形成する複数の行と、列方向(69)を形成する複数の列で並べられている。メモリセル(52)の各列は、複数の交互に配置されたチャネル領域(58)及びソース/ドレイン領域(64)を含む。各ソース/ドレイン領域(64)上には導電性インターコネクト(72)が配置されており、この導電性インターコネクト(72)はただ1つのその他のソース/ドレイン領域(64)に結合する。この1つのソース/ドレイン領域(64)とは、その列に隣接する第2の列に存在する領域である。導電性インターコネクト(64)は、1つおきの導電性インターコネクト(64)がその列の右側に隣接する列に接続するように、また、1つおきの導電性インターコネクトが、その列の左側に隣接する列に接続するように、配置される。複数のソース/ドレインコントロールライン(70)は、隣接するメモリセル(52)の列間に延在し、また、その隣接する列と列との間を結合する各導電性インターコネクト(72)に電気的に結合する。  (もっと読む)

(もっと読む)

2−トランジスタメモリセル及びその製造方法

本発明は、メモリゲートスタック(1)を有する記憶トランジスタ(1)及び選択トランジスタを有する2-トランジスタメモリセルを基板(50)上に製造する方法であって、トンネル誘電層(51)が前記基板(50)と前記メモリゲートスタック(1)との間にもたらされる方法を提供する。前記方法は、第一の導電層(52)及び第二の導電層(54)をもたらし、前記第二の導電層(54)をエッチし、それによってコントロールゲートを形成し、前記第一の導電層(52)をエッチし、それによってフローティングゲートを形成することによって前記メモリゲートスタック(1)を形成するステップを有する。前記方法は更に、前記第一の導電層(52)がエッチされる前に、前記トンネル誘電層(51)の下に形成されるべきチャネルの方向で前記コントロールゲートに対してスペーサ(81)を形成するステップと、その後、前記第一の導電層(52)をエッチするために前記スペーサ(81)をハードマスクとして使用し、それによって前記フローティングゲートを形成し、それによってフローティングゲートをコントロールゲートに自己整合させるステップとを有することを特徴とする。本発明は、前記コントロールゲート(54)は前記フローティングゲート(52)よりも小さくなり、スペーサ(81)が、前記コントロールゲート(54)に隣接してもたらされるメモリセルも提供する。  (もっと読む)

(もっと読む)

不揮発性メモリ装置を製造する方法及びそれによって得られるメモリ装置

本発明は、ダブル・ゲート・スタック及びシングル・アクセス・ゲートを備える不揮発性メモリ・セル(50)を加工する方法に関する。この方法は、アクセス・ゲートを加工する方法を、自己整合的な、ソース注入とは別のドレイン注入と組み合わせる。本発明の方法は、マスク位置合せ精度を考慮せずに、メモリ装置を消去するための延長されたドレインを自己整合的に注入することを可能にする。さらに、この方法は、さらなるマスクを使用せずにドレイン及びソース注入を互いに異なるドーピングで実施する方法を提供する。  (もっと読む)

(もっと読む)

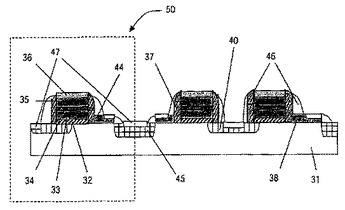

フラッシュメモリデバイスの特性を改善する方法

半導体デバイスを製造する方法において、シリコン基板(62)上にゲート酸化膜(60)を提供する。このゲート酸化膜(60)上に第1ポリシリコン層(64)を提供し、第1ポリシリコン層(64)上に絶縁層(66)を提供し、またこの絶縁層(66)上に第2ポリシリコン層(68)を提供する。適切なマスキングを実行した後にエッチングステップが実行されると、シリコン基板を露出させ、かつこのシリコン基板上にスタックゲート構造を形成すべく、第2ポリシリコン層、絶縁層、第1ポリシリコン層、およびゲート酸化膜の一部を除去するようにこれらの層がエッチングされる。スタックゲート構造(72)上に薄い酸化膜(80)を成長させるべく、短時間(例えば10秒から20秒)の急速熱アニールを実行する。それから、急速熱アニールによって形成された酸化膜(80)上に第2酸化膜(82)をたい積する。

(もっと読む)

(もっと読む)

半導体装置および半導体記憶装置

【課題】本発明は、素子間分離にSTI構造を採用する不揮発性半導体記憶装置において、ソース領域をより確実に接続できるようにすることを最も主要な特徴とする。

【解決手段】たとえば、P型シリコン基板11の表面部に、浅い第一の埋め込み素子分離絶縁膜22と、この第一の埋め込み素子分離絶縁膜22よりも深い、第二の埋め込み素子分離絶縁膜23とからなる素子分離領域24を形成する。そして、第一の埋め込み素子分離絶縁膜22を除去した後に、その底部とメモリセルトランジスタのソース領域とに不純物をイオン注入する。こうして、第一の埋め込み素子分離絶縁膜22のアスペクト比を下げ、トレンチ溝の側壁部分に対しても十分に拡散層を形成できるようにすることで、ソース線SLとなる、連続したN+ 型ソース領域19の形成を可能とする構成となっている。

(もっと読む)

881 - 899 / 899

[ Back to top ]