Fターム[5F083EP56]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 絶縁膜 (4,144) | CG・FG間絶縁膜 (2,372) | 材料 (899)

Fターム[5F083EP56]に分類される特許

121 - 140 / 899

不揮発性記憶素子及びその製造方法

【課題】 信頼性を向上可能な不揮発性記憶素子及びその製造方法を提供する。

【解決手段】 不揮発性素子は、基板100、基板100の上に形成され、制御ベースゲート120a及び制御ベースゲート120aの上に形成される制御金属ゲート125anを有する制御ゲート電極137、制御ゲート電極137と基板100との間に形成される電荷格納領域110a、制御ゲート電極137の上に形成される制御ゲートマスクパターン130、及び制御ゲートマスクパターン130及び制御ベースゲート120aの間に形成された制御金属ゲート125aの側壁の上に形成される酸化防止スペーサ135aを備える。このとき、制御金属ゲート125anの幅は、制御ゲートマスクパターン130の幅より小さくなるように形成されている。これにより、制御金属ゲート125anが酸化工程又は酸化物等によって酸化されることを防止することができる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】浮遊ゲート電極の細りを補償して信頼性を向上させた不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置10では、第1の幅W1を有する活性領域12が、半導体基板11の主面に形成された素子分離層13で分離されている。第1ゲート絶縁膜14が、活性領域12に形成されている。第1の幅W1より狭い第2の幅W2を有する第1導電層15aが、第1ゲート絶縁膜14を介して活性領域12に形成されている。第1の幅W1と第2の幅W2の差を補償するように第3の幅W3を有する第2導電層15aが第1導電層15aの側壁に形成されている。第1ゲート電極15は、第1導電層15aと第2導電層15bを含んでいる。第2ゲート絶縁膜16が、第1ゲート電極15および素子分離層13上にコンフォーマルに形成されている。第2ゲート電極17が、第2ゲート絶縁膜16上に形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離溝を塗布系の材料で埋め込む素子分離構造において、熱処理時に素子分離溝に大きな応力が作用することを防止する。

【解決手段】メモリセル領域に形成され第1の開口幅を有する第1の素子分離溝と、周辺回路領域に形成され第1の開口幅より大きい第2の開口幅を有する第2の素子分離溝と、第1の素子分離溝の内面に形成された第1の酸化膜と、第1の酸化膜上に形成されて前記第1の素子分離溝内に埋め込まれた第1の塗布型酸化膜と、第2の素子分離溝の内面のうちの側部に形成された第2の酸化膜と、第2の素子分離溝内の内面のうちの底部上に形成された第3の酸化膜と、第3の酸化膜上に形成されて第2の素子分離溝内に埋め込まれた第2の塗布型酸化膜とを備えた。

(もっと読む)

半導体記憶装置

【課題】チャネル領域にソース領域及びドレイン領域を形成せずに、信頼性が高い動作が可能な半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、第1の方向に延びる同一導電形のチャネル領域と、チャネル領域上に設けられた第1の絶縁膜と、第1の絶縁膜上に設けられた複数の浮遊ゲートと、浮遊ゲートの上に設けられた第2の絶縁膜と、第2の絶縁膜の上に設けられた制御ゲートとを備えている。複数の浮遊ゲートは第1の方向及びこれに交差する第2の方向に分断されている。制御ゲートは第1の方向に対して交差する第2の方向に延びている。浮遊ゲートのフリンジ電界によって、第1の方向で隣り合う浮遊ゲート間の下のチャネル領域の表面に反転層が形成される。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】空隙AG1の埋め込み絶縁膜4が除去される前に側壁保護膜3´にてトンネル絶縁膜5の側壁を覆うことにより、埋め込み絶縁膜4とトンネル絶縁膜5との間でウェット処理のエッチング選択比が確保できない場合においても、トンネル絶縁膜5を保護できるようにする。

(もっと読む)

半導体基板の作製方法

【課題】半導体基板の欠陥を低減する。また、歩留まり高く欠陥の少ない半導体基板を作製する。また、歩留まり高く半導体装置を作製する。

【解決手段】支持基板に酸化絶縁層を介して半導体層を設け、該半導体層の端部における、支持基板及び酸化絶縁層の密着性を高めた後、半導体層の表面の絶縁層を除去し、半導体層にレーザ光を照射して、平坦化された半導体層を得る。半導体層の端部において、支持基板及び酸化絶縁層の密着性を高めるために、半導体層の表面から、レーザ光を照射する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】電極間絶縁膜7下において、埋め込み絶縁膜9が上下に分離されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、空隙AG1にて分離された上側の埋め込み絶縁膜9は電極間絶縁膜7下に積層し、下側の埋め込み絶縁膜9はトレンチ2内に配置する。

(もっと読む)

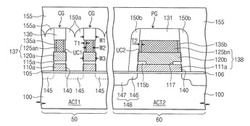

半導体装置及び半導体記憶装置

【課題】データの保持期間を長くする半導体装置又は半導体記憶装置を提供する。

【解決手段】一対の不純物領域を有する第1の半導体層152aと、第1の半導体層と同じ材料であり、第1の半導体層と離間する第2の半導体層152bと、第1、第2の半導体層の上に設けられた第1の絶縁層153と、第1の絶縁層153を介して第1の半導体層に重畳する第1の導電層154と、第1の絶縁層153を介して第1の導電層に重畳し、第1の半導体層と異なる材料である第3の半導体層156と、第1の導電層及び第3の半導体層に電気的に接続される第2の導電層157bと、第3の半導体層156に電気的に接続され、第2の導電層と同じ材料である第3の導電層157aと、第3の半導体層、第2の導電層、及び第3の導電層の上に設けられた第2の絶縁層158と、第2の絶縁層を介して第3の半導体層に重畳する第4の導電層159と、を含む。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】レンチ2内に埋め込まれた埋め込み絶縁膜3の一部を除去することで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1を形成し、空隙AG1は、制御ゲート電極8下に潜るようにしてトレンチ2に沿って連続して形成する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】トレンチ2内に埋め込まれた第2の埋め込み絶縁膜4の一部が除去されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、浮遊ゲート電極6間が完全に埋め込まれないようにして制御ゲート電極8間にカバー絶縁膜10が掛け渡されることで、ビット線方向にDBに隣接する浮遊ゲート電極6間に空隙AG2が形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】柱状のチャネル層となる半導体層に沿って、複数の浮遊ゲート型の不揮発性メモリセルが積層された構造の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、柱状の半導体膜131の側面にトンネル誘電体膜141、浮遊ゲート電極膜142、ゲート間絶縁膜143および制御ゲート電極膜144を備えるメモリセルMCが半導体膜131の延在方向に複数設けられるメモリセル列を、半導体基板101上に略垂直に複数配置した不揮発性半導体記憶装置が提供される。ここで、浮遊ゲート電極膜142と制御ゲート電極膜143は、柱状の半導体膜131の全周のうち特定の方向の側面にのみ形成されている。

(もっと読む)

半導体メモリ及びその製造方法

【課題】半導体メモリの構造の簡略化と製造プロセスの簡易化とを実現する。

【解決手段】半導体基板と、半導体基板内に形成され、かつ互いに直交する第1及び第2の方向にそれぞれ延在する第1及び第2のソース領域104、109とを有する半導体メモリ。第1及び第2のソース領域はそれぞれ拡散領域であって、交差する部分で電気的に接続されている。また半導体メモリは、第2のソース領域109と同一方向に延在するビットライン108と、第2のソース領域109上に形成されたソースラインとを有し、ソースラインと第2のソース領域109とのコンタクトと、ビットライン108と半導体基板内に形成されたドレイン領域とのコンタクトとは直線状に配置されている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】書き込み特性の向上を図る。

【解決手段】半導体記憶装置の製造方法は、基板10上に、トンネル絶縁膜11を形成し、前記トンネル絶縁膜上に、導電体で構成される電荷蓄積層12を形成し、前記電荷蓄積層、前記トンネル絶縁膜、および前記基板を加工して、前記基板内に、前記電荷蓄積層および前記トンネル絶縁膜を分離する素子分離溝22を形成し、前記素子分離溝内に、上面が前記電荷蓄積層の下面より高く上面より低くなるように素子分離絶縁膜13を埋め込み、前記電荷蓄積層の表面に形成された自然酸化膜30を除去し、前記素子分離絶縁膜および前記電荷蓄積層の表面に、絶縁膜14を形成し、前記自然酸化膜の除去から前記絶縁膜の形成までが、その内部の酸素濃度がコントロールされた製造装置内で行われる。

(もっと読む)

シリコン酸化膜の形成方法、シリコン窒化膜の形成方法、シリコン酸窒化膜の形成方法

【課題】ポリシリコン上において高品質な絶縁膜を形成できる絶縁膜の形成方法を提供する

【解決手段】シリコン酸化膜の形成方法は、基板上にポリシリコン膜を堆積する工程と、

前記ポリシリコン膜の表面を、酸素を含むガスとKrガスを主体とする不活性ガスとよりなる混合ガスにマイクロ波によりプラズマを励起することで形成される原子状酸素O*に曝すことにより、前記ポリシリコン膜の表面にシリコン酸化膜を形成する工程とよりなる。

(もっと読む)

半導体装置およびその製造方法

【課題】 エアギャップ構造を簡易な方法で形成する。

【解決手段】 本発明の一態様の半導体装置の製造方法によれば、半導体基板上に導電層を含む被加工膜を形成する工程と、前記被加工膜上にダミー膜を形成する工程と、を備えている。さらに、前記ダミー膜を所望の形状にデポ条件の異方性エッチングにより加工する工程と、前記被加工膜を所望の形状に異方性エッチングにより加工する工程と、前記所望の形状に加工された被加工膜上の前記ダミー膜を異方性エッチングにより除去する工程と、前記被加工膜上に上層膜を形成する工程と、を備えている。

(もっと読む)

半導体装置の製造方法

【課題】フラッシュメモリセルと低電圧動作トランジスタや高電圧動作トランジスタを集積化し、異種トランジスタを混載する半導体装置の製造法を提供する。

【解決手段】半導体装置の製造方法は、(a)トンネル絶縁膜、Fゲート電極膜、電極間絶縁膜を堆積したFゲート電極構造を形成し(b)ゲート絶縁膜を形成し(c)導電膜、エッチストッパ膜を堆積し(d)エッチストッパ膜、導電膜をエッチングした積層ゲート電極構造を形成し(e)積層ゲート電極構造の側壁上に第1絶縁膜を形成し(f)積層ゲート電極側壁上に第1サイドウォールスペーサ層を形成し(g)エッチストッパ層を除去し(h)他の領域の導電層から、ゲート電極構造を形成し(i)積層ゲート電極構造、ゲート電極構造側壁上に第2サイドウォールスペーサを形成し(j)希弗酸水溶液で半導体基板表面を露出し(k)半導体基板表面にシリサイド層を形成する。

(もっと読む)

半導体記憶装置

【課題】メモリデータを外部回路を用いずに、コピーを行う半導体記憶装置を提供することを課題とする。

【解決手段】複数のメモリセルの第一端子が共通接続されたビット線と、ビット線に接続され、読み出し時にビット線を特定の電位にプリチャージするプリチャージ回路と、メモリセルから読み出したデータ、もしくはメモリセルへの書き込みデータを一時的に保持する容量素子を有するデータ保持回路と、データ保持回路で保持しているデータの反転データをビット線に出力する反転データ出力回路とを有し、反転データ出力回路は、データ保持回路で保持しているデータの反転データの出力を制御する手段を有する構成とする。

(もっと読む)

半導体不揮発性メモリ装置

【課題】トンネル絶縁膜にエッジ部があることによるトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】トンネル絶縁膜の上部であって、トンネル領域のエッジ部から離間した位置に、電荷受け渡し用電極を配置し、電荷受け渡し用電極とフローティングゲート電極とが、電気的に接続されるようにした。

(もっと読む)

不揮発性半導体装置および不揮発性半導体装置の製造方法

【課題】不揮発性半導体装置の機能を確保することができ、フローティングゲートのしきい値電圧の変動が抑制された不揮発性半導体装置を提供する。

【解決手段】主表面を有する半導体基板11と、半導体基板11の主表面上に間隔をあけて形成された第1と第2フローティングゲート15a、15bと、第1と第2フローティングゲート15a、15b上の第1と第2コントロールゲート12a、12bと、第1コントロールゲート12a上に形成された第1絶縁膜32aと、第2コントロールゲート12b上に形成され、第1絶縁膜32aに接触するように形成された第2絶縁膜32bと、第1絶縁膜32aと、第2絶縁膜32bとを接触させることで、少なくとも第1フローティングゲート15aと第2フローティングゲート15b間に形成された空隙部26aとを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去電圧を低減させることができる半導体記憶装置を提供することを課題とする。

【解決手段】チャネル形成領域を有する半導体膜と、半導体膜のチャネル形成領域上に、第1の絶縁層、浮遊ゲート電極、第2の絶縁層、制御ゲート電極を設ける。浮遊ゲート電極材料には、半導体基板よりも仕事関数があまり大きくならない窒化チタンとすることにより、消去電圧低減を図ったものである。なお、上記窒化チタンのチタン組成比は、低消費電力化及び誤書き換え耐性の観点から56atomic%以上75atomic%以下がよい。

(もっと読む)

121 - 140 / 899

[ Back to top ]