Fターム[5F083ER13]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 電子放出 (1,246)

Fターム[5F083ER13]の下位に属するFターム

トンネル放出 (407)

ドレイン側へ放出 (115)

ソース側へ放出 (92)

CGへ放出 (79)

CG以外のゲートへ放出 (25)

チャネルへ放出 (411)

ソース/ドレインを除く拡散領域へ放出 (2)

Fターム[5F083ER13]に分類される特許

41 - 60 / 115

半導体装置、及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供することを課題の一とする。また、信頼性の高い半導体装置の作製方法を提供することを課題の一とする。また、消費電力が低い半導体装置を提供することを課題の一とする。また、消費電力が低い半導体装置の作製方法を提供することを課題の一とする。また、量産性の高い半導体装置を提供することを課題の一とする。また、量産性の高い半導体装置の作製方法を提供することを課題の一とする。

【解決手段】酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すれば良い。具体的には、酸化物半導体層にハロゲン元素を添加した後に加熱処理を施し、不純物を除去して使用すれば良い。ハロゲン元素としては、フッ素が好ましい。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位変換回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のトランジスタ160と、第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成され、第1のトランジスタ160のゲート電極と、第2のトランジスタ162のソース・ドレイン電極とは、電気的に接続され、第1の配線と、第1のトランジスタ160のソース電極とは、電気的に接続され、第2の配線と、第1のトランジスタ160のドレイン電極とは、電気的に接続され、第3の配線と、第2のトランジスタ162のソース・ドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のトランジスタ162のゲート電極とは、電気的に接続される。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体OSを用い、オフ状態でのソースとドレイン間のリーク電流(オフ電流)が少ない書き込み用トランジスタ162、書き込み用トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルを有する半導体装置において、メモリセルへの情報の書き込みは、書き込み用トランジスタ162のソース電極またはドレイン電極の一方と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードFGに電位を供給し、ノードFGに所定量の電荷を保持させることで行う。書き込みを1×109回行う前後において、メモリセルのメモリウィンドウ幅の変化量は2%以内である。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体以外の半導体材料が用いられた第1のチャネル形成領域を有する第1のトランジスタ160と、第1のトランジスタ160の上方の、酸化物半導体材料が用いられた第2のチャネル形成領域を有する第2のトランジスタ162と、容量素子164と、を有し、第2のトランジスタ162の第2のソース電極または第2のドレイン電極の一方と、容量素子164の電極の一方とは、電気的に接続される。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタ160と、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタ160と、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成される。

(もっと読む)

不揮発性半導体記憶装置における書き込み方法及び不揮発性半導体記憶装置

【課題】書き込み禁止メモリセルへの誤書き込みである書き込みディスターブを抑止して大幅な追加書き込み回数の増加を可能にする不揮発性半導体記憶装置の書き込み方法の提供。

【解決手段】Nウェルの中にPウェルを形成し、前記Pウェルの表面上に、複数の不揮発性のメモリセルを直列に接続したNAND束をマトリックス状に配列してなるメモリセルアレイを具備する不揮発性半導体記憶装置の書き込み方法であって、前記メモリセルに対する書き込み期間(t0→t4の期間)におけるプログラム電圧の印加による書き込み動作(t3→t4の期間)の前の期間に前記NAND束の全てのメモリセルのワード線に第1の電圧を印加するとともに、前記Pウェルに第1の電圧よりも高い第2の電圧CPWを印加し、さらに前記書き込み期間において前記Pウェルに対し前記Nウェルが逆バイアスされるように前記Pウェル及び前記Nウェル間に逆バイアス電圧CNWを印加する。

(もっと読む)

NAND型フラッシュメモリ

【課題】メモリセルの閾値電圧の分布幅の拡大を抑制することが可能なNAND型フラッシュメモリを提供する。

【解決手段】NAND型フラッシュメモリは、半導体基板表面のウェル上に第1の絶縁膜を介して形成され周囲から絶縁された電荷保持層と、前記電荷保持層との間に第2の絶縁膜を介して設けられた制御ゲートと、を有し、且つ前記電荷保持層に保持された電荷量に応じた閾値電圧に対応して情報が記憶されるメモリセルトランジスタと、前記制御ゲートに印加する電圧、および前記ウェルに印加する電圧を制御することにより、前記メモリセルトランジスタの動作を制御する制御回路と、を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択消去が可能な不揮発性半導体記憶装置を提供する。

【解決手段】メモリ部と制御部とを備える不揮発性半導体記憶装置を提供する。メモリ部は、互いに電気的に分離された第1、第2第半導体層に形成された第1、第2メモリストリングMCS1、MCS2と、第1、第2半導体層に接続された第1、第2配線W11、W12と、を有する。第1、第2メモリストリングは、複数のメモリセルを有する第1、第2メモリセル群と、第1、第2選択ゲートと、を有する。第1メモリセル群の選択セルトランジスタCL1を選択的に消去する際に、制御部は、第1配線に高電圧Vppを、選択セルトランジスタの制御ゲートに0Vを、選択セルトランジスタ以外の第1メモリストリングの非選択セルの制御ゲート、及び、第1選択ゲートに中間電圧Vmを、第2配線に中間電圧以下の低電圧Vccまたは0Vを印加する。

(もっと読む)

マルチドットフラッシュメモリ

【課題】マルチドットフラッシュメモリの書き込み/消去の低消費電力化を図る。

【解決手段】本発明の例に係わるマルチドットフラッシュメモリは、書き込み/消去の対象となる選択されたフローティングゲートの左側に存在するビット線BL13,BL12,BL11,…の電位V2(1), V2(2), V2(3),…を、V2(1)>V2(2)>V2(3)>…とし、選択されたフローティングゲートの右側に存在するビット線BL14,BL15,BL16,…の電位V1(1), V1(2), V1(3),…を、V1(1)<V1(2)<V1(3)<…とする。但し、V2(1)は、プラス電位、V1(1)は、マイナス電位である。また、ビット線の電位は、選択されたフローティングゲートから離れるに従い、0Vに収束する。

(もっと読む)

半導体装置と、それを用いた可変インピーダンス回路および共振回路

【課題】電源電圧が遮断されている場合でも記憶データに基づいてスイッチ回路を導通状態または非導通状態にすることが可能な半導体装置を提供する。

【解決手段】この半導体集積回路装置では、浮遊ゲートおよび制御ゲートを有するメモリトランジスタMAと、ゲートが浮遊ゲートに接続され、メモリトランジスタMAの記憶データに応じてオンまたはオフするNチャネルMOSトランジスタQAとを含む。したがって、電源電圧VCCが遮断されている場合でも、メモリトランジスタMAの記憶データに基づいてトランジスタQAをオンまたはオフさせることができる。

(もっと読む)

半導体装置の製造方法

【課題】不揮発性メモリを有する半導体装置を小型にする。

【解決手段】複数の第1電極4Gと、これに交差する複数のワード線5と、複数の第1電極4Gの隣接間であって複数のワード線5が平面的に重なる部分に配置された複数の浮遊ゲート電極6Gとを有する複数の不揮発性メモリセルMCを持つAND型のフラッシュメモリにおいて、上記複数の浮遊ゲート電極6Gの各々の断面形状を上記第1電極4Gよりも高い凸状とした。これにより、不揮発性メモリセルMCが微細化されても浮遊ゲート電極6Gを容易に加工できる上、不揮発性メモリセルMCの占有面積を増大させることなく浮遊ゲート電極6Gとワード線5の制御ゲート電極とのカップリング比を向上させることができる。

(もっと読む)

不揮発性半導体記憶装置とその駆動方法および電子機器

【課題】周辺回路の増大を極力抑えつつ、データディスターブを改善する不揮発性半導体記憶装置を提供する。

【解決手段】第1ボディ領域100上に不純物拡散層104,124を、第1不純物拡散層104上に第2ボディ領域106を形成する。第1不純物拡散層104はメモリトランジスタMTのドレイン領域と選択トランジスタSTのソース領域、第1不純物拡散層124は選択トランジスタSTのドレイン領域をなす。第2ボディ領域106と第1不純物拡散層104に跨るように第2ボディ領域106上にメモリトランジスタMTのゲート部G_MTをMONOS構造で形成する。第1不純物拡散層104、第1ボディ領域100、第1不純物拡散層124に跨るように選択トランジスタSTのゲート部G_STをMOS型構造で形成する。両トランジスタMT,STは、バックゲートとなるボディ領域が電気的に分離される。

(もっと読む)

不揮発性半導体メモリ及びその製造方法

【課題】電荷トラップ型の不揮発性半導体メモリのデータ読み出し速度を向上させること。

【解決手段】本発明に係る不揮発性半導体メモリは、半導体基板100中のチャネル領域上に第1ゲート絶縁膜110を介して形成された第1ゲート電極WGと、チャネル領域上に第2ゲート絶縁膜120を介して形成された第2ゲート電極CGと、第1ゲート電極WGの上面に形成された第1シリサイド膜151と、第2ゲート電極CGの上面に形成された第2シリサイド膜152と、を備える。第1ゲート電極WGと第2ゲート電極CGは共にサイドウォール形状を有する。第1ゲート電極WGと第2ゲート電極CGは、チャネル領域上で絶縁膜を挟んで並んで配置されており、第1ゲート絶縁膜110及び第2ゲート絶縁膜120のいずれか一方は、電荷をトラップする電荷トラップ膜である。

(もっと読む)

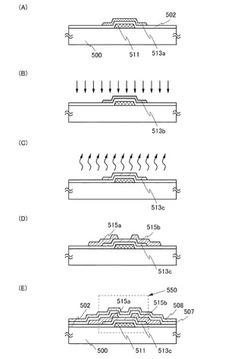

半導体装置の製造方法および半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】消去速度が速く、メモリセル間の干渉が少ない不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置1において、それぞれ複数の層間絶縁膜ILD及び制御ゲート電極CGを交互に積層させて積層体MLを形成する。そして、積層体MLに積層方向に延びる貫通ホールHを形成し、貫通ホールHを介して層間絶縁膜ILDにおける貫通ホールHに面した部分をエッチングして除去し、除去部分Aを形成する。次に、貫通ホールH及び除去部分Aの内面上に絶縁膜IPDを形成し、除去部分Aの内部にシリコンからなる浮遊ゲート電極FGを形成し、浮遊ゲート電極FGにおける貫通ホールHに面した部分を覆うように絶縁膜TOxを形成する。そして、貫通ホールHの内部に半導体ピラーSPを埋設する。

(もっと読む)

半導体装置

【課題】シリコン基板に結晶欠陥が発生するのを抑制して、動作の信頼性が確保され高い歩留まりが得られる半導体装置を提供する。

【解決手段】シリコン基板2に形成された溝にトレンチ分離酸化膜3が形成されている。そのトレンチ分離酸化膜3上にフローティングゲート電極10a〜10dおよびコントロールゲート電極12a〜12dが形成されている。フローティングゲート電極等によって挟まれた領域にシリコン基板2の表面を露出する開口部3aが形成されている。開口部3aを埋込むとともにコントロールゲート電極を覆うようにBPTEOS膜16が形成されている。BPTEOS膜16によって埋込まれた開口部3a内にボイド21が形成されている。

(もっと読む)

半導体装置

【課題】FNトンネル電流の劣化が抑制された良好な書き込み消去特性を有する半導体装置を提供すること。

【解決手段】半導体基板1に離間して形成された第1および第2の拡散層2と、前記第1および第2の拡散層2の間に設けられたチャネル領域3と、前記チャネル領域3の表面に設けられた第1の絶縁膜11、前記第1の絶縁膜11上に設けられた電荷蓄積膜12、前記電荷蓄積膜12上に設けられた第2の絶縁膜13、前記第2の絶縁膜13上に設けられた制御ゲート電極14、を備えるゲート電極部10と、を有して電気的に情報を書き込み消去可能なメモリセルトランジスタが前記半導体基板1に複数配置され、前記ゲート電極部10のゲート長方向における側壁部にシリコン窒化膜よりも高い誘電率を有する第3の絶縁膜30が設けられている。

(もっと読む)

電子素子の電子ブロック層

不揮発性メモリ素子などの電子素子用の方法および装置が記載される。メモリ素子は、2層または3層などの多層の制御誘電体を含む。多層制御誘電体は、酸化アルミニウム、酸化ハフニウム、および/または、酸化ハフニウムアルミニウムのハイブリッド膜などの高k誘電体材料の組み合わせを含む。多層制御誘電体により、単一または多状態(例えば、2ビット、3ビット、または4ビット)動作の実現可能性を備えながら、増大された電荷保持、向上されたメモリプログラム/消去ウィンドウ、改善された信頼性および安定性を含む向上された特性を与える。  (もっと読む)

(もっと読む)

41 - 60 / 115

[ Back to top ]