Fターム[5F083ER25]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 紫外線により消去するもの(EPROM) (42)

Fターム[5F083ER25]に分類される特許

1 - 20 / 42

半導体装置

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】第1のトランジスタ及び第2のトランジスタを有するメモリセルを有し、第1のトランジスタは第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタは酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される不揮発性メモリによって解決する。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

半導体メモリ

【課題】ビット線間の寄生容量による影響を低減することにより、高精度のデータの読出しを可能にする半導体メモリを提供する。

【解決手段】1つの主ビット線に互いに異なるタイミングでオン駆動するセレクタ素子及び当該セレクタ素子のそれぞれに接続された副ビット線を介して当該副ビット線のそれぞれにメモリセルが接続され、当該主ビット線に並置されるとともに固定電位に接続された固定電位線が設けられていること。

(もっと読む)

半導体装置

【課題】小型化が可能な不揮発性メモリを備えた半導体装置を提供する。

【解決手段】基板901上に画素と不揮発性メモリとを備え、不揮発性メモリは、基板901上に形成される半導体活性層と、半導体活性層上に形成される絶縁膜923と、絶縁膜923上に形成されるフローティングゲイト電極907と、フローティングゲイト電極907を酸化して得られる酸化膜908,915,922と、酸化膜908,915,922に接して形成されるコントロールゲイト電極929と、を備え、画素と不揮発性メモリとは、基板901上に一体形成される。

(もっと読む)

半導体装置

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。また、半導体装置の信頼性を向上させる。また、半導体装置の性能を向上すると共に、半導体装置の信頼性を向上する。

【解決手段】フローティングゲート電極FGを有するメモリトランジスタとこのメモリトランジスタに直列に接続された制御トランジスタとで構成されたメモリセルを、半導体基板の主面にX方向およびY方向にアレイ状に複数配列させる。そして、X方向に配列したメモリセルのメモリトランジスタのドレイン領域同士を接続するビット配線M1Bを、半導体基板上に形成された多層配線構造のうちの最下層の配線層に設け、このビット配線M1Bがフローティングゲート電極FG全体を覆うようにする。

(もっと読む)

不揮発性メモリ

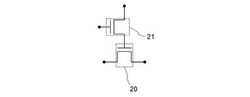

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】不揮発性メモリは、第1のトランジスタ20及び第2のトランジスタ21を有するメモリセルを有し、第1のトランジスタ20は第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタ21は酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される。

(もっと読む)

記憶装置

【課題】ロジック回路を増やすことなく、第三者がメモリセルにアクセスできずかつ必要な場合にはいつでもアクセス可能なメモリセルを有する記憶装置を提供する。

【解決手段】本実施形態は、第1のメモリセルと、第2のメモリセルと、を有し、第2のメモリセルに設けられた第2のトランジスタの第2のチャネルが酸化物半導体膜からなる記憶装置であって、第2のメモリセルからのデータの読み出しは第2のトランジスタに紫外線を照射している時に行われる記憶装置によって解決する。

(もっと読む)

不揮発性メモリを搭載する半導体装置および不揮発性半導体記憶装置の製造方法

【課題】工程数の増大を抑制しつつ、捕獲させた電荷を安定して保持させることが可能な不揮発性半導体記憶装置を提供する。

【解決手段】選択トランジスタTr1およびメモリトランジスタTr2を半導体基板1上に横方向に並べて形成することでFAMOSを構成し、メモリトランジスタTr2のフローティングゲート電極5cは、選択トランジスタTr1のサイドウォール5a、5bに使用されているのと同一のシリコン窒化膜から構成する。

(もっと読む)

半導体製造装置、ゲルマニウムドットの製造方法およびそれを用いた半導体メモリの製造方法

【課題】ゲルマニウムからなるドットの密度を向上可能な半導体製造装置を提供する。

【解決手段】半導体製造装置600は、石英管610と、反応室620と、石英管610内へH2ガスを供給する配管650と、石英管610内にリモート水素プラズマを生成するアンテナ670、マッチング回路680および高周波電源690と、反応室620内で基板800を保持する基板ホルダー630と、基板800を加熱するヒーター640と、ゲルマンガスを基板800の近傍に供給する噴出器700および配管710とを備える。

(もっと読む)

金属ドットの製造方法およびそれを用いた半導体メモリの製造方法

【課題】金属薄膜をリモートプラズマによって処理するときのガスの種類によってドットの密度を制御可能な金属ドットの製造方法を提供する。

【解決手段】SiO2膜502がSiからなる半導体基板501上に形成され(工程(b))、金属薄膜504がSiO2膜502上に形成される(工程(c))。その後、水素ガス、ヘリウムガス、アルゴンガス、窒素ガス、アンモニアガス、水素ガスとヘリウムガスとの混合ガス、水素ガスとアルゴンガスとの混合ガスおよび水素ガスと窒素ガスとの混合ガスの中から選択したガスを用いたリモートプラズマによって金属薄膜504を処理する(工程(d))。これによって、金属ドット503がSiO2膜502上に形成される(工程(e))。

(もっと読む)

キャパシタの製造方法

【課題】 簡単な製造工程で、自然酸化膜の影響を受けることなく、膜質のよいONO構造で、その誘電体膜を薄く形成することができるキャパシタの製造方法を提供する。

【解決手段】 ポリシリコンからなる下層電極3を形成し(図(a))、その下層電極3を、たとえば硫酸と硝酸との混合液のように、ポリシリコンを酸化する酸の溶液に浸漬させ、下層電極3の表面にシリコン酸化膜4を形成する(図(b))。そして、そのシリコン酸化膜4上にシリコン窒化膜5を堆積し、そのシリコン窒化膜5の表面を酸化させる方法などにより、シリコン窒化膜5の表面にシリコン酸化膜6を形成し(図(c))、その上に上層電極7を形成する(図(d))ものである。

(もっと読む)

不揮発性メモリデバイス及びその製造方法

【課題】メモリセル部以外の周辺回路部におけるホットキャリア特性の向上に寄与する不揮発性メモリデバイス及びその製造法を提供することを課題とする。また、メモリセル部の電荷蓄積窒化膜に含まれる電子を消去するに際し、消去後の電流値の低下を抑制可能な不揮発性メモリデバイス及びその製造法を提供することを他の課題とする。

【解決手段】本発明は、半導体層上に形成された情報格納用のメモリセル部と;前記半導体層上に形成された前記メモリセル部以外の周辺回路部とを同時に形成してなる不揮発性メモリデバイスに適用される。そして、前記メモリセル部は、前記半導体層上に形成されたゲート電極と;前記ゲート電極の下端両側に食い込むノッチ上に形成された絶縁膜よりなる電荷蓄積層とを備える。一方、前記周辺回路部は、電荷蓄積層を備えない構造とする。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル間の間隔を狭めつつ、この間隔に対する層間絶縁膜や金属膜の埋め込み性を改善すること。

【解決手段】互いに対向するゲート電極14L,14Rに積層されたONO膜52L,52Rと、ゲート電極同士の間の第1主面10aを被覆するイオン注入保護膜とを含むメモリセル前駆体が、第1主面上に第1距離だけ離間して設けられた半導体基板10を準備し、ウエットエッチングにより、第2酸化膜32L,32Rの、側面14LS,14RSに垂直に測った厚みを薄くして、メモリセル前駆体同士の距離を第1距離よりも長い第2距離とする工程を含む。

(もっと読む)

MOS型半導体メモリ装置

【課題】優れたデータ保持特性と、高速でのデータ書換え性能と、低消費電力での動作性能と、高い信頼性と、を同時に兼ね備えた不揮発性MOS型半導体メモリ装置を提供する。

【解決手段】MOS型半導体メモリ装置601は、大きなバンドギャップを持つ第1の絶縁膜111および第5の絶縁膜と、最も小さなバンドギャップを持つ第3の絶縁膜113との間に、両者の中間の大きさのバンドギャップを持つ第2の絶縁膜112および第4の絶縁膜114を備えている。このようなエネルギーバンド構造を有することにより、データ書き込み時には第1の絶縁膜111を介した電荷の移動が起こりやすく、書き込み動作速度を高速化することが可能で、かつ絶縁膜積層体に電荷を注入するために必要な書き込み電圧を小さく抑えることができる。

(もっと読む)

不揮発性メモリ及びその製造方法

【課題】不揮発性メモリの性能を向上させつつ製造工程を減少させること。

【解決手段】不揮発性メモリは、メモリセルMCにおいて、N型ウェル3aにP型拡散領域7a、P型拡散領域7b、及びP型拡散領域7cが形成され、P型拡散領域7aとP型拡散領域7bの間のチャネル上にセレクトゲート絶縁膜4aを介してセレクトゲート6aが形成され、P型拡散領域7bとP型拡散領域7cの間のチャネル上にフローティングゲート絶縁膜5を介してフローティングゲート6bが形成されている。周辺回路PTにおいて、N型ウェル3bにP型拡散領域7d及びP型拡散領域7eが形成され、P型拡散領域7dとP型拡散領域7eの間のチャネル上に周辺回路ゲート絶縁膜4bを介し周辺回路ゲート6cが形成されている。フローティングゲート絶縁膜5の膜厚は、セレクトゲート絶縁膜4a及び周辺回路ゲート絶縁膜4bの膜厚よりも厚く構成されている。

(もっと読む)

半導体集積回路装置及び半導体集積回路装置の製造方法

【課題】製造過程において半導体記憶素子の書き込みテストを行うことができる半導体集積回路を提供する。

【解決手段】光照射によりデータの記憶状態が変化するPROM22が形成された基板10と、基板10のPROM22が形成された面側に形成された多層配線構造70と、を備え、多層配線構造70に、PROM22が形成されたPROM領域20に対向する位置に透光性材料により形成され、多層配線構造70の外部からPROM22への光導入路とされる透光領域80と、透光領域80の周囲に、複数層の遮光性材料により連続的に形成された遮光領域30と、透光領域80からみて遮光領域30を介して外側に形成され、PROM22の記憶状態を操作するためのPAD部60と、を備えた。

(もっと読む)

半導体装置

【課題】浮遊ゲートをもち制御ゲートを備えていない不揮発性メモリセルを備えた半導体装置において、その不揮発性メモリセルの読出し特性を飛躍的に改善する。

【解決手段】不揮発性メモリセルは、P型半導体基板1上に形成された書込みメモリゲート酸化膜9及び書込みメモリゲート酸化膜9上に形成された電気的に浮遊状態のポリシリコンからなる書込み浮遊ゲート11をもつPMOS書込みトランジスタと、P型半導体基板1上に形成された読出しメモリゲート酸化膜15及び読出しメモリゲート酸化膜15上に形成された電気的に浮遊状態のポリシリコンからなる読出し浮遊ゲート17をもつNMOS読出しトランジスタを備えている。書込み浮遊ゲート11と読出し浮遊ゲート17は電気的に接続されている。不揮発性メモリセルへの書込みはPMOS書込みトランジスタによって行なわれ、読出しはNMOS読出しトランジスタによって行なわれる。

(もっと読む)

半導体装置及びその作製方法

【課題】外部から局所的に圧力がかかっても破損しにくい半導体装置を提供する。また、外部からの局所的押圧による非破壊の信頼性が高い半導体装置を歩留まり高く作製する方法を提供する。

【解決手段】単結晶半導体領域を用いて形成された半導体素子を有する素子基板上に、有機化合物または無機化合物の高強度繊維に有機樹脂が含浸された構造体を設け、加熱圧着することにより、有機化合物または無機化合物の高強度繊維に有機樹脂が含浸された構造体及び素子基板が固着された半導体装置を作製する。

(もっと読む)

半導体装置

【課題】 EPROMを搭載するICチップにおいて、データを消去するメモリ素子(書換え可能な)とデータを消去したくないメモリ素子(データ冗長用)を同時に有する半導体装置を提供する。

【解決手段】 特定のメモリ素子の上に紫外光線を反射、吸収する遮光物を形成する。このことによりデータ消去性を調整できるようなメモリ素子を形成できるようにする。また、遮光物に開口することで、より消去制御性のよりメモリ素子とすることができる。

(もっと読む)

半導体装置の製造方法

【課題】メモリ領域の配線層の露出を防止し、配線抵抗の変動や信頼性劣化を防止する紫外線消去型の不揮発性メモリセルを有した半導体装置の製造方法を提供する。

【解決手段】パッド電極20及び層間絶縁膜2C上に紫外線を透過するエッチングストッパー膜として、SiO2膜21を形成する。その後、パッド電極20上のSiO2膜21を選択的にエッチング除去し、EPROM領域上についてはSiO2膜21を残す。その後、SiO2膜21上及びSiO2膜21が除去されたパッド電極20上に紫外線を透過しない保護膜として、シリコン窒化膜23及びポリイミド膜24を形成する。そして、パッド電極20上及びEPROM領域上のシリコン窒化膜23及びポリイミド膜24を選択的にエッチング除去する。このとき、SiO2膜21はエッチングストッパーとして作用するので、コントロールゲートラインメタル層19が露出するのを防止できる。

(もっと読む)

1 - 20 / 42

[ Back to top ]