Fターム[5F083ER27]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | パルス印加方式 (44)

Fターム[5F083ER27]に分類される特許

1 - 20 / 44

不揮発性半導体記憶装置

【課題】高い信頼性を有し且つ安価な不揮発性半導体記憶装置を提供する。

【解決手段】この不揮発性半導体記憶装置において、メモリストリングスは、基板に対して垂直方向に延びる一対の柱状部、及び前記一対の柱状部の下部を連結させるように形成された連結部を有する半導体層と、前記柱状部の側面を取り囲むように形成された電荷蓄積層と、前記柱状部の側面及び前記電荷蓄積層を含む第1の絶縁膜と、前記柱状部の側面及び前記第1の絶縁膜を覆うように形成された第1導電層と、前記連結部の周囲に形成される第2の絶縁膜と、前記連結部に前記ゲート絶縁膜を介して形成される第2導電層とを備える。

(もっと読む)

NAND型不揮発性メモリのデータ消去方法

【課題】NAND型不揮発性メモリを提供する。

【解決手段】ビット線と、ソース線と、複数の不揮発性メモリが直列に接続されたNAND型セルと、選択トランジスタと、を有し、不揮発性メモリは、第1の絶縁膜を介した半導体上の電荷蓄積層と、第2の絶縁膜を介した電荷蓄積層上の制御ゲートと、を有し、NAND型セルの一方の端子は、選択トランジスタを介して、ビット線に接続され、NAND型セルの他方の端子は、ソース線に接続されたNAND型不揮発性メモリであって、第1の絶縁膜は、半導体に酸素雰囲気で高密度プラズマ処理を行った後、窒素雰囲気で高密度プラズマ処理を行うことで形成されるNAND型不揮発性メモリ。

(もっと読む)

フラッシュEEPROM(FLASHEEPROMMEMORY)の消去方法

【課題】電荷の蓄積を制御することによりメモリセルを消去するフラッシュEEPROMの消去方法を提供する。

【解決手段】フラッシュメモリの消去方法は、F/Nトンネリング期間において、ウェル電極と第二半導体領域に対し正極性の第一電圧バイアスを印加し、且つコントロールゲート電極に対し負極性の第二電圧バイアスを印加するステップと、F/Nトンネリング期間のあとのトラップ減少期間において、ウェル電極と第二半導体領域に対し正極性の第三電圧バイアスを印加し、且つコントロールゲート電極に対し第一ゼロ電圧バイアスを印加するステップと、トラップ減少期間のあとのトラップアシストトンネリング期間において、コントロールゲート電極に対し負極性の第四電圧バイアスを印加し、且つウェル電極と第二半導体領域に対し第二ゼロ電圧バイアスを印加するステップと、を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】データリテンションの特性を向上しつつ消去動作や書き込み動作に要する時間を短縮する。

【解決手段】

不揮発性半導体記憶装置は、第1書き込み領域と第2書き込み領域を有し、複数のメモリセルを含むメモリセルアレイを備える。制御回路は、複数のメモリセルに対して印加する電圧を制御する。制御回路は、複数のメモリセルに対し消去動作を実行する場合に、第2書き込み領域のメモリセルに隣接する第1書き込み領域のメモリセルを除いた第1書き込み領域のメモリセルに第1閾値電圧を与える一方、第2書き込み領域のメモリセル及び第2書き込み領域のメモリセルに隣接する第1書き込み領域のメモリセルに第1閾値電圧より電圧値が大きい消去状態を示す正の第2閾値電圧を与えるよう制御する。

(もっと読む)

メモリにおけるプログラムノイズ低減のための鋸形のマルチパルスプログラミング

半導体メモリ装置および半導体メモリ装置の駆動方法

【課題】オフ状態のソースとドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを保存する半導体装置を提供する。

【解決手段】書き込みトランジスタのドレインと読み出しトランジスタのゲート、および、前記ドレインとキャパシタの一方の電極を接続した記憶セルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に、書き込みトランジスタのソースを書き込みビット線に、読み出しトランジスタのソースとドレインとを、それぞれ、読み出しビット線及びバイアス線に接続する。さらに、キャパシタの他方の電極を読み出しワード線に接続する。配線数を減らすために、読み出しビット線を書き込みビット線や他の列のバイアス線で代用する。

(もっと読む)

半導体メモリ装置

【課題】いわゆるMNOS構造において、ゲート絶縁膜を介した漏れ電流の発生を大幅に抑制させた半導体メモリ装置の提供。

【解決手段】ゲート絶縁膜は、半導体層側に半導体酸化膜、ゲート電極側に半導体窒化膜の積層膜からなる半導体メモリ装置であって、

横軸にゲート電圧をとり縦軸にドレイン電流をとったヒステリシス特性が、ゲート電圧を負側から正側への掃引によって得られる特性を第1特性とし、ゲート電圧を正側から負側への掃引によって得られる特性を第2特性とした場合、前記第1特性は、前記第2特性に対して、ゲート電圧が大きくなる側に位置づけられる特性となっている。

(もっと読む)

不揮発性半導体記憶装置及びその書き込み方法

【課題】書き込み速度の遅れや書き込み不良等を招くことなく、更なる微細化を実現し得る不揮発性半導体記憶装置及びその書き込み方法を提供する。

【解決手段】選択トランジスタとメモリセルトランジスタとを有する複数のメモリセルと、選択トランジスタのドレインに接続されたビット線と、メモリセルトランジスタのコントロールゲートに接続された第1のワード線と、選択トランジスタのセレクトゲートに接続された第2のワード線と、メモリセルトランジスタのソースに接続されたソース線とを有し、第1の電圧Vstep(1)を第1のワード線に印加しながら、ソース線に第2の電圧Vpulse(1)をパルス状に印加する第1のステップと、第1の電圧より高い第3の電圧Vstep(2)を第1のワード線に印加しながら、ソース線に第2の電圧より低い第4の電圧Vpulse(2)をパルス状に印加する第2のステップとを少なくとも実行することにより、メモリセルに情報を書き込む。

(もっと読む)

不揮発性半導体記憶装置

【課題】本発明の目的は、書き込み/消去特性が向上しつつ、電荷保持特性、が向上した、MONOS型メモリを、簡単、且つ、再現性高く、形成する方法を提供することである。

【解決手段】本発明の半導体装置は、シリコン基板上に形成されたトンネル絶縁膜と、トンネル絶縁膜上に形成された電荷蓄積膜と、電荷蓄積膜上に形成されたブロック膜と、ブロック膜上に形成された制御ゲート電極膜と、を備えるMONOS型メモリセルであって、トンネル絶縁膜は、シリコン基板上に形成された第1のシリコン酸化膜と、第1のシリコン酸化膜上に形成されたボロンを含むシリコン窒化膜と、シリコン窒化膜上に形成された第2のシリコン酸化膜と、を備えたものである。

(もっと読む)

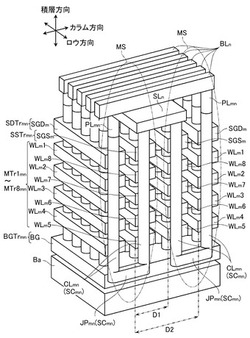

3次元メモリー装置、及びそのプログラム方法

【課題】集積度の増加と共にプログラムディスターバンス問題を効果的に減らすことができる3次元メモリー装置、及びそのプログラム方法が提供される。

【解決手段】本発明の3次元メモリー装置は、複数のワードライン平面が積層されたメモリーセルアレイ、選択されたワードライン平面に具備された少なくとも2以上のページのメモリーセルを同時にプログラムする書込み読出し回路、そして前記書込み読出し回路のプログラム動作を制御する制御回路を含むことができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】高性能な書きこみ消去特性を有する不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板のp型ウエル2上にゲート絶縁膜6を介して選択ゲート18が形成され、p型ウエル2上に酸化シリコン膜15a、窒化シリコン膜15bおよび酸化シリコン膜15cからなる積層膜15を介してメモリゲート17が形成される。メモリゲート17は、積層膜15を介して選択ゲート18に隣接する。p型ウエル2の選択ゲート18およびメモリゲート17の両側の領域には、ソース、ドレインとしてのn型の不純物拡散層20,21が形成されている。不純物拡散層20,21の間に位置するチャネル領域のうち、選択ゲート18により制御され得る領域51とメモリゲート17により制御され得る領域52とにおける不純物の電荷密度が異なる。

(もっと読む)

不揮発性半導体メモリ装置の消去方法

【課題】保持特性に優れた不揮発性半導体メモリ装置の消去方法を提供することである。

【解決手段】ソース・ドレイン領域2、3が離間して形成された半導体基板1と、半導体基板1上に形成された第1の絶縁層7と、第1の絶縁層7上の第1の領域10に形成された第1のゲート電極5と、第1の絶縁層7上の第2の領域11、12に形成された電荷蓄積層8と、電荷蓄積層8上に形成された第2の絶縁層9と、第2の絶縁層9上に形成された第2のゲート電極4、6と、を有する不揮発性半導体メモリ装置の消去方法は次のステップを有する。ソース・ドレイン領域から電荷蓄積層にホットホールを注入するステップ。電荷蓄積層の第1のゲート電極側の領域にチャネルホットエレクトロンを注入するステップ。

(もっと読む)

NAND型フラッシュメモリ

【課題】メモリセルのしきい値電圧の分布幅の拡大を抑制することが可能なNAND型フラッシュメモリを提供する。

【解決手段】NAND型フラッシュメモリは、第1の絶縁膜、電荷保持層、第2の絶縁膜、および、制御ゲートを含み、電荷保持層に保持された電荷量に応じた情報を記憶するメモリセルが直列に複数接続されたNANDストリングと、制御ゲートおよび半導体ウェルに印加する電圧を制御する制御回路とを備え、書き込み動作後、選択メモリセルにデータが書き込まれたか否かを検証するベリファイリード動作を行う前に、制御回路は、選択メモリセルの制御ゲートに、半導体ウェルの電位と同電位または書き込み電圧と同極性である第1の電圧を印加し、書き込み対象ではない非選択メモリセルの制御ゲートには、書き込み電圧と同極性であり第1の電圧よりも絶対値として大きい第2の電圧を印加するデトラップ動作を行う。

(もっと読む)

不揮発性半導体記憶装置並びにその駆動方法

【課題】 注入効率が高く、書き込まれた情報が安定的に保持される不揮発性半導体記憶装置並びにその駆動方法を提供する。

【解決手段】 メモリセル1は、N型基板2上に、P型の不純物拡散領域3,4を離間して形成し、両領域間に係る前記基板上において、不純物拡散領域3に隣接して形成された第一積層部15と、不純物拡散領域4に隣接し前記第一積層部15と離間して形成された第二積層部16を備える。メモリセル1に対する書き込み処理時において、第一ゲート電極8に対し、同ゲート電極下方に位置する基板2の表面が弱反転状態となる条件の第一負電圧を印加し、第二ゲート電極10に対し、前記第一負電圧よりも絶対値の大きい第二負電圧を印加し、不純物拡散領域4に対して前記第一負電圧よりも絶対値の大きいドレイン電圧を印加し、不純物拡散領域3に対して、前記ドレイン電圧よりも電位の高いソース電圧をそれぞれ印加する。

(もっと読む)

不揮発性半導体記憶装置

【課題】効率的に消去動作を実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリストリングMSと、メモリストリングMSの一端に一端を接続されたソース側選択トランジスタSSTrと、ソース側選択トランジスタSSTrの他端に一端を接続されたソース線SLと、ソース側選択トランジスタSSTrのゲートに接続されたソース側選択ゲート線SGSと、メモリセルのデータを消去する消去動作を実行する制御回路AR2とを備える。制御回路AR2は、消去動作時に、ソース線SLの電圧をソース側選択ゲート線SGSの電圧よりも所定電位差だけ大きく保ちつつソース線SLの電圧及びソース側選択ゲート線SGSを昇圧させる。所定電位差は、GIDL電流を生じさせる電位差Vthである。

(もっと読む)

ブースト電圧クランプを改善するためのペアビットラインプログラミング

プログラミング技法は、プログラム外乱を回避するために阻止されたチャネルのクランプブースト電位を上昇させる選択ビットラインパターンを使用してプログラミングすることによって、不揮発性記憶素子のセットでのプログラム外乱を削減する。1つの態様では、隣接するビットラインの交互のペアを第1のセット及び第2のセットにグループ化する。二重プログラミングパルスが、選択されたワードラインに印加される。ビットラインの第1のセットは、第1のパルスの間にプログラミングされ、ビットラインの第2のセットは、第2のパルスの間にプログラミングされる。次に、全てのビットラインに検証動作が実行される。ある特定のビットラインが阻止されると、その隣接ビットラインの少なくとも1つも阻止され、その特定のビットラインのチャネルが十分にブーストされる。別の態様は、2ビットラインおきに別々にプログラミングする。修正されたレイアウトによって、ビットラインの隣接するペアは、奇数−偶数検出回路を使用して検出できる。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置及びその駆動方法

【課題】半導体層と絶縁膜との間の界面の特性を改善した不揮発性半導体記憶装置及びその駆動方法を提供する。

【解決手段】不揮発性半導体記憶装置101は、チャネル1aとチャネル1aの両側に設けられたソース領域及びドレイン領域2とを有する半導体層1と、チャネル1aの上に設けられた第1絶縁膜3Aと、第1絶縁膜3Aの上に設けられた電荷保持層3Bと、電荷保持層3Bの上に設けられた第2絶縁膜3Cと、第2絶縁膜3Cの上に設けられたゲート電極4と、を有するメモリセルと、ゲート電極4と半導体層1との間に、一定の振幅と一定の周波数とを有するバースト信号を印加し、電荷保持層に電荷の書き込み及び消去の少なくともいずれかの処理を行う駆動部20と、を備える。

(もっと読む)

不揮発性半導体記憶素子、不揮発性半導体装置及び不揮発性半導体素子の動作方法

【課題】

本発明は、データ保持時の不揮発性半導体記憶素子の上部絶縁層からの電荷の放出を効果的に抑制し、不揮発性半導体記憶素子のデータ保持中の閾値変化を効果的に抑制することを目的とする。

【解決手段】

本発明に係る不揮発性半導体記憶素子は、半導体基板1と、半導体基板1の表面内に設けられたソース領域2及びドレイン領域3と、半導体基板上に設けられたトンネル絶縁膜4と、トンネル絶縁膜4上に設けられた導電性電荷蓄積層5と、導電性電荷蓄積層5上に設けられた上部絶縁層6と、上部絶縁層6上に設けられた制御ゲート7とを含む構造である。そして、上部絶縁層6は、透過絶縁層6aと電荷捕獲層6bとブロック層6cの積層構造である。そして、電荷捕獲層6bのトラップ準位密度が透過絶縁層6aとブロック層6cのトラップ準位密度と比べて大きく、透過絶縁層6aのリーク電流が、ブロック層6cのリーク電流と比べて大きい。

(もっと読む)

不揮発性メモリのプログラミング方法

【課題】メモリに書き込むための電圧、時間、及び電力を低減するための不揮発性メモリのプログラミング方法を提供する。

【解決手段】不揮発性メモリのプログラミング方法が提供される。その方法は、ソース又はドレインのキャリアを基板内へ注入すべくソース又はドレインに少なくとも電圧を印加する工程と、十分なエネルギーを有する基板内にあるキャリアが電荷記憶デバイスに到達すべく酸化層を通過することができるようにゲート又は基板に第3の電圧を印加する工程とを備える。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】 非導電性の電荷トラップ膜を電荷蓄積領域として用いる不揮発性メモリの読み出し電流を大幅に向上させることができ、また、読み出しディスターブによるデータ反転の読み出し不良を撲滅できる半導体集積回路装置を提供する。

【解決手段】 半導体集積回路装置は、半導体柱と絶縁体柱が一方向に交互に敷き詰めた状態で複数配置された柱列と、前記複数の半導体柱に夫々設けられた複数の不揮発性記憶素子であって、前記半導体柱の前記一方向に沿う側面にゲート絶縁膜を介在して制御ゲート電極が設けられ、前記半導体柱の上面部にドレイン領域が設けられ、かつ前記半導体柱の底面部にソース領域が設けられた複数の不揮発性記憶素子と、前記複数の不揮発性記憶素子の夫々の制御ゲート電極を含み、かつ前記柱列の前記一方向に沿う側面に前記一方向に沿って設けられた配線とを有する。

(もっと読む)

1 - 20 / 44

[ Back to top ]