Fターム[5F083GA25]の内容

Fターム[5F083GA25]に分類される特許

401 - 420 / 686

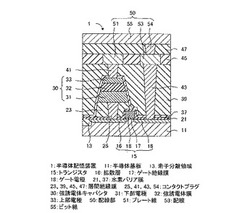

半導体記憶装置及び半導体記憶装置の製造方法

【課題】開孔歩留まりの低下を抑制可能なコンタクトプラグを有する半導体記憶装置を提供する。

【解決手段】半導体基板11の表面に形成された拡散層16を有するトランジスタ15、トランジスタ15の上方に配置された強誘電体キャパシタ30、強誘電体キャパシタ30の上方に配置された配線部50、拡散層16と強誘電体キャパシタ30と配線部50とをそれぞれ接続するコンタクトプラグ25、41、43、及び、強誘電体キャパシタ30を保護する下部の水素バリア膜21、上部の水素バリア膜37を有して、拡散層16と配線部50とを接続するコンタクトプラグ43は、上部の層間絶縁膜39、及び、下部の半導体基板11の表面に接して連続して形成された水素バリア膜21、37が開孔されて形成されている。

(もっと読む)

メモリセル、電子システム、メモリセルの形成方法、およびメモリセルのプログラミング方法

いくつかの実施形態は、誘電体材料によって互いにスペーシングされる、垂直に積層される電荷捕獲領域を有するメモリセルを含む。誘電体材料は、高k材料を含み得る。電荷捕獲領域のうちの1つ以上は、金属材料を含み得る。かかる金属材料は、ナノドット等の複数の個別の絶縁されたアイランドとして存在し得る。いくつかの実施形態は、メモリセルの形成方法を含み、トンネル誘電体上に2つの電荷捕獲領域が形成され、当該領域は互いに対して垂直に配置され、トンネル誘電体に最も近い領域は、もう1つの当該領域よりも深いトラップを有する。いくつかの実施形態は、メモリセルを含む電子システムを含む。いくつかの実施形態は、垂直に積層される電荷捕獲領域を有するメモリセルのプログラミング方法を含む。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】誘電体メモリの微細化が進むと、上部電極の電位を拡散層へ引き出す構造におけるアスペクト比が大きくなるため、上部電極のカバレッジが悪化し、誘電体を結晶化させる熱処理時に上部電極が断線してしまう。

【解決手段】半導体装置は、半導体基板の上方に形成された第1の導電膜及び第2の導電膜と、第1の導電膜を覆うように形成された第1の絶縁膜と、第2の導電膜を覆うように形成された第2の絶縁膜と、第1の絶縁膜に形成され、第1の導電膜に達する第1の開口部と、第1の開口部の壁部及び底部に沿って形成された第3の導電膜と、第3の導電膜、第1の絶縁膜、及び第2の絶縁膜上に形成された誘電体膜と、第2の絶縁膜及び誘電体膜の積層膜に形成され、第2の導電膜に達する第2の開口部と、誘電体膜の上並びに第2の開口部の壁部及び底部に沿って形成された第4の導電膜とを備える。第2の絶縁膜の膜厚が、第1の絶縁膜の膜厚よりも薄い。

(もっと読む)

半導体装置およびその製造方法

【課題】ONO膜に蓄積された電荷のビットライン上への拡散を抑制するまたはビットラインとプラグ金属との接触抵抗を低減すること。

【解決手段】本発明は、半導体基板10内に設けられたビットライン30と、ビットライン間の半導体基板上に設けられた第1ONO膜20と、ビットライン上に設けられた第2ONO膜22と、を具備し、第1ONO膜中の第1窒化シリコン膜15の膜厚は第2ONO膜中の第2窒化シリコン膜16の膜厚より厚い半導体装置およびその製造方法である。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】電極間絶縁膜に含有される窒素や炭素が塗布型素子分離絶縁膜を介してゲート絶縁膜直下の活性領域脇に拡散して固定電荷を発生し、デバイスの電気的特性に悪影響を及ぼすことを抑制する。

【解決手段】塗布型絶縁膜4bが素子分離溝3の内側に形成されている。塩素が5×1018[cm−3]以上含有されたシリコン酸化膜4cが塗布型絶縁膜4b上を覆うように形成されている。このシリコン酸化膜4cが電極間絶縁膜7に含有される窒素や炭素の塗布型絶縁膜4bへの侵入を抑制する。

(もっと読む)

強誘電体キャパシタ及び強誘電体メモリ装置

【課題】MOCVD法による強誘電体膜におけるリーク電流を抑制するとともに、複数の強誘電体層からなる強誘電体膜についてその特性向上を図った強誘電体キャパシタと、この強誘電体キャパシタを備えた強誘電体メモリ装置とを提供する。

【解決手段】下部電極12と、下部電極12上に設けられた強誘電体膜13と、強誘電体膜13上に設けられた上部電極14とを有する強誘電体キャパシタ3である。強誘電体膜13は、下部電極12上に有機金属化学気相堆積法で形成された、ペロブスカイト型の結晶構造を有する第1強誘電体材料からなる第1強誘電体層17と、第1強誘電体層17上に化学溶液堆積法で形成された、ペロブスカイト型の結晶構造を有する第2強誘電体材料からなる第2強誘電体層18と、を含む。第2強誘電体材料の所定厚での抗電圧が、第1強誘電体材料の前記所定厚での抗電圧に対し、±10%の範囲内になっている。

(もっと読む)

半導体素子及びこの半導体素子を用いた装置

【課題】高速な書込み及び消去動作を比較的低電圧で行い、かつ書換え劣化を抑えることで、メモリウインドウが大きく信頼性の高いメモリ素子を、低コストで提供する。

【解決手段】メモリ素子は、絶縁基板上に設けられた半導体層と、P型の導電型を有する第1の拡散層領域及び第2の拡散層領域と、第1の拡散層領域と第2の拡散層領域との間のチャネル領域を覆い、チャネル領域より電荷を注入され得る電荷蓄積膜と、電荷蓄積膜をはさんでチャネル領域とは反対側に位置するゲート電極とを有する。

(もっと読む)

半導体装置およびその作製方法

【課題】不揮発性メモリトランジスタの電荷保持特性を向上させる。

【解決手段】半導体基板と導電膜の間には、第1絶縁膜、電荷トラップ膜、第2絶縁膜が形成されている。電荷トラップ膜は水素濃度が低い上部領域と、水素濃度が高い下部領域を有する窒化シリコン膜でなる。このような窒化シリコン膜は、化学気相成長法により、水素を15atomic%以上含む窒化シリコン膜を形成し、その上部を窒化することで形成される。この窒化処理は、窒素ガスのプラズマ中に生成された窒素ラジカルで窒化シリコン膜を窒化することで行われる。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体キャパシタの上部電極と配線コンタクトとの接続を確実にする半導体装置及びその半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上にはソース/ドレイン拡散層12、ゲート電極13、ゲート絶縁膜14及び側壁絶縁膜15からなるトランジスタTが形成されている。層間絶縁膜16を貫通してトランジスタTに接続するように形成されたコンタクト17に強誘電体キャパシタ22が接続されている。強誘電体キャパシタ22は下部電極19、誘電体分離膜20及び上部電極21から構成され、強誘電体キャパシタ22上には上部電極21と配線25を接続する配線コンタクト23が形成されている。配線コンタクト23と強誘電体キャパシタ22の接触面の平面形状は同一であり、配線コンタクト23の側面と強誘電体キャパシタ22の側面は互いに合致している。

(もっと読む)

強誘電体キャパシタの製造方法及び強誘電体メモリ装置の製造方法

【課題】リーク電流を抑制するとともに、強誘電体膜と上部電極との間の剥離も防止した強誘電体キャパシタの製造方法、及び強誘電体メモリ装置の製造方法を提供する。

【解決手段】第1電極膜12a上に、有機金属化学気相堆積法によって第1強誘電体材料膜17aを形成する工程と、第1強誘電体材料膜17a上に、化学溶液堆積法によって第2強誘電体材料膜の前駆体膜19を形成する工程と、前駆体膜19を、ペロブスカイト型の結晶構造にならない温度で加熱し、乾燥・脱脂を行う工程と、前駆体膜19上に第2電極膜14aを形成する工程と、第2電極膜14a及び前駆体膜19を加熱し、第2電極膜14aに対して回復アニール処理を行うと同時に、前駆体膜19を結晶化しあるいは相転移させることでペロブスカイト型の結晶構造を有する第2強誘電体材料膜18aにする工程と、パターニングによって強誘電体キャパシタ3を形成する工程と、を含む。

(もっと読む)

強誘電体キャパシタの製造方法、強誘電体メモリ装置の製造方法

【課題】良好な強誘電体キャパシタを効率よく製造する。

【解決手段】本発明の強誘電体キャパシタの製造方法は、第1電極33aと第2電極35aとの間に挟持された強誘電体膜34aを有する強誘電体キャパシタの製造方法であって、基板上方に、電極膜331を形成する工程と、電極膜331の表層を酸素分圧が2%以上の大気圧雰囲気で熱酸化して、酸化電極層332とする熱酸化工程と、電極層331上に、MOCVD法で強誘電体膜34aを形成するとともに、強誘電体膜34aの下地となる酸化電極層332を含む電極膜331を第1電極33aとする強誘電体膜形成工程と、強誘電体膜34a上に第2電極35aを形成する工程と、を有することを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】基板とゲート絶縁膜との界面近傍における窒素濃度を必要以上に高くすることなく、ゲート絶縁膜中の窒素濃度を高める。

【解決手段】電界効果トランジスタのゲート絶縁膜は、半導体基板に近い第1領域と、第1領域よりもゲート電極に近い第2領域とで窒素濃度のピークが異なっており、第1領域における窒素濃度のピークは、2.5atomic%〜10atomic%であり、第2領域における窒素濃度のピークは、第1領域における窒素濃度のピークよりも高い。

(もっと読む)

強誘電体メモリ装置の製造方法

【課題】水素バリア膜の下層との間においてエッチングの十分な選択比が得られると共に、コンタクトホールの形成工程を簡略化した強誘電体メモリ装置の製造方法を提供すること。

【解決手段】半導体基板上に強誘電体キャパシタ3を形成する工程と、強誘電体キャパシタ3を被覆する水素バリア膜12を形成する工程と、水素バリア膜12を被覆する層間絶縁膜13を形成する工程と、C4F8ガススとO2ガスとを少なくとも含む混合ガスを用いたエッチングにより層間絶縁膜13及び水素バリア膜12を貫通する貫通孔21を形成する工程とを備え、C4F8ガスの流量がO2ガスの流量に対して0.77倍以上3.8倍以下である。

(もっと読む)

ペロブスカイト型酸化物薄膜の成膜方法および積層体

【課題】(111)、(001)もしくは(110)のいずれかに配向したペロブスカイト型酸化物薄膜を容易に得る方法を提供する。さらに、このペロブスカイト型酸化物薄膜を下部電極として、その上に強誘電体薄膜等を積層することにより、優れた特性の強誘電体層等を得、これを有する半導体装置を提供しうる。

【解決手段】基板の(001)面に蛍石型構造のバッファー層、ついで結晶方位制御バッファー層を形成した後に、ペロブスカイト型酸化物薄膜を該結晶方位制御バッファー層上に積層して(111)、(001)もしくは(110)のいずれかに配向したペロブスカイト型酸化物薄膜を得る。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体膜の劣化を防止する。

【解決手段】本発明の半導体装置1は、基板21上方に順次設けられた第1電極32、強誘電体膜33、及び第2電極34を有する強誘電体キャパシタ3と、強誘電体キャパシタ3の上面及び側面を覆う水素バリア膜4と、水素バリア膜4及び基板21を覆う層間絶縁膜6と、層間絶縁膜6及び水素バリア膜4を貫通して第2電極34を露出させるコンタクトホール70と、第2電極34上を含むコンタクトホール70の内壁面70aを覆い、水素バリア性を有する導電材料からなるバリアメタル75と、コンタクトホール70内に埋設されたプラグ導電部7と、を備えている。水素バリア膜4におけるコンタクトホール70の内壁面は、コンタクトホール70の内側に向かって凹となる湾曲面となっており、水素バリア膜4におけるコンタクトホール70の内径は第2電極34に向かって小さくなる。

(もっと読む)

強誘電体メモリ装置の製造方法及び強誘電体メモリ装置

【課題】強誘電体材料において酸素欠損が発生することをより確実に防止できる強誘電体メモリ装置の製造方法及び強誘電体メモリ装置を提供すること。

【解決手段】半導体基板上に強誘電体キャパシタ3を形成する工程と、強誘電体キャパシタ3を被覆する水素バリア膜12を形成する工程と、水素バリア膜12に貫通孔21を形成する工程と、強誘電体キャパシタ3及び水素バリア膜12を被覆する第2層間絶縁膜13を形成する工程と、第2層間絶縁膜13に貫通孔21を形成する工程と、貫通孔21の内壁面及び強誘電体キャパシタ3の上面それぞれに密着層24を形成する工程と、貫通孔21内にプラグを形成する工程とを備え、貫通孔21が、貫通孔21の内側に形成されると共に、貫通孔21の内壁面が、被覆層24で被覆される。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体キャパシタの特性ばらつきを低減する。

【解決手段】本発明の製造方法は、基体上に第1電極32と強誘電体膜33と第2電極34とが順次積層された強誘電体キャパシタ3を形成する工程と、強誘電体キャパシタ3及び前記基体を覆って第1層間絶縁膜5を形成する工程と、第1層間絶縁膜5を覆って第2層間絶縁膜6の材料膜61を形成する工程と、材料膜61の上面側をCMP法で研磨することにより、強誘電体キャパシタ3上に位置する第1層間絶縁膜5を露出させる工程と、第1層間絶縁膜5を露出させる工程の後に、第1層間絶縁膜5を貫通して第2電極34を露出させるコンタクトホール70を形成する工程と、コンタクトホール70内に、第2電極34と導通するプラグ導電部を形成する工程と、を有する。第1層間絶縁膜5は、第2層間絶縁膜6と比して、CMP法による研磨速度が遅くなるようにする。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】金属酸化膜とその上下を挟む絶縁膜との相互拡散を抑制することにより、電荷蓄積膜に金属酸化膜を用いた不揮発性メモリセルの電荷保持特性を向上させることのできる技術を提供する。

【解決手段】メモリセルMC1に備わる電荷保持用絶縁膜4を、半導体基板1のチャネル領域側から、ボトム絶縁膜4a、金属酸化膜からなる電荷蓄積膜4c、およびトップ絶縁膜4eが順次形成された積層膜によって構成し、さらに、ボトム絶縁膜4aに対してプラズマ窒化処理を行うことにより、ボトム絶縁膜4a中の上面側に、ピーク値を有して窒素濃度が1原子%以上の窒化領域4bを形成し、その窒化領域4bの厚さを0.5nm以上、1.5nm以下、窒素濃度のピーク値を5原子%以上、40原子%以下、窒素濃度のピーク値の位置をボトム絶縁膜4aの上面から2nm以内とすることにより、ボトム絶縁膜4aと電荷蓄積層4cとの相互反応を抑制する。

(もっと読む)

キャパシタの検査方法及び半導体装置の製造方法

【課題】キャパシタにおける誘電体層の特性検査を容易にかつ正確に行うことができるようにしたキャパシタの検査方法と、このキャパシタの検査方法を用いた半導体装置の製造方法とを提供する。

【解決手段】基体上に第1電極膜51a、強誘電体材料膜52a、第2電極膜53aを形成する工程と、第2電極膜53a上にハードマスク60を形成する工程と、ハードマスク60をマスクにして第2電極膜53aと強誘電体材料膜52aとを順次パターニングし、上部電極53と強誘電体層52との積層構造と第1電極膜51aとからなるキャパシタ構造50を形成する工程と、第1電極膜51aと上部電極53との間に電圧を印加し、キャパシタ構造50における強誘電体層52の特性検査を行う工程と、を含むキャパシタの検査方法である。

(もっと読む)

圧電素子およびその製造方法、アクチュエータ、液体噴射ヘッド、並びに、強誘電体メモリ

【課題】アクチュエータ、液体噴射ヘッド、並びに、強誘電体メモリに用いられ、信頼性が高く、かつ圧電特性が良好な圧電素子およびその製造方法を提供する。

【解決手段】圧電素子100は、基体10と、基体10側から順に形成された下部電極層20、PZT,PZTN,PZTNS等を用いた圧電体層30および上部電極層40を有する積層体50と、積層体50の上方に空洞部62を介して形成され、水素などの還元種から、積層体50を保護する機能を有する酸化アルミニウムなどのバリア層70と、を含み、バリア層70は、少なくとも圧電体層30および上部電極層40と、接触していない。

(もっと読む)

401 - 420 / 686

[ Back to top ]