Fターム[5F083GA25]の内容

Fターム[5F083GA25]に分類される特許

481 - 500 / 686

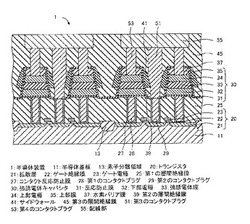

半導体装置及び半導体装置の製造方法

【課題】自己整合的に形成され、幅の減少を抑制可能なコンタクトプラグを有する半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体基板11と、半導体基板11にソース及びドレインとなる拡散層21がそれぞれ形成されたトランジスタ20と、下部電極32、強誘電体膜33、及び、上部電極34を順に有し、下部電極32が一方の拡散層21に接続され、上部電極34が配線部55に接続された強誘電体キャパシタ30と、強誘電体キャパシタ30の上面から下面に連なる側面に配設され、下端が下面より上面側に位置されたサイドウォール41と、サイドウォール41に接触して、一端を他方の拡散層21及び他端を配線部55とそれぞれ接続された第3のコンタクトプラグ51とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】強誘電体キャパシタを埋める層間絶縁膜上に配線層を形成する際に、層間絶縁膜上のAl2O3膜等の水素バリアを超えて生じる水素の侵入を抑制する半導体装置を提供する。

【解決手段】基板11上に第1の層間絶縁膜20を、テトラエトキシシランを原料とするプラズマCVD法により強誘電体キャパシタ18A,18B,18C,18Dを覆うように形成し、その上に水素バリア膜21を形成し、その上に配線パターン22A、22B、22Cを形成し、第2の層間絶縁膜22HDを高密度プラズマCVD法により堆積し、その上にシリコン酸化膜よりなる犠牲膜22PTをテトラエトキシシランを原料としたプラズマCVD法により堆積し、犠牲膜22HDを化学機械研磨法により第2の層間絶縁膜22HDが露出するまで研磨し、その際、犠牲膜22PTの第2の水分量が第2の層間絶縁膜22HDの第1の水分量よりも少ないようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体キャパシタを覆う絶縁膜内に形成されて、その強誘電体キャパシタの電極に接続される導電性プラグをコンタクトホール内に埋め込む際に、工程増を抑制しながら、コンタクトホールの下への水素の浸入を防止する構造を備えた半導体装置を提供する。

【解決手段】絶縁膜20内であってキャパシタ上部電極18の上に形成されたコンタクトホール20e内に埋め込まれる導電性プラグ21eとして、アルミニウム膜32を有する複数層31〜34の構造を採用し、これにより、タングステン膜34をコンタクトホール20e内に充填する際に、水素がコンタクトホール20eの下の強誘電体キャパシタ17aに侵入することをアルミニウム膜32によって防止する。

(もっと読む)

ルテニウムベースの膜を基板上に形成するための方法

半導体製造プロセスにおいて基板上に膜を形成する方法であって、反応チャンバーと、該チャンバー中の基板とが準備される。少なくとも2つの不燃性フッ素化溶媒の混合物中に溶解された四酸化ルテニウムを含むルテニウムベースの前駆体が提供され、ルテニウム含有膜が該基板上に作られる。 (もっと読む)

半導体装置およびその製造方法

【課題】強誘電体キャパシタの水素や水分による劣化を抑制するFeRAMを提供する。

【解決手段】FeRAMの強誘電体キャパシタ4をAlO膜11で覆うことにより、水素や水分が強誘電体キャパシタ4に到達するのをブロックする。さらに、強誘電体キャパシタ4の周辺に、FeRAMの電気伝導には寄与しないダミープラグ40を設けることにより、ダミープラグ40を設けなかった場合に比べて第2層間絶縁膜12の体積を減らし、第2層間絶縁膜12に含まれる水分に起因した強誘電体キャパシタ4の劣化を抑える。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体キャパシタの疲労特性を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】PZT膜24aの形成では有機金属気相成長(MOCVD)法を採用し、その厚さを約5nmとする。PZT膜24bの形成でもMOCVD法を採用し、その厚さを約95nmとする。但し、PZT膜24aの組成とPZT膜24bの組成とを比較すると、PZT膜24bの組成において、Ti含有量が少なく、Zr含有量が多くなるように、原料ガスの供給量を調整する。PZT膜24cの形成では、例えば化学溶液堆積(CSD)法を採用し、その厚さを約20nmとする。但し、PZT膜24c中のPb含有量が、PZT膜24a及び24bよりも、化学量論組成に近くなるよう、原料ガスの供給量を調整する。例えば、Zr含有量及びTi含有量の総和と同程度とする。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率絶縁膜を備えていても、素子特性の劣化を防止することができる半導体装置およびその製造方法を提供することを可能にする。

【解決手段】半導体基板1と、半導体基板に離間して形成されたソース領域8aおよびドレイン領域8bと、ソース領域とドレイン領域との間の半導体基板上に形成された第1絶縁膜3と、第1絶縁膜上に形成された電荷蓄積膜4と、電荷蓄積膜上に形成された高誘電率材料で形成された第2絶縁膜5bと、第2絶縁膜上に形成された制御ゲート電極6と、三配位の窒素結合を有しかつ窒素の第二近接原子の少なくとも1つが窒素であるシリコン窒化層5a、5cと、を備え、電荷蓄積膜と前記制御ゲート電極との少なくとも一方がシリコンを含み、前記シリコン窒化層は、第2絶縁膜と、電荷蓄積膜および制御ゲート電極のうちのシリコンを含む方との界面に設けられている。

(もっと読む)

半導体基板、および半導体装置の製造方法

【課題】層間絶縁膜中にビアプラグをダマシン法により形成する半導体装置の製造工程において、ウェハ中心部からとられた半導体装置でもウェハ周辺部からとられた半導体装置でもビアプラグの長さが一定となる製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体ウェハ上に第1の層間絶縁膜を形成する工程と、前記第1の層間絶縁膜を、第1の条件で化学機械研磨する工程と、前記第1の層間絶縁膜上に第2の層間絶縁膜を形成する工程と、前記第2の層間絶縁膜を、第2の条件で化学機械研磨する工程と、を含み、前記第1の条件と前記第2の条件とは、前記第1の層間絶縁膜と前記第2の層間絶縁膜の膜厚の総和が、前記半導体ウェハの中心部においても周辺部においても、略等しくなるように設定される。

(もっと読む)

キャパシタおよびその製造方法

【課題】誘電体の無機酸化物の還元を抑制し、誘電体の特性を阻害しないバリア層を備えた、漏れ電流の少ないキャパシタ、およびその容易な製造方法を提供すること。

【解決手段】(A)下部電極を形成する工程と、(B)前記下部電極の上方に強誘電体または圧電体からなる誘電体層を形成する工程と、(C)前記誘電体層の上方に上部電極を形成する工程と、(D)前記誘電体層および前記上部電極をパターニングする工程と、(E)前記誘電体層の少なくとも側面を被覆するように第1酸化シリコン層を形成する工程と、(F)酸素を含むプラズマによる処理を行う工程と、(G)少なくとも前記第1酸化シリコン層の上方に第2酸化シリコン層を形成する工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート構造の小型化に対応しやすく、製造が容易な3次元構造のゲート絶縁膜を有する半導体装置の提供を課題とする。

【解決手段】本発明の半導体装置は、半導体基板に3次元構造のゲート絶縁膜が形成され、ゲート絶縁膜に接するゲート電極が半導体基板上に突出形成され、ゲート絶縁膜の周囲の半導体基板に該半導体基板の拡散層領域を介してソース電極およびドレイン電極が形成され、ゲート電極周囲の半導体基板上面が、半導体基板上に突出形成されたゲート電極の側面を覆う保護絶縁膜で覆われ、この保護絶縁膜の上に層間絶縁膜が積層されてなる。

(もっと読む)

記憶装置及び半導体装置

【課題】記憶機能の信頼性の高い有機化合物を含む層を有する素子が設けられたフレキシブルな記憶装置及び半導体装置を提供する。

【解決手段】第1の電極層及103び第2の電極層106からなる一対の電極間に有機化合物を含む層105を有する記憶素子と、当該記憶素子を有する素子層と、素子層上に形成される封止層111を有し、封止層111には吸湿材108が含まれている記憶装置及び半導体装置である。吸湿材108としては、溶融シリカ、結晶シリカ、アルミナ、窒化珪素、窒化アルミニウム、窒化ホウ素、ゼオライト、アルカリ土類金属の酸化物、硫酸塩、または高吸水性ポリマーの粒子で形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】 メモリセル部を保護するための被覆絶縁膜の膜質を改善することができ、メモリセル部の電荷保持特性の向上をはかる。

【解決手段】 半導体基板11上にゲート絶縁膜12を介してゲート電極13,18が形成されたトランジスタ構造の不揮発性メモリセルの表面部を被覆絶縁膜26で覆った不揮発性半導体装置であって、被覆絶縁膜26はシリコン窒化膜又はシリコン酸窒化膜からなり、被覆絶縁膜26中のN−H結合の密度とSi−H結合の密度との比(N−H/Si−H)を3以下に設定した。

(もっと読む)

非揮発性メモリ素子及びその製造方法

【課題】高誘電体膜の電気的な特性を向上させる事ができる非揮発性メモリ素子及びその製造方法を提供する。

【解決手段】フローティングゲート104とコントロールゲート122間誘電体120として、酸化膜108,116の間に高誘電絶縁膜112を含む高誘電体膜を形成し、高誘電絶縁膜の上部及び下部、またはフローティングゲートの上部及びコントロールゲートの下部に窒素含有絶縁膜106,110,114,118を形成することにより、酸化膜と高誘電絶縁膜との間、または酸化膜とフローティングゲートまたはコントロールゲートとの間の界面反応を抑制し、高誘電体膜の誘電率、漏洩電流、絶縁破壊電圧及び電荷保存特性などの電気的な特性を向上させ、高性能及び高信頼性の高誘電体膜を製造することができる。

(もっと読む)

多重拡散防止膜を備える半導体素子

【課題】ゲートスタックのシート抵抗及びコンタクト抵抗が小さいながらも、不純物の外部拡散を効果的に抑制することのできる拡散防止膜を備える半導体素子を提供すること。

【解決手段】第1導電層(211)と、第1導電層(211)上に形成され、且つ金属シリサイド膜(212A)及び窒素含有の金属膜(212B)の順に積層された第1拡散防止膜と、該第1拡散防止膜上の少なくとも窒素含有の金属シリサイド膜(212D)を含む第2拡散防止膜と、該第2拡散防止膜上の第2導電層(213)とを備える。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】水分の浸透を防止するシリコン窒化膜を寄生容量が増大しないように設ける不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】シリコン基板1に、ゲート絶縁膜6、浮遊ゲート電極膜7、ONO膜やNONON膜などの電極間絶縁膜8、制御ゲート電極膜9および加工用ハードマスク材10を積層してエッチング加工することによりゲート電極MGを形成する。浮遊ゲート電極膜7の上面位置までシリコン酸化膜11を埋め込み、その上にホウ素を含有した比誘電率が小さいシリコン窒化膜(SiBN)12を成膜する。この上にシリコン酸化膜13を成膜する。この構成で、シリコン窒化膜12は、水分の浸透を防止し、しかも、浮遊ゲート電極膜7や制御ゲート電極膜9の間に位置せずしかも比誘電率が小さいので寄生容量の増大を抑制できる。

(もっと読む)

多重拡散防止膜を備える半導体素子の製造方法

【課題】ゲートスタックのシート抵抗及びコンタクト抵抗が小さいながらも、不純物の外部拡散を効果的に抑制することのできる拡散防止膜を備える半導体素子の製造方法を提供すること。

【解決手段】本発明に係る半導体素子の製造方法は、第1導電層(21)上に、少なくとも第1金属膜(22A)および窒素含有の金属シリサイド膜(22C)を含む積層構造で拡散防止膜を形成するステップと、該拡散防止膜上に第2導電層(23)を形成するステップとを含む。

(もっと読む)

半導体装置の製造方法

【課題】歩留まりを向上させることが可能な強誘電体キャパシタを備えた半導体装置の製造方法を提供する。

【解決手段】第2導電膜43の上にマスク材料膜45を形成する工程と、マスク材料膜45の上にレジストパターン46を形成する工程と、IPCエッチングチャンバ内においてマスク材料膜45をエッチングして補助マスク45aにする工程と、エッチングチャンバからシリコン基板20を取り出さずに、エッチングチャンバ内において第2導電膜43をエッチングすることによりパーティクル数の増加傾向を抑制して、第2導電膜43を上部電極にする工程と、強誘電体膜42をパターニングしてキャパシタ誘電体膜にする工程と、第1導電膜41をパターニングして下部電極にし、下部電極、キャパシタ誘電体膜、及び上部電極でキャパシタQを構成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置およびその製造方法

【課題】立体スタック型の誘電体メモリにおける上部電極の電位を配線層へ引き出す構造においてより集積度を上げ、尚且つ、信頼性を高くする。

【解決手段】半導体基板300の上に形成された容量素子321の上部電極313が、同じく半導体基板300の上に形成された接合構造体331の第1導電膜315、第1コンタクトプラグ306、第2不純物拡散層303及び第3コンタクトプラグ317を介して、上方に形成された上部配線318と電気的に接続している。該接合構造体331は、第2層間絶縁膜307に設けられた第2凹部309の側壁に形成された誘電体膜314を備え、第2凹部309の底面において、第1導電膜315は、第1コンタクトプラグ306と電気的に接続する。

(もっと読む)

半導体装置の製造方法

【課題】歩留まりを向上させることが可能な強誘電体キャパシタを備えた半導体装置の製造方法を提供する。

【解決手段】下地絶縁膜37の上に、第1導電膜41、強誘電体膜42、及び第2導電膜43を順に形成する工程と、第2導電膜43をパターニングして上部電極43aにする工程と、強誘電体膜42の上にレジストパターンを形成する工程と、レジストパターンをマスクにしながら、ハロゲンガスを含むエッチングガスを用いて強誘電体膜42をエッチングすることにより、キャパシタ誘電体膜42aを形成する工程と、レジストパターンを除去する工程と、キャパシタ誘電体膜42aの側面を水洗する工程と、第1導電膜41をパターニングして下部電極にし、該下部電極、キャパシタ誘電体膜42a、及び上部電極43aでキャパシタQを構成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】ハードマスクを使用して金属膜、絶縁膜等の膜をパターニングする工程を含むFeRAM等の半導体装置の製造方法において、ハードマスクを用いて膜をパターニングした後の基板上の残渣、スカム等をさらに減らす製造方法を提供する。

【解決手段】パターニングの対象となるIrO2からなる第1の導電膜15の上に、アルミナ膜の犠牲膜16を介してTiNなどの窒化物のハードマスク17aを形成し、その後に、ハードマスク17aに覆われない領域の第1の導電膜15をパターニングし、その後に、犠牲膜16をフッ化アンモニウム、アミド、有機酸、有機酸塩類、水の混合液を使用したウェット処理により除去することにより、ハードマスク17aを第1の膜15のパターンの上から剥離してハードマスク17aの表面に付着した残渣、スカム等が再付着する防止工程を有している。

(もっと読む)

481 - 500 / 686

[ Back to top ]