Fターム[5F083GA28]の内容

Fターム[5F083GA28]に分類される特許

141 - 160 / 550

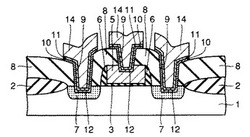

半導体装置およびその製造方法

【課題】半導体装置の微細化に対処しうる、製造が容易で安価な低コンタクト抵抗の半導体装置およびその製造方法を得る。

【解決手段】Si基板(1)上の不純物領域(7)を覆うように層間絶縁膜(8)が形成され、その層間絶縁膜(8)には、層間絶縁膜(8)を貫通して不純物領域(7)を掘り込むようにコンタクトホール(9)が形成されている。コンタクトホール(9)内には、金属膜(10)、バリア層(11)、金属シリサイド(12)およびソース、ドレイン配線(14)が形成されている。ソース、ドレイン配線(14)は、タングステンから形成されている。

(もっと読む)

不揮発性半導体メモリ

【課題】 従来のMONOSは、SiNに電荷を蓄積する構成であるが、電荷蓄積量が不十分であり閾値電圧変化幅を大きく取れず、またHfO2,ZrO2,TiO2中へLa系元素を導入した技術ではドーパント導入による電荷の高密度化は実現が困難である。

【解決手段】 窒化シリコン膜よりも十分に誘電率の高いZr酸化物、Hf酸化物等の窒化シリコンよりも十分に高い誘電率を有する金属酸化物を母体材料として、その中に電子の出し入れが可能なトラップレベルを発生させるために、価数が2つ上(VI価)以上の高価数物質を適量添加する構成の電荷蓄積層を有する不揮発性半導体メモリである。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は補償容量部を設けたDRAMなどの半導体装置に関する。

【解決手段】本発明は、半導体基板の一面に形成された主トレンチ溝内に、ゲート絶縁膜を介しゲート電極が形成され、その両側にソース/ドレイン領域が形成されてなる主トランジスタ構造と、半導体基板の一面に形成された副トレンチ溝内に、ゲート絶縁膜を介しゲート電極が形成され、その両側にソース/ドレイン領域が形成されてなる補償容量用トランジスタ構造とが半導体基板に個々に形成され、主トランジスタ構造の主トレンチ溝の延在方向と補償容量用トランジスタ構造の副トレンチ溝の延在方向が平面視的に交差する方向に設定され、補償容量用トランジスタ構造のゲート絶縁膜周囲のチャネル領域に不純物拡散領域が形成されて補償容量トランジスタ構造の閾値電圧が主トランジスタ構造の閾値電圧より低くされてなることを特徴とする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のトランジスタ160と、第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成され、第1のトランジスタ160のゲート電極と、第2のトランジスタ162のソース・ドレイン電極とは、電気的に接続され、第1の配線と、第1のトランジスタ160のソース電極とは、電気的に接続され、第2の配線と、第1のトランジスタ160のドレイン電極とは、電気的に接続され、第3の配線と、第2のトランジスタ162のソース・ドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のトランジスタ162のゲート電極とは、電気的に接続される。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】注入マスクの低減が図られる半導体装置の製造方法と、そのような半導体装置を提供する。

【解決手段】レジストマスク31と他のレジストマスクを注入マスクとして、NMOS領域RNにボロンを注入することにより、アクセストランジスタおよびドライブトランジスタのハロ領域となるp型不純物領域が形成される。さらに他のレジストマスクを注入マスクとして、PMOS領域RPにリンまたは砒素を注入することにより、ロードトランジスタのハロ領域となるn型不純物領域が形成される。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

半導体装置及びその製造方法

【課題】不揮発性メモリを用いた半導体装置において、消去動作の高速化及び低消費電力化を実現する。

【解決手段】チャネル形成領域、トンネル絶縁膜及び浮遊ゲートを順に積層した不揮発性メモリにおいて、チャネル形成領域を酸化物半導体層により構成する。さらに、チャネル形成領域の下側に、浮遊ゲートと対向する位置に消去用の金属配線を設けた構造とする。上記構造により、消去動作において、浮遊ゲートに蓄積された電荷はチャネル形成領域を介して金属配線に引き抜かれる。これにより、半導体装置の消去動作を高速化し、低消費電力化を実現できる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 低コストで、生産性及び歩留まりに優れる構造の不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】

メモリセル選択用のトランジスタが形成された基板上の同一層の第1の金属配線119及び第2の金属配線121上に、夫々、第1の開口部128及び第2の開口部129を同時に形成する。次に可変抵抗体124と上部電極126を、第1の開口部128内は上部電極126により完全に充填されるが、第2の開口部129内は完全に充填されることのないように全面に堆積する。その後、第2の開口部の底部に第2の金属配線121の表面が露出するまでエッチバックを行うことで、第1の開口部128内に可変抵抗素子104を、第2の開口部129内に第3の金属配線(ビット線)120と接続するための導通孔を、同時に形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】電荷保持特性の良好な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体層SMLと、半導体層に対向して設けられた第1絶縁層I1と、半導体層と第1絶縁層との間に設けられた第2絶縁層I2と、第1絶縁層と第2絶縁層との間に設けられた機能層I3と、第1絶縁層の半導体層とは反対の側に設けられ、互いに離間した第1ゲート電極G1及び第2ゲート電極G2と、を備えた不揮発性半導体記憶装置が提供される。機能層のうちの第1ゲート電極に対向する第1領域R1、及び、機能層のうちの第2ゲート電極に対向する第2領域R2の電荷蓄積能は、機能層のうちの第1領域と第2領域との間の第3領域R3とは異なる。

(もっと読む)

半導体記憶装置

【課題】メモリセルに負の閾値電圧を設定することができ、しかも安定な動作が可能な半導体記憶装置を提供する。

【解決手段】ワード線、及びビット線に接続された複数のメモリセルがマトリックス状に配置され、前記メモリセルに負の閾値電圧を設定することが可能なメモリセルアレイと、前記ワード線、及びビット線の電位を制御する制御回路と、前記制御回路は、前記ビット線のうち第1のビット線BLoに接続されたメモリセルから負の閾値電圧の読み出し動作を行なう場合、前記第1のビット線に隣接して配置された第2のビット線BLeと、前記メモリセルアレイが形成されたウェルと、前記メモリセルアレイのソース線SRCに、正の第1の電圧Vfixを供給し、選択セルのワード線に前記第1の電圧より低い正の電圧を供給する。

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜を除去するエッチング中に、異常エッチングを防止する。エッチング工程において加わる水圧や風圧によりガードリングの形状が変形して剥離し、欠陥が発生することを防止する。

【解決手段】半導体装置は、メモリセル領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた周辺回路領域と、ガードリング及び周辺回路領域上に設けられた支持体膜と、周辺回路領域内に設けられたコンタクトプラグとを有する。ガードリングとコンタクトプラグは、同一の導電材料から構成される。

(もっと読む)

専用のセレクタトランジスタが不要な自己選択式PCMデバイス

【課題】専用のセレクタトランジスタが不要な自己選択式PCMデバイスを提供する。

【解決手段】原子層堆積法(ALD)を使用して、亜鉛酸化物(ZnO)を層変化材料の上に堆積させることで、自己選択型記憶デバイスが形成される。ZnO/GST界面に形成されるダイオードは、PCMアーキテクチャ内で、整流能力と記憶能力の両方を示す。

(もっと読む)

不揮発性メモリセル、これを有するメモリアレイ、並びに、セル及びアレイの操作方法

【課題】自己収束消去動作を容易にすると共に保持状態の期間におけるメモリデバイスの電荷蓄積層内での電荷保持能力を保持してもいるトンネル誘電体構造を有する不揮発性メモリデバイスの提供。

【解決手段】半導体基板101であって、該基板の表面より下に配置され且つチャネル領域106によって分離されたソース領域102及びドレイン領域104を備えた半導体基板と、前記チャネル領域より上に配置されたトンネル誘電体構造102であって、低いホールトンネリング障壁高さを有する少なくとも1つの層を備えたトンネル誘電体構造と、前記トンネル誘電体構造より上に配置された電荷蓄積層130と、前記電荷蓄積層より上に配置された絶縁層140と、前記絶縁層より上に配置されたゲート電極150とを有するメモリセル、該メモリセルのアレイ及び操作方法と共に開示する。

(もっと読む)

半導体記憶装置

【課題】簡便な方法で書き込みが可能であり、しきい値特性の不安定性に対応した酸化物半導体を用いた半導体記憶装置を提供する。

【解決手段】酸化物半導体を用いた薄膜トランジスタが紫外線照射する事でしきい値シフトする特性を有していることを利用して半導体記憶装置とする。読み取り電圧を紫外線未照射のしきい値と照射後のしきい値の間に設定して読み取ることができる。初期特性におけるしきい値特性の制御にはバックゲートを備えることや2個の薄膜トランジスタを用いることで解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】水分又は水素の侵入による強誘電体キャパシタの性能劣化をより確実に防止できるとともに、製造工程数の増加を回避できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板110上にトランジスタTを形成した後、第1の絶縁膜121を形成する。次に、第1の絶縁膜121上に強誘電体キャパシタ130を形成し、その上に第2の絶縁膜131aを形成する。次に、第2の絶縁膜131aの上面を平坦化して強誘電体キャパシタ130の上部電極128aの上面と連続するようにした後、トランジスタTの不純物領域118に接続するプラグ133を形成する。その後、酸化アルミニウム等により水素バリア層134を形成し、その上に第3の絶縁膜131bを形成する。次いで、強誘電体キャパシタ130及びプラグ133に接続する配線137を形成する。

(もっと読む)

半導体ウエハ、半導体ウエハの製造方法、および半導体装置

【課題】ヒューズ素子形成領域の配線を露出させることなく、クラックストップトレンチとボンディングパッド開口部を同時に形成する半導体ウエハ及びその製造方法を提供する。

【解決手段】半導体基板と多層配線構造とを少なくとも具備してなり、前記多層配線構造がチップ領域Aとヒューズ素子形成領域Bおよびダイシング領域Cとに渡って形成されてなる半導体ウエハにおいて、前記チップ領域に位置する前記多層配線構造上には、前記配線で構成されたボンディングパッド170が形成される一方、前記ダイシング領域には、前記多層配線構造が一部除去されることによって形成された二本以上が並行して並ぶダミーリングおよび、前記ダミーリング間に形成された、クラックストップトレンチ152となる溝部が設けられていることを特徴とする半導体ウエハを採用する。

(もっと読む)

メモリ素子及びその動作方法

【課題】メモリ素子及びその動作方法を提供する。

【解決手段】メモリセルを含み、該メモリセルは、バイポーラメモリ要素及び双方向スイッチング要素を含み、該双方向スイッチング要素は、該バイポーラ・メモリ要素の両端に連結され、該双方向スイッチング要素は、第1スイッチング要素及び第2スイッチング要素を含み、該第1スイッチング要素は、該バイポーラ・メモリ要素の一端に連結され、第1スイッチング方向を有することができ、該第2スイッチング要素は、該バイポーラ・メモリ要素の他端に連結され、第2スイッチング方向を有することができ、該第2スイッチング方向は、該第1スイッチング方向に反対方向でありうる。

(もっと読む)

半導体装置の製造方法

【課題】配線層の加工マージンが大きく、微細化に適した半導体装置の製造方法を提供する。

【解決手段】半導体基板1にゲート電極溝を形成する工程と、ゲート電極溝の内壁面にゲート絶縁膜15を形成する工程と、ゲート電極溝の底部に埋め込みゲート電極23Aを形成する工程と、埋め込みゲート電極23Aの上面を覆うようにゲート電極溝の内部に絶縁膜を埋め込んだ後、エッチバックして当該ゲート電極溝の上部にキャップ絶縁膜22を形成する工程と、半導体基板1の上面に層間絶縁膜24を形成する工程と、層間絶縁膜24にビットコンタクト開口部を形成する工程と、を備え、半導体基板1の上面に層間絶縁膜24を形成する工程が、半導体基板1の上面とキャップ絶縁膜22の上面との間に生じた段差を埋め込むように層間絶縁膜24を成膜するとともに当該層間絶縁膜24の上面を平坦とすることを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量コンタクトプラグとキャパシタとの間の重ねマージンを十分に確保して、接続信頼性の高い半導体装置を提供する。

【解決手段】埋め込みゲート電極23Aと、半導体基板1上に設けられてビット線30を有する絶縁層33と、絶縁層33を貫通するように設けられた容量コンタクトプラグ41と、絶縁層33上に設けられて容量コンタクトプラグ41及びキャパシタの下部電極46と接続される容量コンタクトパッド42とを備え、容量コンタクトプラグ41が、半導体基板1側からポリシリコン層38a、シリサイド層39a、金属層からなる積層構造であり、容量コンタクトパッド42の底面と金属層の上面との接続部分以外の当該金属層の上面が、絶縁層33の上面からリセスされるとともに、シリサイド層39aの上面が、金属層によって被覆されていることを特徴とする半導体装置を選択する。

(もっと読む)

141 - 160 / 550

[ Back to top ]