Fターム[5F083GA28]の内容

Fターム[5F083GA28]に分類される特許

161 - 180 / 550

半導体装置及び半導体装置の製造方法

【課題】容量コンタクトプラグとキャパシタとの間の重ねマージンを十分に確保して、接続信頼性の高い半導体装置を提供する。

【解決手段】埋め込みゲート電極23Aと、半導体基板1上に設けられてビット線30を有する絶縁層33と、絶縁層33を貫通するように設けられた容量コンタクトプラグ41と、絶縁層33上に設けられて容量コンタクトプラグ41及びキャパシタの下部電極46と接続される容量コンタクトパッド42とを備え、容量コンタクトプラグ41が、半導体基板1側からポリシリコン層38a、シリサイド層39a、金属層からなる積層構造であり、容量コンタクトパッド42の底面と金属層の上面との接続部分以外の当該金属層の上面が、絶縁層33の上面からリセスされるとともに、シリサイド層39aの上面が、金属層によって被覆されていることを特徴とする半導体装置を選択する。

(もっと読む)

MOS型半導体メモリ装置、その製造方法およびコンピュータ読み取り可能な記憶媒体

【課題】 電荷蓄積領域として機能する絶縁膜積層体のバンドギャップ構造を長期間維持し、優れたデータ保持特性と、高速でのデータ書換え性能と、低消費電力での動作性能と、高い信頼性と、を同時に兼ね備えたMOS型半導体メモリ装置を提供する。

【解決手段】 MOS型半導体メモリ装置601は、大きなバンドギャップを持つ第1の絶縁膜111および第5の絶縁膜115と、最も小さなバンドギャップを持つ第3の絶縁膜113との間に、両者の中間の大きさのバンドギャップを持つ第2の絶縁膜112および第4の絶縁膜114を備えている。第2の絶縁膜112と第3の絶縁膜113との間には、第1のブロック層112Bが設けられ、第3の絶縁膜113と第4の絶縁膜114との間には、第2のブロック層113Bが設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】データ保持特性の良好な不揮発性メモリおよびその製造技術を提供する。

【解決手段】ゲート絶縁膜6上に多結晶シリコン膜7および絶縁膜8を順次堆積し、これら多結晶シリコン膜7および絶縁膜8をパターニングしてゲート電極7A、7Bを形成した後、ゲート電極7A、7Bの側壁に酸化シリコン膜からなるサイドウォールスペーサ12を形成する。その後、基板1上にプラズマCVD法で窒化シリコン膜19を堆積することにより、ゲート電極7A、7Bと窒化シリコン膜19とが直接接しないようにする。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタの性能を良好にするとともに、トランジスタにより構成されたアンチヒューズのゲート絶縁膜の破壊後の特性を良好にする。

【解決手段】アンチヒューズ素子190として機能するNMOSトランジスタにおいて、N型チャネル領域112aが設けられている。また、通常のNMOSトランジスタ194には、N型エクステンション領域120およびP型ポケット領域122が設けられているが、アンチヒューズ素子190には、エクステンション領域およびポケット領域が設けられない。

(もっと読む)

半導体装置

【課題】書き込みおよび消去特性が良好で、記憶情報の不揮発性が高い不揮発性記憶装置を提供する。

【解決手段】不揮発性記憶装置は、第1不純物領域1、第2不純物領域2、並びに第1不純物領域1および第2不純物領域2のいずれとも離間して形成された一組のソース領域3およびドレイン領域4、が区画された半導体基板10と、半導体基板10の上に形成された絶縁膜と、フローティングゲート30と、を有し、フローティングゲート30は、平面視において、第1部分31は第1不純物領域1に重複し、第2部分32は第1不純物領域1および第2不純物領域2の間に位置し、第3部分33は一組のソース領域3およびドレイン領域4の間に位置し、フローティングゲート30の第3部分33と半導体基板10との間に位置する絶縁膜は、フローティングゲート30の他の部分と半導体基板10との間に位置する絶縁膜よりも厚みが大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体キャパシタの下部電極材料の選択自由度が高く、ビア工程の少ない半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板101上に形成されたスイッチングトランジスタ301A,301Bと、拡散層121と、トランジスタ301上に形成された層間絶縁膜131と、下部電極211、強誘電体膜212、及び上部電極213を含む強誘電体キャパシタ201A,201Bと、上部電極213の上方に形成された配線層141と、上部電極213と配線層141とを電気的に導通させる第1のプラグTWと、拡散層121と配線層141とを電気的に導通させる第2のプラグV1A,V1Bと、下部電極211の側方に配置されており、下部電極211と拡散層121とを電気的に導通させる第3のプラグCSFとを備える。

(もっと読む)

半導体記憶装置

【課題】メモリセルアレイ全体の消費電力を削減することが可能であり、且つ高集積化の可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ワード線1と、ワード線1と交差するように配置されたビット線2と、ワード線1とビット線2との各交差部に配置された絶縁膜3と、ワード線1の間及びビット線2の間を埋め込む層間絶縁膜と、ビット線1に接続され、低抵抗状態と高抵抗状態との間で遷移する抵抗変化材4とを備える。ワード線1、ビット線2、及び絶縁膜3はワード線1とビット線2との各交差部において電界効果トランジスタを構成する。電界効果トランジスタ及び抵抗変化材4はメモリセルを構成する。ビット線2は、絶縁膜を介してワード線1と対向する第1面と、この第1面とは反対側の第2面とを有する。抵抗変化材4は、第2面と接するように配置され、且つその一部が層間絶縁膜と接触している。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 低コストで、生産性及び歩留まりに優れる構造の不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】

基板上の第1の金属配線119上に第1の開口部128を、第2の金属配線121上に第2の開口部129を同時に形成する。次に導電膜120を全面に堆積すると、開口面積の小さな第1の開口部内において、堆積される導電膜の膜厚に不均一が生じ、第1の開口部の底部と側壁部の境界部分に、膜厚が薄く堆積される局所薄膜領域が生じる。当該局所薄膜領域の導電膜が完全に酸化されるが、底部及び側壁部上には未酸化の導電膜が残存するような膜厚で導電膜を酸化させることにより、第1の開口部128内において、底部の導電膜122と側壁部の導電膜126が導電膜の酸化膜である可変抵抗体を介して分離され、可変抵抗素子104が形成される。一方、第2の開口部内には導電膜と第2の金属配線を接続するコンタクトが形成される。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】金属配線上にダイオード等の選択素子を有し、選択素子と相変化メモリ等の記憶素子とを共に積層することにより、高性能化、高信頼化を実現し、製造コストを低減する半導体記憶装置とその製造方法を提供する。

【解決手段】第1、第2、第3ポリシリコン膜119,120,121によるダイオードDIODの上に、バッファ層122、相変化材料層123が形成され、層間膜127bより熱伝導率の高いダイオードDIODの一部分を加工せずに配線上に延在させて残すことにより、ダイオードDIODで発生する熱の散逸を大きくする。また、ダイオードDIODの一部をエッチストッパとして利用することで、積層化時のコンタクト開口を一括で行うことを可能とする。

(もっと読む)

半導体装置

【課題】素子特性の劣化を可及的に防止することのできる半導体装置を提供する。

【解決手段】半導体基板51と、半導体基板上に設けられたゲート絶縁膜53と、ゲート絶縁膜上に設けられた第1ゲート電極54aと、第1ゲート電極上に設けられ金属および酸素を含む電極間絶縁膜55と、電極間絶縁膜上に設けられた第2ゲート電極54bと、第1および第2ゲート電極の両側の半導体基板に設けられたソース/ドレイン領域58a、58bと、を備え、電極間絶縁膜55は、リン、砒素、アンチモン、ビスマスのうちから選択された少なくとも1つの添加元素を含み、その含有量が0.1at%以上3at%以下である。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】回路構成を複雑化することなくソフトエラー低減化を図ったメモリセル構造を有する半導体記憶装置を得る。

【解決手段】NMOSトランジスタN1及びPMOSトランジスタP1によるインバータI1(出力部が記憶端子Na)とNMOSトランジスタN2及びPMOSトランジスタP2によるインバータI2(出力部が記憶端子Nb)とが交叉接続され、さらにNMOSトランジスタN3及びN4が記憶端子Na及びNbにそれぞれ接続される。記憶端子Naに一方電極が接続されるNMOSトランジスタN1及びN3はPウエル領域PW0及びPW1に分けて形成されるともに、記憶端子Nbに一方電極が接続されるNMOSトランジスタN2及びN4はPウエル領域PW1及びPW0に分けて形成される。Pウエル領域PW0及びPW1はNウエル領域NWを挟んで各々反対側に形成される。

(もっと読む)

半導体装置の製造方法

【課題】 STIを利用して形成した素子分離膜がウエットエッチング工程により目減りすることを出来るだけ抑制しながら半導体装置を製造する。

【解決手段】 犠牲酸化膜の形成とウエットエッチングによる剥離、及び/又は、二酸化珪素膜の形成とウエットエッチングによる剥離を行う半導体装置の製造プロセスにおいて、犠牲酸化膜及び/又は二酸化珪素膜の形成を、プラズマ処理装置の処理容器内で、酸素を含む処理ガスを用いて生成させたO(1D2)ラジカルが支配的なプラズマにより行う。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化を簡易に実現する、キャパシタを備える半導体装置を提供する。

【解決手段】半導体装置は、半導体基板10と、半導体基板10上に形成され、且つ、開口部OPを有する絶縁層20と、絶縁層20上に形成された第1キャパシタCAP1及び第2キャパシタCAP2と、を備える。絶縁層20の上面は、開口部OPの内壁面の少なくとも一部を含む第1上面と、第1上面と比較して半導体基板からより離れている第2上面と、を含む。第1キャパシタCAP1は、第1上面上に形成された第1下部電極51と、第1下部電極51上に誘電体膜60を介して形成された上部電極70と、を備える。第2キャパシタCAP2は、第2上面上に形成され第1下部電極51と電気的に分離された第2下部電極52と、第2下部電極52上に誘電体膜60を介して形成された上部電極70と、を備える。

(もっと読む)

三次元メモリアレイ積層構造体

【課題】 改善された三次元メモリ(例えば、RRAM)アーキテクチャを提供すること。

【解決手段】 メモリデバイスが、平面基板と、平面基板の上方の複数の水平な導電性平面と、複数の水平な導電性平面と交互に配置される複数の水平な絶縁層とを備える。複数の導電性平面および絶縁層と直角である垂直な導電性列のアレイが、複数の導電性平面および絶縁層における開口部を通過する。メモリデバイスは、複数のプログラム可能なメモリ素子を備え、それぞれのメモリ素子が、水平な導電性平面の1つをそれぞれの垂直な導電性列に連結する。

(もっと読む)

半導体装置

【課題】半導体装置の歩留まりを向上させること若しくは製造コストを低減すること又は集積回路の面積を低減する半導体装置を提供する。

【解決手段】半導体装置が有するメモリ素子10のメモリ層12及び抵抗素子20の抵抗層22が同一材料によって構成される。そのため、メモリ層12と、抵抗層22とを同一工程によって形成することで、半導体装置の作製工程数を低減することができる。結果として、半導体装置の歩留まりを向上させること又は製造コストを低減することができる。また、半導体装置は、抵抗値の高い抵抗成分を備えた抵抗素子20を有する。そのため、半導体装置が有する集積回路の面積を低減することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】PMOS領域における素子分離膜のライナー窒化膜の除去を行う従来技術による問題を解決した半導体装置およびその製造方法を提供すること。

【解決手段】半導体装置の製造方法は、基板20をエッチングして複数のトレンチを形成するステップと、複数のトレンチ内に第1絶縁膜24Aを埋め込んで第1素子分離膜を形成するステップと、一部のトレンチ(CELL又はPERI NMOS領域のトレンチ)内に埋め込まれた第1絶縁膜24Aをリセスするステップと、リセスされたトレンチの全面にライナー膜26A、27Aを形成するステップと、ライナー膜26A、27Aが形成されたトレンチ内に第2絶縁膜28を埋め込んで第2素子分離膜を形成するステップとを含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】製造工程の簡略化および製造時間短縮を目的とする、メモリセルと周辺回路を備える半導体装置と製造方法を提供する。

【解決手段】トランジスタ形成層30上に、内部に配線10bを備え、かつ、表面に容量パッド14a,14bを有する絶縁層32を形成する工程と、絶縁層32を層間絶縁膜16で覆い、層間絶縁膜16を貫通する第一のホール16aと、第一のホール16aよりも大きい直径を有する第二のホール16bおよび第三のホール16cを、それぞれメモリセル部と周辺回路部に同時に形成する工程と、各ホール内を覆う下部電極18と容量絶縁膜19と上部電極20と容量サポート21を形成することにより第一のホール16aを充填するとともに、第二のホール16bと第三のホール16c内側に空洞を形成する工程と、空洞内に、配線10bと容量パッド14bにそれぞれ接続するコンタクト16d,16eを形成する工程と、を具備している。

(もっと読む)

半導体集積回路装置

【課題】MISFETのソース/ドレイン間の寄生容量を減少させる電極および配線を有したメモリや、メモリ混載のロジック等の半導体集積回路を提供する。

【解決手段】ゲート電極5より上方に少なくともキャパシタ電極14,16または情報記憶部の一部を有する半導体集積回路装置において、MISFETは、ソース・ドレイン拡散層7に接続する少なくとも1つずつの第1のプラグ9を有する。ソース・ドレイン拡散層7のどちらか一方に、第1のプラグ9を介して接続し、キャパシタまたは情報記憶部の一部の下部電極14と同一工程またはそれより前工程の配線層から成る第1の配線21を設け、一方のソース・ドレイン拡散層7の上方に第1の配線21と他の配線22を接続するプラグを設けず、また、ソース・ドレイン拡散層7の他方の領域の上方に第1の配線21と同一工程の配線を設けないようにする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】少ない工数の追加でロジック回路とメタル容量素子とを混載し、かつ、ロジック動作特性の劣化を生じることがない半導体装置の製造方法を提供する。

【解決手段】基板11上に第1層間絶縁膜13を形成し、第1層間絶縁膜13に導電体柱14A、14Bを形成する。第1層間絶縁膜13の上面に溝配線部絶縁膜15を形成する。導電体柱14Bの上方において溝配線部絶縁膜15を除去して容量用開口部151を形成し、第1層間絶縁膜15の上面に容量素子用絶縁膜16を形成する。導電体柱14Aの上方において容量素子用絶縁膜16および第1層間絶縁膜15を除去して配線用溝152を形成する。容量用開口部151および配線用溝152に金属体17A、17Bを埋め込む。容量用開口部152の金属体17Aを容量素子の上部電極とし、配線溝152の金属体17Bをロジック配線とする。

(もっと読む)

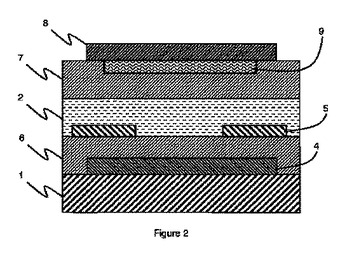

有機デュアルゲートメモリおよびその製造方法

有機メモリデバイスは、第1のゲート電極(4)と、第1のゲート誘電体(6)と、有機半導体材料(2)と、第2のゲート誘電体(7)と、第2のゲート電極(8)とを備えるデュアルゲートトランジスタである。ソース・ドレイン電極(5)が、有機半導体材料(2)中に配置されるとともに、電極間表面を規定する。捕捉領域(9)が、有機半導体材料(2)とゲート電極(4,8)のうちの一方との間に配置されるとともに、ゲート電極(4,8)のうちの一方または有機半導体材料(2)と電気的に接触する。捕捉領域(9)は少なくとも電極間表面と対向する。  (もっと読む)

(もっと読む)

161 - 180 / 550

[ Back to top ]