Fターム[5F083GA28]の内容

Fターム[5F083GA28]に分類される特許

121 - 140 / 550

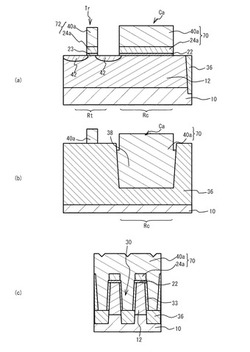

半導体装置およびその製造方法

【課題】トレンチ内に埋め込まれたシリコン層と複数のトレンチ間の半導体基板上に形成されたシリコン層とを同じイオン注入を行ない導電層とすること。

【解決手段】半導体基板10に複数のトレンチ30と、前記複数のトレンチ間の前記半導体基板上に第1キャパシタ絶縁膜22を介し第1シリコン層24と、を形成する工程と、前記複数のトレンチ内に埋め込み絶縁膜36を埋め込む工程と、前記埋め込み絶縁膜を前記複数のトレンチの側面に第2キャパシタ絶縁膜33が残存するように除去し、前記埋め込み酸化膜内に凹部を形成する工程と、前記凹部内の前記第2キャパシタ絶縁膜上と前記複数のトレンチ間の前記第1シリコン層上とに第2シリコン層40を直接形成する工程と、前記凹部内および前記第1キャパシタ絶縁膜上に形成された前記第2シリコン層内に不純物を同時にイオン注入する工程と、を含むことを特徴とする半導体装置の製造方法。

(もっと読む)

不揮発性半導体メモリ

【課題】新たなコンセプトに基づく不揮発性半導体メモリを提供する。

【解決手段】本開示の不揮発性半導体メモリは、半導体基板11上の半導体層12と、半導体層12を貫通する複数のコントロールゲートCG11〜CG17と、第1方向の2つの端部における半導体層12内にそれぞれ配置される2つの第1導電型拡散層14と、半導体層12上で第1方向に延びる複数のセレクトゲート線SG1〜SG5と、複数のセレクトゲート線SG1〜SG5上で第2方向に延びる複数のワード線WL1〜WL7とを備える。複数のセレクトゲート線SG1〜SG5の各々は、第1方向に並ぶ複数のコントロールゲートCG11〜CG17と複数のワード線WL1〜WL7との間に接続される複数のセレクトトランジスタに共有されるセレクトゲートとして機能する。半導体層12及び複数のコントロールゲートCG11〜CG17は、メモリセルアレイを構成する。

(もっと読む)

抵抗変化メモリ

【課題】高い抵抗値の抵抗素子を実現する。

【解決手段】本実施形態の抵抗変化メモリは、第1の配線レベルILV1に位置し、第1の方向に延びる制御線L1と、第2の配線レベルILV2に位置し、第2の方向に延びる制御線L2と、制御線L1と制御線L2との間に設けられるセルユニットCUとを含むメモリセルアレイを有し、複数の配線レベルに設けられる少なくとも2つの抵抗線RL3A,RL5と、抵抗線RL3A,RL5間に設けられ、セルユニットCUの構成部材又はコンタクトプラグZCの構成部材と同じ構成部材を含む抵抗体91と、を有し、抵抗素子領域17内に設けられる抵抗素子90を含んでいる。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧MISFETを含む半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】高耐圧MISFETQ4のゲート絶縁膜GOX4を、酸化シリコン膜と窒化シリコン膜という異なる種類の膜から形成する。具体的に、高耐圧MISFETQ4では、ゲート絶縁膜GOX4を、酸化シリコン膜PREOX1と、この酸化シリコン膜PREOX1上に形成された酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から形成している。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗変化素子を半導体装置に組み込む際の必要なフォトマスクを削減しても高密度化が可能な抵抗変化素子を搭載した半導体装置及びその製造方法を提供すること。

【解決手段】配線溝を有する層間絶縁膜14と、配線溝に埋め込まれた配線16aと、配線16aを含む層間絶縁膜14上に形成されるとともに、配線16aに通ずる下穴を有する層間絶縁膜18と、少なくとも下穴が配置された領域における配線16a上に形成されるとともに、抵抗が変化する抵抗変化膜19aと、下穴が配置された領域における抵抗変化膜19a上に形成されたバリアメタル20aと、下穴が配置された領域におけるバリアメタル20a上に形成されたプラグ21aと、を備え、抵抗変化素子5は、第1電極と第2電極との間に抵抗変化膜19aが介在した構成となっており、配線16aは、第1電極を兼ね、バリアメタル20aは、第2電極を兼ねる。

(もっと読む)

半導体装置の製造方法

【課題】ダミーシリコンピラーを用いてゲート電極を延長する場合の、シリコンピラーにおける反り変形の発生を抑制する。

【解決手段】半導体装置の製造方法は、第1及び第2のシリコンピラー3,4の側周面3a,4aに形成されたゲート絶縁膜9を覆うゲート電極材料を成膜する工程を備え、ゲート電極材料の成膜量は、ゲート絶縁膜9を介して側周面3aを覆う第1の部分と、ゲート絶縁膜9を介して側周面4aを覆う第2の部分とが接触しないよう制御され、第1及び第2の部分を覆うとともに第1の部分と第2の部分の間の領域を埋めるマスク絶縁膜を形成する工程と、マスク絶縁膜をマスクとして用いてゲート電極材料をエッチングすることにより、ゲート絶縁膜9を介してそれぞれ側周面3a,4aを覆うゲート電極101,102と、ゲート電極101,102とを電気的に接続する導体膜11とを形成する工程とをさら備える。

(もっと読む)

半導体装置の製造方法

【課題】SMAP法と比べて少ない積層数の膜構成で被加工部材に対し高アスペクト比の加工を行うことができる半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法によれば、被加工部材上にBを含む第1の膜、及びシリコン酸化膜からなる第2の膜を形成し、凹凸形状によりパターンが形成された原版を第2の膜に押し付けてパターンを第2の膜に転写し、パターンが転写された第2の膜をマスクとして、CH3FとO2を含み、酸素濃度を50〜90原子%とするエッチングガスを用いて第1の膜をエッチングしてパターンを第1の膜に転写し、パターンが転写された第1の膜をマスクとして被加工部材を加工してパターンを有する凹部を形成する。

(もっと読む)

半導体装置の製造方法

【課題】工程数が多く、煩雑になる問題を解決する半導体装置の製造方法を提供する。

【解決手段】半導体基板1に第1絶縁膜2を形成し、第1領域Aに第1導電型の第1ウエル層31を形成し、第1領域A以外の第1絶縁膜2上に第1半導体膜3を形成し、第1ウエル層31にトランジスタを形成し、第1半導体膜3及び第1領域Aの第1絶縁膜2の上に、トランジスタのビットコンタクトを兼ねる第2半導体膜7を形成する工程、第2半導体膜7上に、第2領域用B1のマスク8を積層してから、第1または第2導電型ドーパントを注入して第2ウエル層32を形成し、次いで、第2領域B1の少なくとも第2半導体膜7に、ドーパントを注入する工程、第2半導体膜7上に導電膜を積層してから、第1、第2半導体膜3,7及び導電膜を部分的にエッチングして、第1領域Aにトランジスタのビット配線層を、第2領域B1,B2に別の配線層を形成する工程、を具備する。

(もっと読む)

記憶装置、半導体装置

【課題】データの書き込み不良を抑えつつ、面積を小さく抑えることができる不揮発性の記憶装置、または当該不揮発性の記憶装置を用いた半導体装置の提供を目的の一とする。

【解決手段】不揮発性の記憶素子を有する第1の記憶部と、上記第1の記憶部へのデータの書き込みが正確に行われたかどうかを検証するベリファイ動作において、上記データを一時的に保存するための第2の記憶部(データバッファ)とを有する。そして、第2の記憶部が、記憶素子と、当該記憶素子における電荷の保持を制御するための、オフ電流またはリーク電流が極めて小さい絶縁ゲート電界効果型トランジスタとを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】第3電極への電圧印加のみで低抵抗状態と高抵抗状態のスイッチングが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、抵抗変化素子10を有している。抵抗変化素子10は、金属イオンが伝導可能なイオン伝導層14と、イオン伝導層14と接する第1電極12、第2電極16および第3電極17と、を備えている。第1電極12と第2電極16とは、電気化学反応に寄与しない不関電極であり、イオン伝導層14を挟んで対向するように配置され、第1電極12と第2電極16間との距離がイオン伝導層14の厚みと等しい。第3電極17は酸化可能な金属を含む電極である。第1電極12とイオン伝導層14とが接する面積をS1、第2電極16とイオン伝導層14とが接する面積をS2、第3電極17とイオン伝導層14が接する面積をS3としたとき、S1+S2<S3である。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】メモリセルアレイの耐ストレス性を向上できるようにする。

【解決手段】局所選択ゲート電極CSGが、部分的にメモリセルトランジスタMTを選択(例えばメモリセルトランジスタMT0〜MT7)することで、その他のメモリセルトランジスタMT(例えばメモリセルトランジスタMT8〜MT63)を非選択状態にすることができ、当該非選択状態とされたメモリセルトランジスタMTに高電圧を与える必要がない。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供することを課題の一とする。また、信頼性の高い半導体装置の作製方法を提供することを課題の一とする。また、消費電力が低い半導体装置を提供することを課題の一とする。また、消費電力が低い半導体装置の作製方法を提供することを課題の一とする。また、量産性の高い半導体装置を提供することを課題の一とする。また、量産性の高い半導体装置の作製方法を提供することを課題の一とする。

【解決手段】酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すれば良い。具体的には、酸化物半導体層にハロゲン元素を添加した後に加熱処理を施し、不純物を除去して使用すれば良い。ハロゲン元素としては、フッ素が好ましい。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】半導体と金属の反応速度を制御してメモリセル領域と周辺回路領域とのシリサイド反応の差による不具合を解消する不揮発性半導体記憶装置とその製造方法を提供する。

【解決手段】シリコン基板1の上面にゲート絶縁膜4、第1の導電膜5を形成し、これらをエッチングして素子分離絶縁膜2を埋め込み形成する。電極間絶縁膜6、ゲルマニウム膜7aを形成する。周辺回路領域のゲート電極PGの電極間絶縁膜6に開口6aを形成し、この上に多結晶シリコン膜9aを形成する。ゲート電極MG、PGおよび容量性素子Capの分離加工後に層間絶縁膜10を埋め込む。多結晶シリコン膜9aの上部を露出させ、金属膜を形成してシリサイド化をする。この時、メモリセル領域ではシリサイドが速く進行するが、ゲルマニウム膜7aに達するとジャーマナイド反応は遅くなり、その間に周辺回路領域のシリサイド反応を促進させることができる。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供することを課題の一とする。また、信頼性の高い半導体装置の作製方法を提供することを課題の一とする。また、消費電力が低い半導体装置を提供することを課題の一とする。また、消費電力が低い半導体装置の作製方法を提供することを課題の一とする。また、量産性の高い半導体装置を提供することを課題の一とする。また、量産性の高い半導体装置の作製方法を提供することを課題の一とする。

【解決手段】酸素欠損を生じることなく酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すればよい。具体的には、酸化物半導体層に酸素を添加した後に加熱処理を施し、不純物を除去して使用すればよい。特に酸素の添加方法としては、高エネルギーの酸素をイオン注入法またはイオンドーピング法などを用いて添加する方法が好ましい。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】多数の種類の材質の膜をエッチングによって加工する際に、膜の種類に応じた複数のハードマスクで加工を行いながら、工程数の増加を抑えることができる不揮発性記憶装置の製造方法を提供する。

【解決手段】第1の素子となる所定形状の素子形成部C1〜WL1間に絶縁膜60が形成された素子層上に、第2の素子となる素子材料層VR2〜BL1と、第2の素子の配線の一部となる配線材料層C2と、絶縁材料からなるマスク層と、を積層させ、所定形状に加工したマスク層を用いて配線材料層C2と素子材料層BL1〜VR2とをエッチングし、マスク層と配線材料層C2とをマスクとして、素子層の絶縁膜60をエッチングし、配線材料層C2をマスクとして、素子層の素子形成部C1〜WL1をエッチングして第1の素子を形成し、パターン間に埋め込んだ絶縁層を、配線材料層C2をストッパとして除去し、絶縁層上に第2の素子の配線となる配線層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】製造工程時間の増加を抑制して、微細なラインアンドスペースパターンを形成可能な半導体装置の製造方法を提供する。

【解決手段】被加工材であるシリコン酸化膜23上に、パターニングされた芯材31aとなるアンドープ多結晶シリコン膜31を形成する工程と、アンドープ多結晶シリコン膜31をスリミングして芯材31aとする工程と、芯材31aの側面及び上面、並びにシリコン酸化膜23の上面を被うように、シリコン酸化膜23と同じシリコン酸化膜にボロンが導入されたBドープ多結晶シリコン膜34を形成する工程と、芯材31a及びシリコン酸化膜23の上面のBドープ多結晶シリコン膜34を除去し、芯材31aの側面にBドープ多結晶シリコン膜34からなる側壁マスク膜34aを形成する工程と、芯材31aを除去する工程と、側壁マスク膜34aをマスクとしてシリコン酸化膜23をエッチング加工する工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体キャパシタ及び常誘電体キャパシタの両方を有する半導体装置を比較的少ない工程で製造できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板110にトランジスタ等を形成した後、メモリセル形成領域及びロジック回路形成領域にそれぞれ強誘電体膜127を電極126a,128aで挟んだ構造の強誘電体キャパシタを形成する。その後、強誘電体キャパシタを覆う層間絶縁膜131を形成し、更にその上にアルミナからなる保護膜132を形成する。そして、ロジック回路形成領域の保護膜132を除去する。これにより、半導体装置の製造工程が完了するまでの間にロジック回路形成領域の強誘電体膜127に水素及び水分が侵入して強誘電体特性が劣化し、強誘電体キャパシタが常誘電体キャパシタとなる。一方、メモリセル形成領域の強誘電体キャパシタは、保護膜132により強誘電体特性が保持される。

(もっと読む)

フラッシュメモリの製造方法

【課題】フラッシュメモリの製造工程において、エッチングによるSTI膜の膜減りを抑制することができる製造方法と、それを可能にするスプリットゲートタイプのMONOS型フラシュメモリ構造を提供する。

【解決手段】ワードゲートとコントロールゲートを含むスプリットゲートタイプのMONOS型フラシュメモリの製造方法であって、STIによって分離された半導体基板の不純物拡散層上に、酸化膜を挟んだワードゲートを形成する工程と、該STIとワードゲートが形成された半導体基板の表面全体に酸化膜、窒化膜、酸化膜の順に成膜されるONO層を形成する工程と、該ONO層の上にコントロールゲート用導電膜(10)を形成する工程と、該コントロールゲート用導電膜の表面全体にマスク用絶縁膜(26)を形成する工程と、を含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去特性の変動が小さく、特性の安定した不揮発性半導体記憶装置を実現する。

【解決手段】不揮発性半導体記憶装置50は、第1導電型の半導体基板1上にゲート電極6bを有し第2導電型のMISFET5と、半導体基板1上の第2導電型第1ウェル3に設けられ、第1容量電極6cを有する第1MISキャパシタ15と、半導体基板1上の第2導電型第2ウェル4に設けられ、第2容量電極6aを有する第2MISキャパシタ21とを備える。ゲート電極6b、第1容量電極6c、第2容量電極6aが電気的に接続されてフローティングゲート6を構成する。第2MISキャパシタ21にて、第2ウェル4と、第2ウェル4上の部分の第2容量電極6aとがキャパシタ領域を構成する。第2容量電極6aは、キャパシタ領域が複数の分割キャパシタ領域に分割され、各分割キャパシタ領域の面積が変動してもその総面積は略一定となる平面形状及び配置を有する。

(もっと読む)

半導体装置

【課題】デプレッション型トランジスタを用いて構成される記憶素子を有する半導体装置であっても、正確な情報の保持を可能にすること。

【解決手段】あらかじめ信号保持部への信号の入力を制御するトランジスタのゲート端子に負に帯電させ、且つ電源との接続を物理的に遮断することにより負電荷を保持させる。加えて、一方の端子が当該トランジスタのゲート端子に電気的に接続される容量素子を設け、当該容量素子を介して当該トランジスタのスイッチングを制御する。

(もっと読む)

121 - 140 / 550

[ Back to top ]