Fターム[5F083GA28]の内容

Fターム[5F083GA28]に分類される特許

41 - 60 / 550

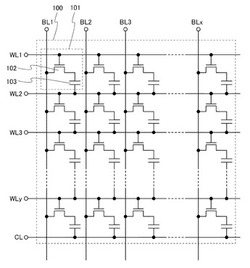

記憶装置、及び半導体装置

【課題】プロセスを複雑化させることなく、単位面積あたりの記憶容量を高めることができる記憶装置を提案する。

【解決手段】複数のメモリセルと、複数のワード線と、複数のビット線とを有し、複数のメモリセルは、スイッチング素子と、第1の電極及び第2の電極を有する容量素子と、をそれぞれ有し、複数のメモリセルの少なくとも1つにおいて、複数のワード線のうち一のワード線に与えられる電位に従って、スイッチング素子が複数のビット線のうち一のビット線と第1の電極の接続を制御し、なおかつ、第2の電極が複数のワード線のうち一のワード線とは異なる一のワード線に接続されている記憶装置。

(もっと読む)

ラッチ回路及び半導体装置

【課題】新規のラッチ回路を提供すること。

【解決手段】ラッチ回路は、酸化物半導体(OS)によってチャネル領域が形成されるトランジスタ10を有し、出力端子(Q端子)並びにトランジスタ10のソース及びドレインの一方に電気的に接続され、且つトランジスタ10がオフ状態となることによって浮遊状態となるノード11においてデータを保持する。なお、当該酸化物半導体は、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い。このような酸化物半導体によってトランジスタのチャネル領域が形成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。

(もっと読む)

記憶装置

【課題】データを保持する期間を確保しつつ、単位面積あたりの記憶容量を高めることが

できる記憶装置の提案を目的の一とする。

【解決手段】記憶素子と、記憶素子における電荷の蓄積、保持、放出を制御するための、

酸化物半導体を活性層に含むトランジスタと、記憶素子に接続された容量素子とを有する

記憶装置。上記容量素子が有する一対の電極の少なくとも一方は、遮光性を有している。

さらに、上記記憶装置は遮光性を有する導電膜或いは絶縁膜を有しており、上記活性層が

、遮光性を有する電極と、遮光性を有する導電膜或いは絶縁膜との間に位置する。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】演算部と、メモリと、演算部及びメモリを制御する制御部と、を有し、制御部は、揮発性の記憶回路と揮発性の記憶回路に保持されたデータを記憶するための第1の不揮発性の記憶回路との組を複数有し、メモリは、第2の不揮発性の記憶回路を複数有し、第1の不揮発性の記憶回路及び第2の不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子とを有する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、を有し、駆動回路は、

データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】メモリ・ロジック混載型の半導体装置の高性能化を可能にする技術を提供する。

【解決手段】ストッパ膜17は、ストッパ膜13及び層間絶縁膜14から成る絶縁層上に形成されている。コンタクトプラグ16,65,66のそれぞれは、その上面がストッパ膜17から露出するように、ソース・ドレイン領域9,59とそれぞれ電気的に接続されてストッパ膜13、層間絶縁膜14及びストッパ膜17に設けられている。絶縁層20は、ストッパ膜17及びコンタクトプラグ16,65,66の上に設けられている。キャパシタ82の下部電極は、メモリ形成領域において、コンタクトプラグ66の上面とストッパ膜17の上面とに接触するように絶縁層20内に設けられている。

(もっと読む)

記憶装置、及び半導体装置

【課題】高速動作を実現できる記憶装置、或いは、リフレッシュ動作の頻度が低減できる記憶装置を提供する。

【解決手段】セルアレイ101の内部において、メモリセル100に接続された配線に、駆動回路102から電位の供給が行われる。さらに、駆動回路102上にセルアレイ101が設けられており、セルアレイ101が有する複数の各メモリセル100は、スイッチング素子と、スイッチング素子により電荷の供給、保持、放出が制御される容量素子とを有する。そして、スイッチング素子として用いられるトランジスタは、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体を、チャネル形成領域に含んでいる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

半導体素子の製造方法

【課題】 製造コストの低減が可能な半導体素子の製造方法を提供する。

【解決手段】 第1再配線層400は、金属バンプ層320の一部分を露出するように形成される。第1再配線層400は、第1拡張パッド部410、第1延長部420及び第1連結部430を備える。第1拡張パッド部410は、金属パッド120と電気的に接続し、外部装置と接続する。第1延長部420は、金属バンプ層320上から第1拡張パッド部410上に延びるように形成される。第1連結部430は、スクライブレーン領域SRに形成され、複数の第1再配線層400を電気的に連結する。第1再配線層400は、銀、ニッケルまたは銅を含むペーストまたはインクを利用したプリンティング方法、または、ロールオフセットプリンティング方法によって形成される。これにより、金属パッドと再配線層との接触抵抗を小さくするとともに、製造コストを低減することができる。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、容量素子と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、信号線及びワード線に接続された第2のトランジスタと、ワード線、に接続された容量素子とを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方とが接続された、半導体装置。

(もっと読む)

半導体装置の作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを提供する。また、該トランジスタを用い、これまで実現が困難であった高性能の半導体装置を提供する。

【解決手段】トランジスタに、インジウム、スズ、亜鉛およびアルミニウムから選ばれた二種以上、好ましくは三種以上の元素を含む酸化物半導体膜を用いる。該酸化物半導体膜は、基板加熱しつつ成膜する。また、トランジスタの作製工程において、近接の絶縁膜または/およびイオン注入により酸化物半導体膜へ酸素が供給され、キャリア発生源となる酸素欠損を限りなく低減する。また、トランジスタの作製工程において、酸化物半導体膜を高純度化し、水素濃度を極めて低くする。

(もっと読む)

半導体装置およびその製造方法

【課題】FMONOSメモリセルとCMOSトランジスタが共存する半導体装置において、トランジスタの駆動電流を高めるとともにFMONOSメモリセルとしての機能を確保する半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、主表面上に形成された、チャネルを有するMONOS型メモリセルと、主表面上に形成されたnチャネル型トランジスタと、主表面上に形成されたpチャネル型トランジスタとを備える半導体装置である。上記MONOS型メモリセル、nチャネル型トランジスタおよびpチャネル型トランジスタの上面に接するように窒化膜CS1、CS2が形成されている。上記窒化膜CS1、CS2はMONOS型メモリセル、nチャネル型トランジスタおよびpチャネル型トランジスタのチャネルに応力を付加する。

(もっと読む)

多層接続構造及びその製造方法

【課題】3次元積層ICデバイスにおいて、相互接続領域のコンタクトレベルのスタックへの電気接続形成工程を簡略化する製造方法を提供する。

【解決手段】各コンタクトレベルは導電層と絶縁層とを有する。コンタクト開口を作り出すために、第1のコンタクトレベルを露出させるように上部層の一部が除去される。N個のマスクを用いて、最大2N個のコンタクトレベルまでコンタクト開口がエッチングされる。各マスクは、コンタクト開口のうちの実効的に半数をエッチングするために使用される。Nが3であるとき、第1のマスクにより1つのコンタクトレベルがエッチングされ、第2のマスクにより2つのコンタクトレベルがエッチングされ、第3のマスクにより4つのコンタクトレベルがエッチングされる。コンタクト開口の側壁に誘電体層が形成され得る。コンタクト開口内に導電体が形成され、前記誘電体層が該導電体を前記側壁から電気的に絶縁する。

(もっと読む)

半導体記憶装置

【課題】不揮発性の記憶装置を有するCAMとする際に、メモリセルの低消費電力化を図ることのできる半導体記憶装置を提供することを課題の一とする。また、データの書き込みを繰り返し行う際の劣化をなくすことができる半導体記憶装置を提供することを課題の一とする。また、メモリセルの高密度化が可能な不揮発性の記憶装置を提供する。

【解決手段】酸化物半導体を半導体層に有する第1のトランジスタ及び当該第1のトランジスタをオフ状態とすることで書き込んだデータに対応する電位を保持できる容量素子を有するメモリ回路と、書き込んだ電位を参照するための参照回路を有し、参照回路を構成する第2のトランジスタの導通状態を検出することで、整合するデータのアドレスを取得し、高速な検索機能を可能にした半導体記憶装置である。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは、ビット線をキャパシタとセルトランジスタの間に形成するため、構造が複雑であったり、回路の特性を犠牲にしたりする必要があり、集積化の面で大きな障害となっている。

【解決手段】キャパシタの一方の電極をビット線に接続し、他方の電極をセルトランジスタのドレインに接続する。また、セルトランジスタのソースは、ソース線に接続される。この結果、例えば、スタック型キャパシタを採用する場合には、キャパシタの電極の一方をビット線の一部とすることができる。ソース線は、半導体基板上に形成された不純物領域や、ワード線に平行な配線を用いることができるので、構造が単純となる。

(もっと読む)

半導体素子及びその製造方法

【課題】干渉現象を減らしてゲートラインの抵抗を減らすことができる半導体素子の製造方法を提供する。

【解決手段】最上部層が金属シリサイド層からなり、第1間隔で半導体基板上に配列される第1ゲートラインと、最上部層が金属シリサイド層からなり、前記第1間隔より広い第2間隔で前記半導体基板上に配列される第2ゲートラインと、前記第1ゲートラインの間の前記半導体基板上に形成されてエアギャップを含む第1絶縁膜と、前記第2ゲートラインの対向する側壁上に形成された第2絶縁膜と、前記第2絶縁膜の側壁に形成されたエッチング停止膜と、前記第1ゲートラインの間の空間と前記第2ゲートラインとの間の空間が満たされるように全体構造上に形成された第3絶縁膜と、前記第3絶縁膜の上部に形成されたキャッピング膜と、前記キャッピング膜及び前記第3絶縁膜を貫通して前記第2ゲートラインの間の前記半導体基板に形成された接合領域と繋がれるコンタクトプラグと、を含む。

(もっと読む)

半導体記憶装置

【課題】相変化メモリの構造の簡素化と低コスト化を実現する。

【解決手段】相変化材料からなる記録層18とn+型ポリシリコン膜15との間に、相変化材料を構成する元素の少なくとも一種とシリコンとを含有する中間層20を配置し、記録層18とn+型ポリシリコン膜15との接触抵抗を低減することにより、相変化メモリの構造の簡素化と低コスト化を実現する。例えば相変化材料がGe、SbおよびTeを含む場合、中間層20は、Si−Sb、Si−Te、Si−Geの少なくとも一種を含む。

(もっと読む)

半導体装置

【課題】不揮発性であって、作製が簡単であり、追記が可能な記憶回路を有する半導体装置の提供を課題とする。

【解決手段】本発明の半導体装置は、複数のトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記複数のトランジスタのうちの1つの上に設けられた記憶素子及びアンテナとして機能する導電層とを有し、前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、アンテナとして機能する前記導電層と前記複数のトランジスタのソース配線又はドレイン配線として機能する導電層とは、同じ層上に設けられていることを特徴とする。

(もっと読む)

不揮発性半導体記憶装置とその製造方法

【課題】メモリセルが3次元的に積層された不揮発性半導体記憶装置を工程数の増大を抑制しながら製造可能な不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】半導体基板101上にスペーサ膜104とチャネル半導体膜103とを交互に複数層積層させた積層構造を形成し、積層構造に第1の方向に延在するトレンチを形成する。ついで、トレンチからチャネル半導体膜103を第2の方向にリセスして空隙を形成し、空隙内のチャネル半導体膜103上にトンネル誘電体膜108を形成し、フローティングゲート電極膜109を埋め込む。その後、第1の方向に隣接するメモリセル間でフローティングゲート電極膜109が分離され、チャネル半導体膜103が分離されないように、積層構造を第1の方向に所定の間隔で分割する。また、第2の方向に隣接するメモリセル間でチャネル半導体膜103が分離されるように、積層構造を第2の方向に所定の間隔で分割する。

(もっと読む)

半導体装置及びその製造方法

【課題】従来のReRAMを有する半導体装置では、メモリ素子特性にばらつきが生ずるおそれがあった。

【解決手段】基板11を覆う第1の絶縁膜23を形成する工程と、第1の絶縁膜23を貫通する導電プラグ24を形成する工程と、導電プラグ24の上部を一部除去して、導電プラグ24の上面を底面として有し、かつ、一部除去した導電プラグ24に覆われていた部分の第1の絶縁膜23を側壁として有する孔部を形成する工程と、孔部の側壁を覆い、孔部の底面の一部を露出させる側壁絶縁膜25を形成する工程と、孔部の側壁絶縁膜25および底面を覆う可変抵抗膜26を形成する工程と、可変抵抗膜26を覆う導電膜27を形成する工程と、を有する。

(もっと読む)

41 - 60 / 550

[ Back to top ]