Fターム[5F083GA28]の内容

Fターム[5F083GA28]に分類される特許

81 - 100 / 550

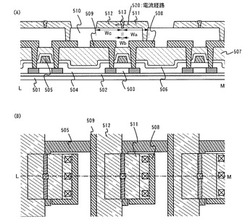

半導体装置

【課題】上下電極間に有機化合物を設けて記憶素子を形成するが、有機化合物を含む層の

上に電極を形成した場合、電極の形成時の温度によっては有機化合物を含む層への影響が

あるため温度に制限がある。この温度の制限のため形成方法が限定され、希望通りの電極

を形成することができず、素子の微細化を阻害している問題があった。

【解決手段】絶縁表面を有する基板上に記憶素子及びスイッチング素子が配置された半導

体装置とし、前記素子は、同一平面に配置された第1の電極と第2の電極と有機化合物を

含む層とを有し、前記有機化合物を含む層は前記第1の電極と前記第2の電極との間に形

成され、電流は前記第1の電極から前記第2の電極へと流れ、前記第1の電極は、前記ス

イッチング素子と電気的に接続されている半導体装置である。

(もっと読む)

半導体装置

【課題】非接触でデータの送受信が可能な半導体装置は、鉄道乗車カードや電子マネーカ

ードなどの一部では普及しているが、さらなる普及のためには、安価な半導体装置を提供

することが急務の課題であった。上記の実情を鑑み、単純な構造のメモリを含む半導体装

置を提供して、安価な半導体装置及びその作製方法の提供を課題とする。

【解決手段】有機化合物を含む層を有するメモリとし、メモリ素子部に設けるTFTのソ

ース電極またはドレイン電極をエッチングにより加工し、メモリのビット線を構成する導

電層とする。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体記憶装置の製造方法

【課題】製造が容易なNAND型半導体記憶装置の製造方法を提供する。

【解決手段】製造方法は、基板101上に第1絶縁膜105及び第2絶縁膜106を交互に積層して積層体110を形成する工程と、第1絶縁膜105及び第2絶縁膜106の積層方向に延び、積層体110を貫通する貫通孔114を形成する工程と、貫通孔114の内面上に、MONOS116を構成するブロック絶縁膜、チャージトラップ膜及びトンネル誘電体膜の少なくとも一部を形成する工程と、トンネル誘電体膜上にチャネル半導体117を形成する工程と、積層体110にトレンチ121を形成する工程と、トレンチ121を介してエッチングを施すことにより、第2絶縁膜106を除去する工程と、第2絶縁膜106を除去した後の空間内に導電材料を埋め込む工程と、を備える。

(もっと読む)

埋め込みドープ層を有する完全空乏型SOIデバイス

【課題】完全空乏型SOIデバイスの製造に適したセミコンダクタオンインシュレータ(SeOI)ウェーハおよびそれを用いたデバイスを提供すること。

【解決手段】本発明は、第1の基板の表面領域にドープ層、ドープ層上に埋め込み酸化物層、埋め込み酸化物層上に半導体層を形成してSeOIウェーハを得る。SeOIウェーハの第2の領域の埋め込み酸化物層および半導体層を維持しながらSeOIウェーハの第1の領域から埋め込み酸化物層および半導体層を除去し、第2の領域に上部トランジスタを形成する。第1の領域にリセスチャネルアレイトランジスタを形成し、第2の領域にpチャネルトランジスタおよび/またはnチャネルトランジスタを形成する。ドープ層内またはこの近傍にバックゲートを形成し、第1の領域にリセスチャネルアレイトランジスタを形成し、ドープ層内またはその近傍にソース領域およびドレイン領域を形成する。

(もっと読む)

半導体記憶装置

【課題】CMOSプロセスで、ダイナミック型半導体記憶装置を形成し、ロジックとの混載に適したダイナミック型半導体記憶装置を実現する。

【解決手段】メモリセル(MC)のワード線(WL)を形成する導電線(3)とメモリセルセルプレート電極(CP)を形成する導電線(5)とを、異なる配線層に形成する。対をなすビット線に並行してメモリセルを接続し、2つのメモリセルで1ビットのデータを記憶する。

(もっと読む)

浅いトレンチ分離および基板貫通ビアの集積回路設計への統合

【課題】浅いトレンチ分離および基板貫通ビアの集積回路設計への統合を提供すること。

【解決手段】ICを製造する方法は、第1の側、および第2の対向する側を有する基板を用意すること、基板の第1の側にSTI開口を形成すること、および基板の第1の側に部分的TSV開口を形成すること、および部分的TSV開口を延長することを含む。延長された部分的TSV開口は、STI開口より基板内への深さが深い。方法はまた、STI開口を第1の固体材料で充填すること、および延長された部分的TSV開口を第2の固体材料で充填することを含む。STI開口、部分的TSV開口、または延長された部分的TSV開口のいずれも、基板の第2の側の外面を貫通しない。少なくとも、STI開口および部分的TSV開口は同時に形成され、またはSTI開口および延長された部分的TSV開口は同時に充填される。

(もっと読む)

半導体記憶装置

【課題】チャネル領域にソース領域及びドレイン領域を形成せずに、信頼性が高い動作が可能な半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、第1の方向に延びる同一導電形のチャネル領域と、チャネル領域上に設けられた第1の絶縁膜と、第1の絶縁膜上に設けられた複数の浮遊ゲートと、浮遊ゲートの上に設けられた第2の絶縁膜と、第2の絶縁膜の上に設けられた制御ゲートとを備えている。複数の浮遊ゲートは第1の方向及びこれに交差する第2の方向に分断されている。制御ゲートは第1の方向に対して交差する第2の方向に延びている。浮遊ゲートのフリンジ電界によって、第1の方向で隣り合う浮遊ゲート間の下のチャネル領域の表面に反転層が形成される。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】データの取り扱いが容易な半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、基板と、前記基板上に設けられ、それぞれ複数の絶縁膜及び電極膜が交互に積層され、前記基板の上面に対して平行な第1の方向側の端部において、それぞれが各前記電極膜の上面によって構成された複数のテラスが前記第1の方向のみに沿って階段状に形成された積層体と、前記テラスに接続され、前記電極膜を、前記基板の上面に平行な方向であって前記第1の方向に対して直交する第2の方向に引き出し、前記基板に接続する導電部材と、前記積層体の中央部に設けられ、前記絶縁膜及び前記電極膜の積層方向に延びる半導体ピラーと、前記電極膜と前記半導体ピラーとの間に設けられた電荷蓄積層と、を備える。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】データの保持期間を長くする半導体装置又は半導体記憶装置を提供する。

【解決手段】一対の不純物領域を有する第1の半導体層152aと、第1の半導体層と同じ材料であり、第1の半導体層と離間する第2の半導体層152bと、第1、第2の半導体層の上に設けられた第1の絶縁層153と、第1の絶縁層153を介して第1の半導体層に重畳する第1の導電層154と、第1の絶縁層153を介して第1の導電層に重畳し、第1の半導体層と異なる材料である第3の半導体層156と、第1の導電層及び第3の半導体層に電気的に接続される第2の導電層157bと、第3の半導体層156に電気的に接続され、第2の導電層と同じ材料である第3の導電層157aと、第3の半導体層、第2の導電層、及び第3の導電層の上に設けられた第2の絶縁層158と、第2の絶縁層を介して第3の半導体層に重畳する第4の導電層159と、を含む。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】下部電極、上部電極およびそれらの間の絶縁膜により構成される容量素子の下部電極および上部電極間の耐圧を向上させる。

【解決手段】上部電極TEならびに上部電極TEのそれぞれの側壁の側壁酸化膜9およびサイドウォール10と下部電極BEとの間にONO膜IFを連続的に形成し、また、上部電極TEの側壁に、側壁酸化膜9を介して真性半導体膜からなるサイドウォール10を形成することにより、下部電極BEおよび上部電極TE間にリーク電流が発生することを防ぐ。

(もっと読む)

半導体メモリ及びその製造方法

【課題】半導体メモリの構造の簡略化と製造プロセスの簡易化とを実現する。

【解決手段】半導体基板と、半導体基板内に形成され、かつ互いに直交する第1及び第2の方向にそれぞれ延在する第1及び第2のソース領域104、109とを有する半導体メモリ。第1及び第2のソース領域はそれぞれ拡散領域であって、交差する部分で電気的に接続されている。また半導体メモリは、第2のソース領域109と同一方向に延在するビットライン108と、第2のソース領域109上に形成されたソースラインとを有し、ソースラインと第2のソース領域109とのコンタクトと、ビットライン108と半導体基板内に形成されたドレイン領域とのコンタクトとは直線状に配置されている。

(もっと読む)

埋め込み配線を備える基板、その製造方法、これを利用する半導体装置およびその製造方法

【課題】 低抵抗の埋め込み配線を備える基板の製造方法を提供する。

【解決手段】 始めに半導体用基板100の第1面S1上に導電層120を形成する。次に、導電層120をパターニングして第1方向に延長する線形の導電層パターン122を形成する。導電層120をパターニングするとき露出する半導体用基板100をエッチングして導電層パターン120の下部に第1方向に延長する線形の半導体パターン104を形成する。次に導電層パターン120および半導体パターン104上に絶縁層150を形成する。半導体用基板100の第1面S1側の絶縁層150が支持基板160と当接するように支持基板160上に配置する。次に半導体用基板100のイオン注入層102側の絶縁層150が露出するように半導体用基板100を除去する。これにより、導電層パターン120は、半導体パターン104の埋め込み配線として利用することができる。

(もっと読む)

半導体装置の製造方法

【課題】 半導体記憶装置に係り、特に、高集積化されたDRAMを、少ない工程数で、且つ微細なセル面積で実現できる半導体記憶装置及びその製造方法を提供する。

【解決手段】 半導体基板10に形成されたメモリセルトランジスタと、メモリセルトランジスタのゲート電極20の上面及び側面を覆う絶縁膜42と、ソース拡散層24上に開口したスルーホール40と、ドレイン拡散層26上に開口したスルーホール38とが形成された層間絶縁膜36と、スルーホール40内壁及び底部に形成され、ソース拡散24層に接続されたキャパシタ蓄積電極46と、キャパシタ蓄積電極46を覆うキャパシタ誘電体膜48と、キャパシタ誘電体膜48を覆うキャパシタ対向電極54とを有するキャパシタと、スルーホール38の内壁及び底部に形成され、ドレイン拡散層と接続されたコンタクト用導電膜44とにより構成する。

(もっと読む)

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタのSCEに対する免疫性を向上させると同時に、分岐点での重なりを増加させる方法及び構造の提供。

【解決手段】基板102は第1活性領域104と第2活性領域106とを有し、浅溝分離(STI)領域108によって分離される。バッファ層112は応力緩和層として機能しハードマスク層114が形成される。基板102の表面に分離領域108を部分的に網羅するように凹部118を設ける。ゲート誘電体120が凹部118に形成された後第一ドーパントインプラント122により、ドープ済みチャンネル領域124が形成される。インプラントはハードマスク114を貫通しないので、凹部118の下に形成されたドープ済みチャンネル領域124中のドーパント濃度は最も高くなる。ドープ済みチャンネル領域124はトランジスタのオン・オフを切り替える閾値電圧を変調する。

(もっと読む)

ナンドフラッシュメモリ素子及びその製造方法

【課題】セレクトラインの抵抗を改善すると同時にナンドフラッシュメモリ素子の製造工程を単純化することができるナンドフラッシュメモリ素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された選択トランジスタ及びメモリセル用第1導電膜パターンと、前記第1導電膜パターン上に形成された誘電体膜と、前記メモリセル用第1導電膜パターン上の前記誘電体膜上に形成された第2導電膜パターンと、前記選択トランジスタ用第1導電膜パターンと繋がれて前記第2導電膜パターンより抵抗の低い物質で形成されたセレクトラインと、を含む。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】 半導体装置の製造工程を簡略化させ、金属元素含有膜の酸化を抑制させる。

【解決手段】 金属元素含有膜及び金属元素含有膜上に形成された絶縁膜を備える基板を処理室内に搬入し、処理室内に設けられた基板支持部により支持する工程と、励起状態の水素と励起状態の窒素のいずれか又は両方と、励起状態の酸素と、を含む反応ガスを処理室内で基板上に供給して基板を処理する工程と、基板を処理室内から搬出する工程と、を有する。

(もっと読む)

半導体装置

【課題】半導体装置の省スペース化を実現する。

【解決手段】半導体基板5に、センスアンプが備えられた周辺回路領域Sとメモリセル領域Mとが区画形成され、メモリセル領域Mにおいて、半導体基板5の一面に形成されたトレンチ溝内に、ゲート絶縁膜を介しゲート電極を含む埋込ワード線9とその上に位置する埋込絶縁膜とが埋め込まれ、前記トレンチ溝に隣接する半導体基板5一面の表面領域に不純物拡散層が形成され、前記不純物拡散層が形成された領域上にはビット配線15が形成されており、ビット配線15が周辺回路領域Sまで延長され、周辺回路領域Sにおいてビット配線15が前記センスアンプを構成するMOSトランジスタのゲート電極Gとされていることを特徴とする半導体装置を採用する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを用いて、高速動作が可能で、信頼性も高い半導体装置を歩留まりよく作製する。

【解決手段】絶縁膜上にマスクを形成し、該マスクを微細化する。微細化されたマスクを用いて凸部を有する絶縁層を形成し、これを用いて、微細なチャネル長(L)を有するトランジスタを形成する。また、トランジスタを作製する際に、微細化された凸部の上面と重なるゲート絶縁膜の表面に平坦化処理を行う。これにより、トランジスタの高速化を達成しつつ、信頼性を向上させることが可能となる。また、絶縁膜を凸部を有する形状とすることで、自己整合的にソース電極及びドレイン電極を形成することができ、製造工程の簡略化、また生産性を向上させることが可能となる。

(もっと読む)

81 - 100 / 550

[ Back to top ]