Fターム[5F083GA28]の内容

Fターム[5F083GA28]に分類される特許

201 - 220 / 550

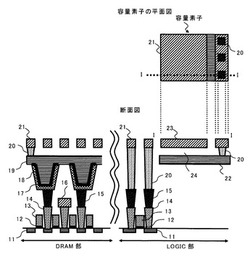

半導体装置

【課題】回路を形成する領域を確保しつつ、十分な耐圧、容量を備えた容量素子を備える半導体装置を提供する。

【解決手段】半導体装置は、DRAMセルのキャパシタ上部電極19と、上部電極19の下方に形成されたキャパシタ下部電極17とを含む情報記憶部と、情報記憶部へのアクセスを制御するアクセストランジスタとを有するメモリセルと、アクセストランジスタに接続され、情報記憶部にデータの書き込み又は読み出しを行うビット線16と、アクセストランジスタのゲート電極に接続され、アクセストランジスタを制御するワード線と、キャパシタ上部電極19の上方に形成された第1金属配線21と同一層からなる上部電極23と、キャパシタ上部電極19と同一層の下部電極22とを有し、メモリセルが形成された領域外に形成された容量素子とを備える。

(もっと読む)

ナノ線メモリ

【課題】単純な構造のナノ点を有するメモリを利用してマルチレベルを保存することができるメモリ素子を提供する。

【解決手段】ソース210及びソース210と対応するドレイン220と、ソース210とドレイン220との間を連結するように形成されているナノチャンネル230とを含み、ナノチャンネル230は、ソース210及びドレイン220の電圧によってソース210とドレイン220との間を電気的に連結するナノ線と、ナノ線上に吸着されて形成され、電荷を補集する複数のポテンシャルを有するナノ点とを含む。

(もっと読む)

半導体装置の製造方法

【課題】多段キャパシタの形成およびキャパシタシリンダを支えるサポート絶縁膜の周辺回路領域における除去を工程数を増大させることなく達成する、キャパシタシリンダが多段に積層されたキャパシタを有する半導体装置の製造方法を提供する。

【解決手段】容量絶縁膜および上部電極の形成工程をそれぞれ1回の成膜工程で行うと共に、周辺回路領域のスルーホールエッチングや水素アニールの妨害となるサポート絶縁膜について、周辺回路領域の残すべき層間絶縁膜の最上層のみ、容量絶縁膜および上部電極形成時に一括して除去し、それより下層の周辺回路領域のサポート絶縁膜がある場合は、メモリセル領域のコア絶縁膜除去のための開口形成と同時に除去する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】1つのトランジスタと1つの抵抗変化素子とを用いた1T1R型のメモリセルであって、抵抗変化素子の構造を簡素化することにより、微細化できるメモリセルを有する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】トランジスタ101が形成された基板102と、基板上にトランジスタを覆って形成された第1の層間絶縁層103と、第1の層間絶縁層に形成され、トランジスタのドレイン電極101aまたはソース電極101bと電気的に接続された第1のコンタクトプラグ104または第2のコンタクトプラグ105と、第1のコンタクトプラグの少なくとも一部を被覆して形成された抵抗変化層106と、抵抗変化層上に形成された第1の配線107と、第2のコンタクトプラグの少なくとも一部を被覆して形成された第2の配線108とを備え、抵抗変化層の端面と第1の配線の端面とは同一面内にある不揮発性半導体記憶装置100。

(もっと読む)

半導体装置の製造方法

【課題】被保護素子部、保護素子部及び周辺トランジスタ部を備える半導体装置において、周辺トランジスタ部のゲート絶縁膜と該ゲート絶縁膜よりも膜厚が薄い保護素子部の界面絶縁膜とを同一の工程において形成できるようにする。

【解決手段】半導体基板1の上に、被保護素子用ゲート絶縁膜2を形成し、保護素子部に形成された被保護素子用ゲート絶縁膜2の一部を除去して、開口部14を形成し、半導体基板1の上部に開口部14を通して不純物を注入して、保護素子部にダイオードを形成し、ダイオードの上部に酸化抑制材を注入して、酸化抑制層9を形成し、半導体基板1における周辺トランジスタ部の少なくとも一部とを露出し、露出した半導体基板1の上にゲート絶縁膜11を形成すると共に、酸化抑制層9の上に界面絶縁膜12を形成し、被保護素子用ゲート絶縁膜2、ゲート絶縁膜11及び界面絶縁膜12の上にゲート電極13を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 抵抗素子の抵抗値の選択範囲を拡大し、且つ抵抗層形成後にシリサイドブロックを形成せずに該抵抗層のシリサイド化を防止することを可能にする。

【解決手段】 半導体領域11上に絶縁膜15を形成し、絶縁膜15を介して半導体領域11に不純物のイオン注入12を行う。これにより、絶縁膜15の下に抵抗層13が形成されるとともに、抵抗層13に隣接して電極領域14が形成される。その後、電極領域14の表面にシリサイド膜17を形成する。このとき、絶縁膜15は、抵抗層13がシリサイド化されることを防止するシリサイドブロックとして機能する。イオン注入12として、同一半導体基板上に形成されるMOSトランジスタのソース/ドレイン領域への不純物注入工程を利用し得る。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】動作電圧が低い半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置の抵抗可変素子を作製する際に、タングステンからなる導電膜31上にチタンシリコン窒化物からなる非晶質膜32を堆積させ、その上にチタン窒化物からなる多結晶導電膜33を堆積させることにより、下部電極25を形成する。次に、ニッケル酸化物からなる抵抗可変膜26を堆積させ、その後加熱処理を行い、多結晶導電膜33の結晶を成長させると共に、多結晶導電膜33に含まれるチタンと抵抗可変膜26に含まれる酸素とを反応させる。これにより、多結晶導電膜33の結晶粒が不均一に成長して突起34が形成されると共に、酸化膜35が形成されることにより、抵抗可変膜26の下層部分26aに酸素欠損が生成される。

(もっと読む)

半導体集積回路

【課題】集積回路内では、それぞれの回路の事情により最適なゲート長とゲート酸化膜厚としきい値電圧があることになる。これらの回路を同一基板上に集積する半導体集積回路では、それぞれの回路の最適な値にするために製造工程が複雑化し、結果として歩留まりの低下、製造日数の増加に伴い製造コストの上昇をもたらす。

【解決手段】論理回路には高低2種類のしきい値のトランジスタを用い、メモリセルには高しきい値電圧と同じしきい値電圧のトランジスタにより構成し、入出力回路は上記の高しきい値電圧と同じチャネルの不純物濃度でゲート酸化膜厚を厚くしたトランジスタを用いて構成する。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】コンタクト抵抗の増大を防止できるようにする、記憶部と論理部とを混載する不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】半導体基板1の上にビット線コンタクト領域20と、ビット線コンタクト領域を含め、行方向に延伸する複数の第1のゲート絶縁膜11とを形成し、ビット線コンタクト領域20を挟んでビット線拡散層2を形成し、ビット線拡散層2及び第1のゲート絶縁膜11の上に導電膜4を形成し、導電膜4からビット線拡散層2と交差するコントロールゲート電極4aを形成し、少なくともビット線コンタクト領域20の第1のゲート絶縁膜11を除くと共に、ビット線コンタクト領域20に、その両側のビット線拡散層2同士を接続するように接続拡散層を形成する。コントロールゲート電極4aを形成する時に、ビット線コンタクト領域20の上及びその両側のビット線拡散層2の上にまたがるように導電膜4を残存させる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】電荷蓄積膜に電界が均一に印加される不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】シリコン基板11上にトンネル絶縁膜14、電荷蓄積膜15、ブロック絶縁膜16を形成する。次に、これらの膜及びシリコン基板11の上層部分にメモリストリング方向に延びる複数本のSTI12を形成することにより、ブロック絶縁膜16、電荷蓄積膜15及びトンネル絶縁膜14を分断すると共に、シリコン基板11の上層部分をメモリストリング方向に延びる複数本の半導体部分13に区画する。次に、半導体部分13の直上域及びSTI12の直上域の双方に配置されるように、ブロック絶縁膜19を形成し、その上に制御ゲート電極WL及び選択ゲート電極SGを形成する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】選択トランジスタと抵抗変化素子との間の配線抵抗を低減して、抵抗変化素子の消去動作を安定して行うことを可能にする半導体記憶装置とその製造方法を提供する。

【解決手段】半導体基板11に形成された第1MOSトランジスタ2と、半導体基板11に形成されていて第1MOSトランジスタ2の二つの第1拡散層16A,17Aの一つの第1拡散層17Aを共通の拡散層とする第2MOSトランジスタ3と、第1MOSトランジスタ2の第1ゲート電極13Aと第2MOSトランジスタ3の第2ゲート電極13Bとの間に第1,第2サイドウォール絶縁膜15A,15Bを介して形成されていて共通の拡散層18に接続された抵抗変化素子4を有する。抵抗変化層22は、金属酸化物膜からなる記憶層24と、記憶層24に金属イオンを供給もしくは記憶層24に供給した金属イオンを受給するイオン源層25からなる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】フォトリソグラフィによるレジストを形成する工程を削減してコストを低減することが可能な半導体記憶装置及びその製造方法を提供すること。

【解決手段】第2不純物領域2bは、列方向に隣り合う第2不純物領域2b同士が繋がるように構成され、セレクトゲート電極4は、第2不純物領域2bを囲むようにリング状に構成されるとともに、ワード線WLと電気的に接続され、第1コントロールゲート電極6aは、セレクトゲート電極4の外周側にてリング状に構成され、第2コントロールゲート電極6bは、セレクトゲート電極4の内周側にてリング状に構成され、メモリセル上にて行ごとに対応する一対の第1、第2ビット線BLが配され、第1ビット線BLは、行方向に隣り合う第1不純物領域2aの一方と電気的に接続され、第2ビット線BLは、行方向に隣り合う第1不純物領域2aの他方と電気的に接続されている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】消費電力の増大に対して有利な半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルをそれぞれ備え、半導体基板35上に複数積層される三次元構造の複数のメモリセルアレイ10と、半導体基板35中に設けられる第1導電型の第1ウェル43と、第1ウェル43中において第1ウェル43の底面よりも浅い位置に底面を有し、半導体基板35中に埋め込み配置される素子分離絶縁膜STIと、第1ウェル43中において第1ウェル43の底面よりも浅い位置に底面を有し(DP<DN)、素子分離絶縁膜STIの少なくとも一部の底面に沿って設けられ、第2導電型の不純物によって形成される第2ウェル44と、第1ウェルと電気的に接続されるコンタクト配線CLとを具備する。

(もっと読む)

薄膜トランジスタを利用して不揮発性メモリとする方法およびその装置

【課題】薄膜トランジスタ(TFT)のベースを利用して電荷を保存し、不揮発性メモリとする方法を提供する。

【解決手段】薄膜トランジスタ10を利用し、そのうち薄膜トランジスタ10は中間がベース21、両端がそれぞれドレイン電極22、ソース電極23である半導体層20を備え、絶縁表面31を備えた基板30上に設置され、ゲート電極絶縁層41が前記半導体層20上に設置され、ゲート電極40がゲート電極絶縁層41上に設置され、電子がゲート電極40の電場作用下で、熱電子界放射により電子正孔対を形成し、電子正孔対がゲート電極40の垂直電場により分離され、複数のキャリア(nチャネルでいうと正孔)が薄膜トランジスタ10のベース21に注入され、薄膜トランジスタ10の閾値電圧の変化を引き起こし、書き込み動作が完了する。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】製造工程による抵抗変化層の特性劣化を改善する抵抗変化層を用いた不揮発性記憶装置を提供する。

【解決手段】基板11上に形成された下層配線15と、下層配線15上の少なくとも一部に形成された抵抗変化層16と、下層配線15と抵抗変化層16とを含む基板11上に形成された層間絶縁層17と、層間絶縁層17を貫通して抵抗変化層16に接続するように形成されたコンタクトホール26と、抵抗変化層16に接続し、コンタクトホール26内に形成された埋め込み電極19と、層間絶縁層17上に埋め込み電極19と接続し、下層配線15に対して交差する上層配線20とを備え、抵抗変化層16は少なくとも酸素不足型の遷移金属酸化物を含み、かつコンタクトホール26が接続する領域の抵抗変化層16の表層部分がコンタクトホール26と接続する領域以外の抵抗変化層16の表層部分に比べて凹んだ形状になっている。

(もっと読む)

半導体装置の製造方法

【課題】本発明は多層配線構造を有する半導体装置の製造方法に関し、高い集積度が要求される場合に優れた歩留まりと高い信頼性とを確保することを目的とする。

【解決手段】トランジスタのソースドレイン領域の上層にシリコン酸化膜7を形成する。一端面がソースドレイン領域6に導通し、他端面がシリコン酸化膜7の表面に露出するように、シリコン酸化膜7の内部に導電性のパッド10を設ける。シリコン酸化膜7およびパッド10の上層にシリコン酸化膜11を形成する。一端面がパッド10に接触し、他端面が配線層14と導通するようにシリコン酸化膜11の内部にプラグとして機能する導電層を設ける。シリコン酸化膜7の表面と、パッド10の他端面は平滑な同一平面を形成する。プラグとして機能する導電層は、パッド10に比して小さく、かつ、パッド10の中央部近傍に接触するように形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】製造工程の増加を抑えて、通常のコンタクトとシェアードコンタクトとをそれぞれ良好なコンタクト特性を有するようにする。

【解決手段】半導体装置100は、第1の不純物拡散領域106aに接続するとともに、第1のゲート電極112aとは接続しないように形成された第1のコンタクト124と、第2のゲート電極112bおよび第2の不純物拡散領域106bに共通して接続するように形成された第2のコンタクト126とを含む。第1のコンタクト124および第2のコンタクト126は、それぞれ、層間絶縁膜122の表面から基板101に向かう途中の位置でテーパー角度が小さくなるように変化する形状を有し、第2のコンタクト126においてテーパー角度が変化する位置が、第1のコンタクト124においてテーパー角度が変化する位置よりも基板101に近い。

(もっと読む)

垂直ビット線および片側ワード線アーキテクチャを有する再プログラミング可能な不揮発性メモリ素子の3次元アレイ

自分に印加された電圧差に応答して電気コンダクタンスのレベルを可逆的に変化させるメモリ素子に特に適する3次元アレイを開示する。半導体基板の上の別々の距離のところに位置する複数のプレーンにメモリ素子が形成される。全プレーンのメモリ素子が接続されるビット線の2次元アレイは、基板からその複数のプレーンを通って垂直に向けられる。片側ワード線アーキテクチャは、2行のメモリ素子の間で1つのワード線を共有する代わりにメモリ素子の各行のために唯1つのワード線を設け、これによりアレイ中のメモリ素子をワード線を横断させてつなぐことを回避する。メモリ素子の行は同様にローカルビット線の対応する行によりアクセスされるけれども、ローカルビット線の隣接する行間での結合の拡張はなく、従ってワード線を越えるリーク電流はない。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】加工マージンの大きい半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置は、主面を有する半導体基板と、半導体基板上に形成された第1絶縁膜と、第1絶縁膜に形成された複数のコンタクト孔と、複数のコンタクト孔内にそれぞれ形成された複数の第1コンタクトプラグと、第1絶縁膜上に形成され、該第1絶縁膜の複数の第1コンタクトプラグが形成された領域を含む所定領域を露出させる開口部を有する第2絶縁膜と、第1絶縁膜のうち開口部で露出した部分に形成され、半導体基板の主面に対して垂直方向に見て、開口部が形成されていない第1絶縁膜の上面の位置よりも低い上面の位置を有する凹部と、開口部を横切り、かつ複数の第1コンタクトプラグのそれぞれの上面に接続されるように、第1絶縁膜の凹部から第2絶縁膜の開口部を経て第2絶縁膜の上面にかけて形成された第2導電膜から成る複数の配線と、を有している。

(もっと読む)

201 - 220 / 550

[ Back to top ]