Fターム[5F083HA06]の内容

Fターム[5F083HA06]に分類される特許

301 - 320 / 569

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。一部の構造及び方法は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。一部の構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得る。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】メモリセル部と周辺回路部との段差を低減させつつ、メモリセル部を積層する。

【解決手段】メモリセル部R1には、層間絶縁膜11と半導体層9とが交互に積層された積層構造をフィン状に半導体基板1上に配置し、周辺回路部R2には、ゲート絶縁膜3を介してゲート電極4を半導体基板1上に配置し、ゲート電極4の上面の高さは、層間絶縁膜11と半導体層9とが交互に積層された積層構造の上面の高さと実質的に等しくなるように設定する。

(もっと読む)

不揮発性半導体記憶装置

【課題】強誘電体キャパシタを積層した構造を有し、読み出し速度を向上させつつ微細化を可能とする不揮発性半導体記憶装置を提供する。

【解決手段】強誘電体キャパシタC1、C2を互いに直列に接続し、強誘電体キャパシタC1、C2の接続点に対する導通状態をセルトランジスタM1にて制御し、プレート線PL0Aを強誘電体キャパシタの他端C1に接続し、プレート線PL0Bを強誘電体キャパシタの他端C2に接続し、ビット線BL0、BL1を共有する複数のメモリセルMC00〜MC03にてプレート線PL0A、PL0Bを共有させる。

(もっと読む)

不揮発性メモリセル及びその製造方法

【課題】同一の基板上に形成されたメモリトランジスタ及び駆動トランジスタを備える透明不揮発性メモリセル及びその製造方法を提供する。

【解決手段】本発明による不揮発性メモリセルは、基板上に形成された半導体膜、バッファー膜、有機強誘電体膜及びゲート電極を含むメモリトランジスタと;前記基板上に形成された前記半導体膜、前記バッファー膜、ゲート絶縁膜及び前記ゲート電極を含む駆動トランジスタと;を備える。本発明によれば、同一の基板上に形成されたメモリトランジスタ及び駆動トランジスタを備え、可視光領域で透明な不揮発性メモリセルを提供することができる。

(もっと読む)

抵抗スイッチ素子および抵抗スイッチメモリ素子

【課題】消費電力の少ない抵抗スイッチ素子を提供する。

【解決手段】抵抗スイッチ素子は、下部電極と、前記下部電極上に形成された誘電体膜と、前記誘電体膜上に形成された上部電極と、前記下部電極と前記上部電極との間に、セット電圧を印加することにより、前記誘電体膜の状態を第1の抵抗状態から、より高抵抗の第2の抵抗状態に遷移させるセット電圧源と、を含み、前記誘電体膜は、非ドープまたは深い不純物でドープされたペロブスカイト膜より構成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】アンチヒューズ素子への書き込み時にゲート電極に電流が分散して流れるのを抑制する。

【解決手段】ゲート電極302の一端からは引き出し配線204を引き出して端子202に接続するとともに、ゲート電極302の他端からは引き出し配線205を引き出して端子203に接続し、引き出し配線204の長さL2は、引き出し配線205の長さL1と異なるように設定する。

(もっと読む)

半導体基板、半導体装置及び半導体装置の製造方法

【課題】半導体層の界面に生じるダングリングボンドをフッ素で終端することで、界面準位を低減することができ、また、低熱履歴のプロセスでも活性領域のみへ効率よくフッ素を導入することができる半導体基板を提供する。

【解決手段】フッ素拡散防止膜6と該フッ素拡散防止膜6上に形成されたフッ素を含有するシリコン酸化膜7からなる絶縁層9と、前記絶縁層9上に形成された半導体層8と、を含み、前記半導体層8とフッ素を含有する前記シリコン酸化膜7とが接触していることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】リーク電流の増加が抑制されたキャパシタを形成可能な半導体装置の製造方法を提供する。

【解決手段】基板上に第1絶縁膜と第2絶縁膜とを順次形成する工程と、第2絶縁膜を貫いて第1絶縁膜内に達する孔部を形成する工程と、孔部の底部及び側面を覆うとともに断面視で凹字型の形状を有する電極を形成する工程と、電極上及び第2絶縁膜上に、電極の上面の一部から第2絶縁膜の上面の一部にかけて開口を有するマスクを形成する工程と、マスクを用いてドライエッチングを行い、開口から露出する第2絶縁膜を除去して第2絶縁膜に開口部を形成すると共に、開口から露出する電極の上部の一部を掘削して電極の上部に切り欠き部を形成する工程と、切り欠き部の端部の少なくとも一部を等方性エッチングにより削る工程とを備える半導体装置の製造方法を採用する。

(もっと読む)

強誘電体メモリ素子の製造方法

【課題】分極方向の均一性が高められた強誘電体層を有し、書き込み及び読み出しに際しての精度を高め得る強誘電体メモリ素子の製造方法。

【解決手段】基板2上に電極3が形成されており、電極3上に強誘電体層4が積層されている積層体を用意し、積層体を空気雰囲気下で熱処理する、強誘電体メモリ素子1の製造方法。

(もっと読む)

犠牲材を使用してダマシンダイオードを作る方法

半導体デバイスを作る方法は、下位層の上にシード材を備える第1の層を形成することと、シード材とは異なる犠牲材を備える第2の層を第1の層の上に形成することと、第1の層および第2の層を複数の分離したフィーチャとなるようにパターニングすることと、複数の分離したフィーチャの間に絶縁充填材を形成することと、絶縁充填材の中に複数の開口部を形成して、複数の開口部の中でシード材を露出させるため、分離したフィーチャから犠牲材を除去することと、複数の開口部の中で露出されたシード材の上に半導体材を成長させることと、を含む。  (もっと読む)

(もっと読む)

パンチスルーアクセスを有する縦型不揮発性スイッチおよびその製造方法

不揮発性メモリセルにアクセスするための半導体装置が提供される。いくつかの実施形態においては、半導体装置は、ソース、ドレインおよびウェルを含む半導体層の縦型スタックを有する。半導体装置へのドレイン−ソースバイアス電圧の印加は、ウェルにわたってパンチスルー機構を生成し、ソースとドレインとの間の電流の流れを発生させる。  (もっと読む)

(もっと読む)

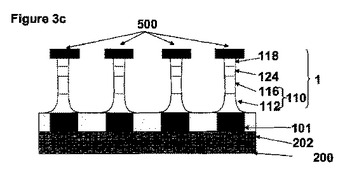

丸いコーナーを有する複数の柱を備えるクロスポイント形不揮発性メモリ装置およびその製造方法

不揮発性メモリ装置が複数の柱(1)を備え、複数の柱のそれぞれは、ステアリング素子(110)および記憶素子(118)を含む不揮発性メモリセルを備え、複数の柱のそれぞれのトップコーナーまたはボトムコーナーの少なくとも一方が丸くされる。不揮発性メモリ装置を製作する方法が、装置層のスタックを形成すること、およびこのスタックをパターン形成して複数の柱を形成することを含み、複数の柱のそれぞれは、ステアリング素子および記憶素子を含む不揮発性メモリセルを備え、複数の柱のそれぞれのトップコーナーまたはボトムコーナーの少なくとも一方が丸くされる。  (もっと読む)

(もっと読む)

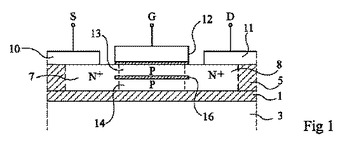

トランジスタを備えるRAM記憶素子

本発明は、ドレイン(8)と、ソース(7)と、絶縁ゲート(12)によって覆われたバルク領域とを有するMOSトランジスタの形状を成すメモリセルに関する。バルク領域の厚さは、ゲート面に平行に延びる絶縁層の部分(16)によって分離される2つの異なる領域(13,14)に分けられる。  (もっと読む)

(もっと読む)

半導体記憶素子

【課題】従来構造のフラッシュメモリと比べてはるかに微細化可能な、フラーレンによるダイポールを利用した半導体記憶素子を提供する。

【解決手段】半導体領域を含む第1の電極11と、第1の電極11上に形成され、膜厚方向に設けられた孔を有する絶縁膜12と、孔の開口部を覆って閉鎖された空間13を形成する金属を含む第2の電極15と、閉鎖空間13内に配置され、電圧の印加により第1または第2の電極11,15のいずれかの側に移動することにより第1の電極11と第2の電極15との間にダイポールを発生させて、フラットバンド電圧をシフトさせるフラーレン14を具備する。

(もっと読む)

非プレーナ型トランジスタを用いた半導体装置および製造方法

【課題】より速い駆動電流およびより小さな短チャネル効果を備え、微細化されたスタティック・ランダム・アクセス・メモリ・セルを提供する。

【解決手段】スタティック・ランダム・アクセス・メモリ・セル300は、半導体基板上の1つ以上のフィンを備える2つの非プレーナ型パスゲート・トランジスタを備える。2つの非プレーナ型プルアップ・トランジスタは、半導体基板上の1つ以上のフィンを備える。2つの非プレーナ型プルダウン・トランジスタは、半導体基板上の1つ以上のフィンを備える。半導体基板上の2つのアシスト・バー314、316は、非プレーナ型プルアップ・トランジスタのフィンの一部と非プレーナ型プルダウン・トランジスタのフィンの一部とを電気的に接続する。

(もっと読む)

圧電素子

【課題】本発明の目的は、セラミックスの結晶化温度を低減させることができ、セラミックスの表面モフォロジを改善することができる、セラミックスの製造方法を提供することにある。

【解決手段】セラミックスの製造方法は、酸素八面体構造を有する複合酸化物材料と、該複合酸化物材料に対して触媒作用を有する常誘電体材料とが混在した膜を形成し、その後該膜を熱処理することを含み、前記常誘電体材料は、構成元素中にSiを含む層状触媒物質、または構成元素中にSi及びGeを含む層状触媒物質からなる。前記熱処理は焼成及びポストアニールを含み、少なくとも該ポストアニールは、加圧された、酸素及びオゾンの少なくとも一方を含む雰囲気中で行われることが望ましい。セラミックスは、酸素八面体構造を有する複合酸化物であって、該酸素八面体構造中にSi及びGeを含む。

(もっと読む)

不揮発性メモリ素子及びその製造方法

【課題】不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】不揮発性メモリ素子及びその製造方法が提供される。本発明の不揮発性メモリ素子は、基板と、互いに対向するように垂直伸張する第1部及び第2部と、前記第1部及び第2部を連結する底部とを前記基板上に含む半導体構造物と、前記半導体構造物の前記第1部及び第2部に沿って離隔配置されて互いに直列に連結された複数のメモリセルと、を含む。本発明の不揮発性メモリ素子の製造方法は、互いに対向するように垂直伸張する第1部及び第2部と、前記第1部及び第2部を連結する底部と、を基板上に含む半導体構造物を前記基板上に形成する段階と、前記半導体構造物の前記第1部及び第2部に沿って離隔配置され、互いに直列に連結された複数のメモリセルを形成する段階と、を含む。

(もっと読む)

不揮発性半導体メモリ

【課題】メモリセルを可及的に小さくできるとともにセル単位で書き込み消去が可能な不揮発性半導体メモリを提供する。

【解決手段】NAND列であって、絶縁膜11上の半導体領域と、ソース/ドレイン領域14a、14bと、チャネル領域12と、電荷をトラップできる電荷トラップ膜20と、磁化の向きが固定された第1のハーフメタル強磁性金属からなるソース/ドレイン電極401とを有し、各電荷トラップ膜上に設けられ、第2のハーフメタル強磁性金属からなるゲート電極30a1、30a2であって、前記ゲート電極は、磁化の向きが前記ソース/ドレイン電極の磁化の向きに略平行な第1の領域と、磁化の向きが略反平行な第2領域から構成され、前記第1の領域が、前記ゲート電極に電流を印加することにより、前記電荷トラップ膜上から前記絶縁膜上へ、及び前記絶縁膜上から前記電荷トラップ膜上へと、可逆的に移動可能となっているゲート電極と、を備える。

(もっと読む)

半導体装置

【課題】コンタクト抵抗を低減し、動作信頼性を向上出来る半導体装置を提供すること。

【解決手段】半導体基板10上に形成された、第1導電型の第1MOSトランジスタ5と、前記半導体基板10上に形成された、第2導電型の複数の第2MOSトランジスタ6と、円形の平面形状を有する第1コンタクトプラグCP10−1と、楕円形の平面形状を有する第2コンタクトプラグCP10−2とを具備し、前記第2コンタクトプラグCP10−2は、前記第2MOSトランジスタ6のいずれか6−1の、ソースまたはドレイン上に形成され、前記第1コンタクトプラグCP10−1は、残りの前記第2MOSトランジスタ6−2、及び前記第1MOSトランジスタ5の、ソースまたはドレイン上に形成される。

(もっと読む)

フラッシュ・メモリ・デバイスおよびその製造方法

【課題】 制御ゲートと浮動ゲートとの間にジグザグ容量を含み、浮動ゲートおよびチャネルに対する制御ゲートの結合を増大するフラッシュ・メモリ・デバイスを提供する。

【解決手段】 フラッシュ・メモリ・デバイスは、ウェハと、このウェハの上に配置されたゲート酸化物層と、このゲート酸化物層、ウェハ、またはそれらの組み合わせの上に配置された浮動ゲートであって、平坦な浮動ゲート部およびこの平坦な浮動ゲート部の選択された領域の上に配置された概ね矩形の浮動ゲート部を含む浮動ゲートと、浮動ゲートの上に配置された高K誘電材料と、高K誘電材料の上に配置された制御ゲートとを含み、高K誘電材料が浮動ゲートを制御ゲートに結合するジグザグ・パターンを形成する。

(もっと読む)

301 - 320 / 569

[ Back to top ]