Fターム[5F083HA06]の内容

Fターム[5F083HA06]に分類される特許

501 - 520 / 569

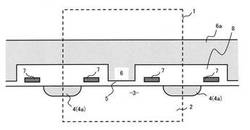

不揮発性半導体記憶装置及びその製造方法

【課題】 ゲート電極の側壁部に電荷蓄積部を配置してなる不揮発性メモリセルにおいて、アライメントずれによる特性バラツキを抑制し、メモリセル面積の縮小化を図る。

【解決手段】 半導体基板2上に形成されたゲート絶縁膜5、ゲート絶縁膜5上に形成されたゲート電極6、ゲート電極6の行方向の両側壁部に形成された電荷蓄積部7、ゲート電極6と電荷蓄積部7の下方に位置するチャネル領域3、及び、チャネル領域3の行方向に両側の半導体基板2表面に埋め込み拡散層で形成された2つの拡散層領域4を備え、行方向に隣接する2つのメモリセルのゲート電極6が、2つの拡散層領域4と電荷蓄積部7の上方を通過して相互に接続して行方向に延伸するゲート電極配線6aを形成し、2つの拡散層領域4がゲート電極配線6aの下方に位置し、列方向に隣接する2つのメモリセルの各拡散層領域4が相互に接続して、列方向に延伸する埋め込み拡散配線4aを形成する。

(もっと読む)

強誘電体メモリ装置及びその製造方法

【課題】製造が容易であり、低電圧下で動作し、データ保持時間に優れた強誘電体メモリ装置及びその製造方法を提供する。本発明においてはシリコン基板1のチャネル領域(4)に対応する部分上に強誘電体層(60)が形成される。この強誘電体層(60)は、例えばPVDFなどの有機物よりなる。この有機物強誘電体層(60)は1V以下の低電圧下で分極特性を示し、この分極特性は経時的に変動せず一定時間以上持続される。従って、低電圧下で動作が可能であり、また簡単な構造および製造方法をもって製造できる強誘電体メモリ装置が具現される。 (もっと読む)

溝に横方向第1ゲート及び縦方向第2ゲートを含むスプリットゲート記憶装置

スプリットゲート記憶装置には、第1ゲート誘電体に接触した第1ゲート電極と、第2ゲート誘電体に接触した第2ゲート電極とが含まれる。第1拡散領域は、半導体基板中に画成された溝(108)の一部の下に横たわり、第2拡散領域は、基板(102)の上部を占有する。第1ゲート誘電体(110)は、溝を内張りする。第1及び第2ゲート誘電体の内の1つには、一層の不連続記憶素子(DSE)(120)が含まれ、第1及び第2ゲート電極の内の1つは、少なくとも部分的に溝内に配置される。一事例では、第1ゲート電極は制御ゲートであり、第1誘電体は一層のDSEを含む。他の事例では、第1ゲート電極は選択ゲートであり、第2誘電体は一層のDSEを含む。第2ゲート誘電体は基板の上面全体に横たわる。  (もっと読む)

(もっと読む)

トレンチ内にナノ結晶記憶要素を含むプログラム可能構造

記憶セルは、トレンチを画成する半導体基板、トレンチの内側を覆う底部誘電体、及び底部誘電体上の電荷格納層を有している。電荷格納層は複数の不連続な記憶要素(DSE)を含んでいる。制御ゲート及び頂部誘電体がDSEを覆っている。記憶セルはトレンチの下にソース/ドレイン領域を有している。DSEはシリコンナノ結晶であってもよく、制御ゲートはポリシリコンであってもよい。制御ゲートは半導体基板の上面の下方までリセス化され、最も上側のDSEは縦方向で制御ゲートの上面に揃えられている。記憶セルは、トレンチの側壁に隣接するシリコンナノ結晶に横方向で揃えられ、且つ最も上側のシリコンナノ結晶から基板の上面まで縦方向に延在している酸化物ギャップ構造を含んでいる。DSE群は少なくとも2つのプログラム可能な注入領域を含んでいる。  (もっと読む)

(もっと読む)

半導体記憶装置のデータ書き込み方法

【課題】 誤読み出し頻度を少なくでき、かつデータ破壊の可能性も小さくできる半導体記憶装置のデータ書き込み方法を提供すること。

【解決手段】 第1メモリセルに隣接した少なくとも1個の第2メモリセルを有する半導体記憶装置のデータ書き込み方法であって、第1メモリセルへのデータ書き込みを行い、第1メモリセルのデータを第1の参照しきい値電圧によって第1の判定をし、第1の判定の結果、第1メモリセルのデータが未達の場合に、第1メモリセルへのデータ書き込み後に第1メモリセルへのデータ再書き込みを行い、第1メモリセルのデータ書き込みを行った後で、第2メモリセルへのデータ書き込みを行い、第1メモリセルのデータを第2の参照しきい値電圧によって第2の判定をし、第2の判定の結果、第1メモリセルのデータが未達の場合に、第2メモリセルへのデータ書き込み後に第1メモリセルへのデータ再書き込みを行う。第1の参照しきい値電圧と第2の参照しきい値電圧とは異なる。

(もっと読む)

切り換え可能な抵抗器とトランジスタとを備えた不揮発性メモリセル

薄膜トランジスタと、切り換え可能な抵抗器メモリ素子とを直列に備える書き換え可能な不揮発性メモリセルが教示される。切り換え可能な抵抗器メモリ素子は、第1の方向に印加されたセット電圧量を受けると抵抗を減少させ、第1の方向と逆の第2の方向に印加されたリセット電圧量を受けると抵抗を増加させる。好ましい実施形態において、メモリセルは、アレイ、好ましくは、複数のメモリレベルが単一の基板の上に形成されるモノリシックな三次元メモリアレイに形成される。好ましい実施形態において、薄膜トランジスタおよび切り換え可能な抵抗器メモリ素子は、互いに平行なデータ線と参照線との間に電気的に配置される。好ましくは、データ線および参照線に対して垂直に延びる選択線がトランジスタを制御する。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】 個々のメモリ素子の特性バラツキに起因する読み出し動作余裕の低減を抑制し、高信頼性で高性能な読み出し動作が可能な半導体記憶装置を提供する。

【解決手段】 第1メモリ機能部Lの電荷蓄積量によりドレインとソースの一方から他方に流れる第1ドレイン・ソース電流Ids1が変化し、第2メモリ機能部Rの電荷蓄積量によりドレインとソースの他方から一方に流れる第2ドレイン・ソース電流Ids2が変化するメモリトランジスタ20と、第1ドレイン・ソース電流Ids1を流して得られる第1読み出し電圧と、第2ドレイン・ソース電流Ids2を流して得られる第2読み出し電圧を比較して、メモリトランジスタの記憶データを読み出す比較回路55を備え、第1メモリ機能部Lと第2メモリ機能部Rの各電荷蓄積量が、第1メモリ機能部Lに書き込まれるデータと第2メモリ機能部Rに書き込まれるデータが相補な関係になるように調整されている。

(もっと読む)

急激な金属−絶縁体転移を利用したメモリ素子及びその動作方法

構造変化を経ずに均一な薄膜を保持して、高速スイッチング動作が可能なメモリ素子及びその動作方法を提供する。その素子及び方法は、電子のエネルギー変化により急激に金属−絶縁体転移をする金属−絶縁体転移物質層にコンタクトさせられ、熱により融解されて転移物質層に導電性経路を形成する少なくとも2個の電極を備える。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】特性バラツキを改善でき、電流駆動能力を向上できる微細化に適した半導体装置及びその製造方法を提供することである。

【解決手段】上記の課題を解決した半導体装置は、半導体基板と、前記半導体基板から突き出し、前記半導体基板上の幅が前記半導体基板中の幅よりも狭い素子分離と、前記素子分離に挟まれた半導体基板部分上に形成された半導体層と、前記半導体層に形成されたMOSFETとを具備する。

(もっと読む)

半導体装置

【課題】 メモリセル領域がダミーセル領域を含む場合でも、メモリセル領域におけるデバイス特性の低下を抑制できる、不揮発性半導体メモリを備えた半導体装置を提供することである。

【解決手段】 半導体装置は、半導体基板1と、半導体基板1上に設けられたメモリセル領域110,120と、メモリセル110,120領域上に設けられたワードラインWLとを具備してなり、ワードラインWL下のメモリセル領域110,120は、第1のゲート絶縁膜2およびその上に設けられた第1の浮遊ゲート電極4、ならびに、第1のゲート絶縁膜2とは厚さが異なる第2のゲート絶縁膜2’およびその上に設けられた第2の浮遊ゲート電極4を含むことを特徴とする。

(もっと読む)

高移動性波形チャネルを有するTFT電荷記憶メモリセル

本発明は、1セルごとに2ビットを有する再書き込み可能な不揮発性メモリセルについて開示する。メモリセルは、チャネルホットエレクトロン注入法により電荷を誘電体電荷記憶層内または電気的に分離された導電性ナノ結晶内に蓄積することにより動作するのが好ましい。好適な実施形態では、チャネル領域は波形形状を有し、2つの記憶領域間にさらなる分離を提供する。チャネル領域は堆積され、好ましくは、チャネル領域を多結晶ゲルマニウムまたはシリコン−ゲルマニウムから形成する。本発明のメモリセルをメモリアレイ内に形成することができる。好適な実施形態では、複数のメモリレベルが、単一基板上に積層されるように形成される。  (もっと読む)

(もっと読む)

ダイオードおよび抵抗率切り換え材料を備える不揮発性メモリセル

基板の上に形成された新規な不揮発性メモリセルにおいて、ダイオードが、可逆的な抵抗率切り換え材料、好ましくは、例えばNix Oy ,Nbx Oy ,Tix Oy ,Hfx Oy ,Alx Oy ,Mgx Oy ,Cox Oy ,Crx Oy ,Vx Oy ,Znx Oy ,Zrx Oy ,Bx Ny およびAlx Ny などの金属酸化物または窒化物と対にされている。好ましい実施形態において、ダイオードは、導体間に配置された垂直な柱として形成される。モノリシックな三次元メモリアレイを形成するために、複数のメモリレベルを積み重ねることが可能である。ある実施形態において、ダイオードは、ゲルマニウムまたは比較的低い温度で堆積および結晶化可能なゲルマニウム合金を備え、導体内でアルミニウムまたは銅を使用できる。本発明のメモリセルは、再書き込み可能なメモリセルまたは1回プログラム可能なメモリセルとして使用でき、2つ以上のデータ状態を記憶できる。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】 不揮発性半導体記憶装置の信頼性を向上することのできる技術を提供する。

【解決手段】 基板1の主面上に形成されたアシストゲートAGと、アシストゲートAG上に絶縁膜11を介して形成されたフローティングゲートFGと、フローティングゲートFGの一方の側壁側で絶縁膜14を介すると共に、アシストゲートAG上に絶縁膜11を介して形成されたコントロールゲートCGとの3つのゲートを有してなる複数のメモリセルを備える。

(もっと読む)

DNRカルコゲニド装置を有する静的RAMメモリおよびその製造方法

SRAMメモリ装置は改善された安定性を持ち2つの直列接続された装置からなりその装置の少なくとも1つは差分負性抵抗特性を表わすカルコゲニド装置である。2つの装置のうちの一方は他方の負荷として働く。スイッチが中間の入力ノードをバイアスしそのメモリ装置を2つの論理状態の間で切り替えるために設けられる。 (もっと読む)

改善されたセル安定性及び性能のためのハイブリッド・バルク−SOI6T−SRAMセル

【課題】 改善されたセル安定性及び性能を示すハイブリッド・バルクSOI 6T STRAMセルを提供すること。

【解決手段】 本発明は、同じ結晶配向又は異なる結晶配向を有するSOI領域及びバルク−Si領域を含む基板と、バルク−Si領域からSOI領域を分離する分離領域と、SOI領域内に配置された少なくとも1つの第1デバイス及びバルク−Si領域内に配置された少なくとも1つの第2デバイスとを含む、6T−SRAM半導体構造体を提供する。SOI領域は、絶縁層の上にシリコン層を有する。バルク−Si領域はさらに、第2デバイスの下にあるウェル領域と、浮遊体効果を安定化させる、ウェル領域へのコンタクトとを含む。ウェル・コンタクトはまた、バルク−Si領域内のFETの閾値電圧を制御して、SOI領域のFET及びバルク−Si領域のFETの組み合わせから構築されたSRAMセルのパワー及び性能を最適化するためにも用いられる。

(もっと読む)

SOC用途のための高密度トレンチ・ベース不揮発性ランダム・アクセスSONOSメモリ・セルの構造及びこれを製造する方法

【課題】 低い電圧でランダム・アクセス及びプログラムが可能な高密度SONOSメモリ・セルを形成するための方法を提供する。

【解決手段】 本発明は、ランダムにアクセス可能なストレージ位置を持つ2トランジスタ・シリコン−酸化物−窒化物−酸化物−半導体(2−Tr SONOS)不揮発性メモリ・セル、及びこれを製造する方法を提供する。1つの実施形態においては、1μmから2μmのトレンチ深さを有するトレンチ構造内にセレクト・トランジスタが配置され、トレンチ構造に隣接する半導体基板の表面にメモリ・トランジスタが配置される、2−Tr SONOSセルが提供される。別の実施形態においては、セレクト・トランジスタとメモリ・トランジスタのいずれも、上述の深さを有するトレンチ構造内に配置される、2−Tr SONOSメモリ・セルが提供される。

(もっと読む)

多層ゲート構造を備える半導体素子及びそれの製造方法

【課題】半導体基板と半導体基板上に形成されたドープされた導電膜を含む半導体素子を提供する。

【解決手段】拡散バリヤ膜がドープされた導電膜上に形成される。拡散バリヤ膜は、非晶質半導体物質を含む。オーミックコンタクト膜が拡散バリヤ膜上に形成される。金属バリヤ膜がオーミックコンタクト膜上に形成される。金属膜が金属バリヤ膜上に形成される。これにより、界面抵抗を所望の範囲内に維持できながら、オーミックコンタクト膜下部の導電体にドープされた不純物が外部に拡散することを効果的に防止できて、多層構造を採用した半導体素子の反転キャパシタンス特性などを向上させることができる。

(もっと読む)

半導体記憶装置

【課題】リークパスの形成を防止できる半導体記憶装置を提供する。

【解決手段】入力保護回路は、P型半導体基板711と、そのP型半導体基板711の表面に形成されたP+型ウェル領域720と、P+型ウェル領域720と電気的に接続するとともにP+型ウェル領域720よりも深くなるようにP型半導体基板711の表面に形成されたP-型ウェル領域713と、P-型ウェル領域713を覆うようにP型半導体基板711の表面に形成されたN-型ウェル領域714とを含んでいる。

(もっと読む)

半導体装置およびその製造方法

【課題】量子ドット体として機能する微粒子の酸化がより確実に抑制された半導体装置およびその製造方法を提供する。

【解決手段】半導体装置20は、半導体基板1と、半導体基板1上に設けられたトンネル絶縁膜3と、トンネル絶縁膜3上に間隔を空けて配置された酸化数が増加しない酸化物半導体からなる微粒子4と、トンネル絶縁膜3上に設けられ、微粒子4を埋め込むSiO2からなる絶縁膜5と、絶縁膜5上に設けられたコントロールゲート6とを備えている。量子ドットとして機能する微粒子4が製造工程中あるいは製造後に酸化されて絶縁体となることがないので、半導体装置は歩留まり良く製造され、且つ信頼性が向上している。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】 データの書込み/読出し時におけるメモリセルの動作速度が従来よりも速い、フルディプレッション型の半導体記憶装置を提供する。

【解決手段】 半導体記憶装置は、半導体基板10と、半導体基板上に設けられた絶縁層20と、絶縁層上に設けられ、該絶縁層によって半導体基板から電気的に絶縁された半導体層30と、半導体層に形成された第1導電型のソース層90と、半導体層に形成された第1導電型のドレイン層91と、ソース層と前記ドレイン層との間の前記半導体層に形成され、電気的に浮遊状態であり、電荷を充放電することによってデータを記憶可能な第1導電型のボディ領域99と、ボディ領域上に形成された第1のゲート絶縁膜50と、第1のゲート絶縁膜上に形成された第1のゲート電極60とを備え、少なくともデータを書き込みまたは読み出すときに、ボディ領域が完全空乏化する。

(もっと読む)

501 - 520 / 569

[ Back to top ]