Fターム[5F083HA06]の内容

Fターム[5F083HA06]に分類される特許

521 - 540 / 569

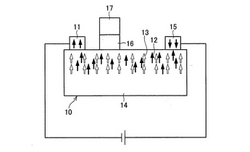

核スピンメモリセルおよび情報処理回路

【課題】 より高性能なメモリセルおよび情報処理回路を実現する。

【解決手段】 本発明のメモリセルは、スピントランジスタ構造を用いてチャンネル14中の核スピン13に電子スピン12を転写することによりメモリ情報を保持するようになっている。

(もっと読む)

容量素子、半導体装置、及び容量素子の製造方法

【課題】 キャパシタ誘電体膜が劣化するのを防止することが可能な容量素子、半導体装置、及び容量素子の製造方法を提供すること。

【解決手段】 基材10と、基材10の上に形成された下地絶縁膜11と、下地絶縁膜11の上に下部電極13、キャパシタ誘電体膜14、及び上部電極15を順に形成してなるキャパシタQと、上部電極15上に形成され、キャパシタQの少なくとも一部を覆う下部保護絶縁膜16aと、下部保護絶縁膜16aの上に形成され、該下部保護絶縁膜16aよりもエネルギバンドギャップが広い上部保護絶縁膜16bと、を有することを特徴とする容量素子による。

(もっと読む)

高Kゲートスタックを備えた不揮発性メモリトランジスタ

メモリ装置は、基板(105)に形成されるソース領域(305)およびドレイン領域(310)と、基板(105)においてソース領域(305)とドレイン領域(310)との間に形成されるチャネル領域(315)とを含んでもよい。メモリ装置は、さらに、チャネル領域(315)の上に形成され、第1の誘電率を有する第1の酸化物層(110)、および第1の酸化物層(110)の上に形成される電荷蓄積層(115)を含んでもよい。メモリ装置は、さらに、電荷蓄積層(115)の上に形成される第2の酸化物層(120)、第2の酸化物層(120)の上に形成され、第1の誘電率より大きい第2の誘電率を有する誘電材料の層(125)、および誘電材料の層(125)の上に形成されるゲート電極(130)を含んでもよい。電荷蓄積層は、誘電材料、例えば窒化物、またはポリシリコンフローティングゲートであり得る。層(125)の材料は、アルミニウム酸化物、ハフニウム酸化物、アルミン酸ハフニウムまたはケイ酸ハフニウムを含む。  (もっと読む)

(もっと読む)

半導体記憶装置及びその製造方法

【課題】ゲート電極の側壁に電荷保持部を有する半導体記憶装置で、書き込み動作の速度を向上させるために電荷保持部をゲート絶縁膜とチャネル領域との界面よりも下に配置する構造では、読み出し電流経路が長くなることを抑制し、読み出しのアクセス時間を短くする。

【解決手段】ゲート電極に垂直な方向の断面において、凸部の段差を有する半導体基板の凸部両側底面であって電荷保持部の直下である領域が、活性領域上では、全てソース/ドレインである拡散層領域の一部である構造にした。さらに、ゲート電極の左右両端部下の基板の凸部側面をオフセット領域とする構造にした。このため、書き込み動作時の電荷注入効率が高いと言う特長を有したまま、従来の構造よりも読み出し電流量を多くすることができる。

(もっと読む)

バックエンドプロセスを使用する相変化抵抗体の製造

相変化抵抗体デバイスは、相変化材料(PCM)を有し、このPCMによって、PCM内部で相転移が起こり、接点電極とのインタフェースでは相転移が起きない。PCMの製造を容易にするために、細長いライン構造(210,215)を、その側面で導電性の電極部(200,240)によって囲み、CMOSのバックエンドプロセスで形成する。代替方法としては、電極なしで直接他の回路部分と結合してこのデバイスを形成するものがある。いずれの場合においても、PCMのラインは、スペーサをハードマスクとして利用して縮小した寸法で形成した、一定の直径または断面積を有する。第1の接点電極および第2の接点電極を、PCMの「一次元的な」層により電気的に接続する。PCMの一次元的な層と第1接点電極および第2接点電極との間の接触抵抗は、上述のラインの中心部分または中間部分の抵抗よりも低い。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】素子の微細化(高集積化)と信頼性の高い安定した高速メモリ動作ができ、2ビット以上の記憶保持ができる半導体記憶装置を提供する。

【解決手段】半導体基板10上に第1,第2の拡散層領域17,18を形成し、その第1,第2の拡散層領域17,18を連結するようにチャネル形成領域31を形成する。上記チャネル形成領域31上にゲート絶縁膜12を形成し、そのゲート絶縁膜12上にゲート電極13を形成する。また、上記ゲート絶縁膜12およびゲート電極13の両側の側壁に電荷保持体61,62を形成する。上記チャネル形成領域31にカーボンナノチューブを用いる。

(もっと読む)

制御可能なナノメカニカルメモリ素子

メモリ装置は、区別可能な双安定状態を振幅変調下で呈するメカニカル素子を備える。これらの状態は、所定周波数の駆動信号の適用によって、動的に双安定性となるか多安定性となる。ヒステリシス効果に関連した素子の固有共振は、区別可能な複数の状態を特定の周波数範囲に亘って生じる。共通コンタクト上に設けられた異なる周波数範囲に対応する多様な素子を持つ複数の装置は、改良された密度で形成される。これらの装置は、起磁式、容量式、圧電式及び/又は光学式方法によって励起され、そして読み取られる。これらの装置は、平面方位付けされるか面外方位付けされて、3次元メモリ構造を可能にする。DCバイアスが、周波数応答をシフトして、素子の状態を弁別するための代替法を可能にすることに使用される。 (もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】 工程数の増加を伴うことなく、FAMOSにおける消去を実現する。

【解決手段】 素子分離絶縁膜2を介してP型不純物拡散層5a、5bと離間して配置されたP型不純物拡散層5cをN型半導体基板1に形成することにより、N型半導体基板1との間でPN接合ダイオードを形成し、フローティングゲート4とP型不純物拡散層5cとを配線層7を介して電気的に接続し、N型半導体基板1を負の電位に設定し、フローティングゲート4に蓄積されたキャリアをP型不純物拡散層5cを介してN型半導体基板1側に引き抜くことにより、FAMOSの消去を実現する。

(もっと読む)

不揮発性メモリ

【課題】 簡単なメモリ構成を有し、製造コストが安い、不揮発性メモリを提供する。

【解決手段】 十字状パターンを有するホール素子3上に絶縁膜2を介して形成された磁性薄膜1からなる不揮発性メモリにおいて、磁性薄膜1を容易軸が前記十字状パターンの電圧出力方向に沿い、かつ前記十字状パターン上に形成し、磁性薄膜1は、矩形状の一軸異方性を有し、少なくともCoとSmとを含有するアモルファス合金からなる不揮発性メモリである。

(もっと読む)

半導体装置、半導体記憶装置および半導体装置の製造方法

【課題】 ゲートからソースへの漏洩電流を伴うことなく、しきい値電圧を可変させるとともに、素子面積の増大を抑制する。

【解決手段】 半導体基板101上には絶縁層102が形成され、絶縁層102上には半導体層103が形成され、さらに、半導体層103上には絶縁層104が形成され、絶縁層104上には半導体層105が形成され、半導体層105上には、ゲート絶縁膜106を介してゲート電極107が形成され、ゲート電極107の側方には、ソース層109およびドレイン層110が形成され、ゲート電極107は、配線層を介して半導体層103に接続されている。

(もっと読む)

CMOS技術における自己整合デュアル・サリサイド形成のための方法

【課題】 従来のデュアル・サリサイド処理における典型的な位置ずれの問題を克服する、新規なデュアル・サリサイド・プロセスを提供すること。

【解決手段】 相補型金属酸化膜半導体(CMOS)デバイスを製作する方法であって、本方法は、第1のタイプの半導体デバイス(130)を収容するために半導体基板(102)の中に第1のウェル領域(103)を形成するステップと、第2の半導体デバイス(140)を収容するために半導体基板(102)の中に第2のウェル領域(104)を形成するステップと、第1のタイプの半導体デバイス(130)をマスク(114)で遮蔽するステップと、第2のタイプの半導体デバイス(140)の上に第1の金属層(118)を堆積させるステップと、第2のタイプの半導体デバイス(140)の上で第1のサリサイド形成を行うステップと、マスク(114)を除去するステップと、第1及び第2のタイプの半導体デバイス(130、140)の上に第2の金属層(123)を堆積させるステップと、第1のタイプの半導体(130)の上で第2のサリサイド形成を行うステップとを含む。本方法は、1つのパターン形成段階しか必要とせず、また、異なるデバイスの上に異なるシリサイド材料を形成するプロセスを単純化するため、パターンの重なりを排除することができる。

(もっと読む)

電極層および誘電体層を含む積層体ユニット

本発明にかかる積層体ユニットは、シリコン単結晶によって形成された支持基板と、支持基板上に、酸化シリコンによって形成されたバリア層と、異方性および導電性を有し、かつ、その上で、ビスマス層状化合物を含む誘電体材料をエピタキシャル成長させることができるBi2Sr2CaCu2O8で表わされる化学量論組成を有するBSCCOによって形成され、c軸方向に配向された電極層と、電極層上で、SrBi4Ti4O15で表わされる組成を有するビスマス層状化合物を含む誘電体材料をエピタキシャル成長させて形成され、c軸方向に配向された誘電体層を備えている。  (もっと読む)

(もっと読む)

半導体チップ

【課題】半導体チップのソフトエラー免疫セル構造を提供する。

【解決手段】ディープNウェル領域107中にメモリデバイスが形成される。メモリデバイスはメモリセルを含む。メモリセルは第1の記憶ノードおよび第2の記憶ノードを含む。メモリセルは、それぞれ第1の記憶ノードおよび第2の記憶ノードと電気的に結合された第1の抵抗および第2の抵抗を含む。メモリセルは、それぞれ第1の記憶ノードおよび第2の記憶ノードと電気的に結合された第1のキャパシタおよび第2のキャパシタを含む。ILD層219はメモリデバイス上に形成される。ILD層219は少なくともホウ素を含まない誘電体材料を含む。IMD層221はILD層219上に形成される。IMD層221の誘電率は3より小さい。ポリイミド(Polyimide)層240はIMD層221上に形成される。ポリイミド層の厚みは20μmより小さい。

(もっと読む)

マルチビット不揮発性メモリセルを含む半導体素子及びその製造方法

【課題】マルチビット不揮発性メモリセルを含む半導体素子及びその製造方法を提供する。

【解決手段】不揮発性半導体素子は、ソース及びドレーン領域がそれぞれ共有される複数のトランジスタを備える単位セルを含み、複数のトランジスタは、それぞれ少なくとも一つのコントロールゲートと少なくとも一つの電荷蓄積領域とを含み、各コントロールゲートは各トランジスタのスレッショルド電圧をシフトするための少なくとも一つのコントロール電圧に連結される。これにより、フラッシュEEPROMの高集積化及びメガバイト当たり低コスト化を効果的に達成できる。

(もっと読む)

強誘電体キャパシタ及びその製造方法、並びに強誘電体メモリ装置

【課題】 強誘電体特性が良好であって、電極膜の剥離が生じにくい、強誘電体キャパシタ及びその製造方法、並びに強誘電体メモリ装置を提供することにある。

【解決手段】 強誘電体キャパシタの製造方法は、基体10の上方に、下部電極20、少なくとも1つの中間電極40、上部電極60が順に配置し、それぞれの電極同士の間に強誘電体膜30,50を設ける。中間電極40の形成工程で、(a)強誘電体膜30の上方に、スパッタ法によって第1の金属膜41を形成し、(b)第1の金属膜41の上方に、蒸着法によって第2の金属膜46を形成する。

(もっと読む)

改良された浮遊ゲート絶縁と浮遊ゲートの製造方法

この発明は、互いにスリットにより分離されている複数の浮遊ゲートを形成する方法、並びに、その浮遊ゲートを用いた半導体装置に関する。この発明は、各々が浮遊ゲート(36)を有する複数半導体装置のアレイを基板(10)上に製造する方法であって、最初に、基板(10)内に複数絶縁領域(14)を形成し、その後、隣接浮遊ゲート(36)間に分離部が形成される位置において、複数絶縁領域(14)上に浮遊ゲート分離部(32)を形成し、浮遊ゲート分離部(32)形成後、浮遊ゲート分離部(32)の部分間において、基板(10)上に複数浮遊ゲート(36)を形成し、その後、隣接浮遊ゲート(36)間にスリットを得るために浮遊ゲート分離部(32)を除去する工程を備えた方法を提供する。この発明は、従来技術に対し、浮遊ゲート材料残留物が少なく、即ち、浮遊ゲート材料による隣接浮遊ゲート間の短絡が少ないという有利な点がある。さらに、従来スリット処理技術に比べてゲート特性が悪くならない。  (もっと読む)

(もっと読む)

電極膜、圧電素子、強誘電体キャパシタ及び半導体装置

【課題】 良好な強誘電体特性が得られる電極膜、圧電素子、強誘電体キャパシタ及び半導体装置を提供することにある。

【解決手段】 電極膜は、基体の上方に形成される白金族金属を含み、CuKα線を用いたθ−2θ法によるX線回折において求められるピークに対応する回折角2θが、電極膜の熱処理後のピークに対応する回折角以上の大きさである。

(もっと読む)

半導体素子及びその製造方法

【課題】 半導体素子及びその製造方法を提供する。

【解決手段】 本発明の一実施形態による半導体素子は、第1のジャンクション領域と第2のジャンクション領域とを有する半導体基板を含む。絶縁されたフローティングゲートは、基板上に形成され、第1のジャンクション領域と少なくとも一部重畳する。絶縁されたプログラムゲートは、フローティングゲート上に形成され、湾曲された上面を有する。半導体素子は、基板上に設けられてフローティングゲートと隣接し絶縁された消去ゲートをさらに含む。消去ゲートは、第2のジャンクション領域と一部重畳する。これにより、自己整列工程を通じて形成された消去ゲートを含み、写真エッチング工程によって製造された従来のEEPROMと比較してセルサイズを縮めさせうる。

(もっと読む)

適応型負性微分抵抗デバイス

【課題】 単一のシリコンウェーハ中に形成した互いに異なる回路に多様な負性微分抵抗(NDR)特性を付与できるように製造工程中または出荷後のフィールドでの通常動作中に最大電流対最小電流比(PVR)値などの特性値を調整できるようにしたNDRデバイスを提供する。

【解決手段】 互いに異なるNDRモードを発現するように動作中に多様にNDR特性を変える過程を含むNDR素子の制御の方法を開示している。NDR素子(シリコン利用のNDR FETなど)に印加するバイアスの条件を変えることによって、最大電流対最小電流比(PVR)値(またはそれ以外の特性)をNDR素子利用回路の所望の動作変化の実現のために動的に変えることができる。例えば、メモリ用または論理回路用では、動作電力の削減のために最小電流値を休止期間中に小さくすることができる。すなわち、適応型NDR素子を慣用の半導体回路の中で有利に活用することができる。

(もっと読む)

マルチレベルの仮想接地メモリのための読出方法

この発明は、両面ONOフラッシュメモリセル(500)におけるビットのレベルを決定するための技術(800)に関する。この場合、両面ONOフラッシュメモリセルのビットの各々は複数のレベル(540、542、544)にプログラミング可能である。この発明の1つ以上の局面は、1つのビット上の電荷のレベルが相補ビット妨害として公知である他のビットに及ぼす恐れのある影響を考慮に入れている。相互コンダクタンスとして公知の測定基準が、より高い解像度および精度をもたらすようビットレベルを決定する際に用いられる。この態様では、この発明の1つ以上の局面に従ったビットレベルの決定により、偽のまたは誤った読出が軽減される。  (もっと読む)

(もっと読む)

521 - 540 / 569

[ Back to top ]