Fターム[5F083HA06]の内容

Fターム[5F083HA06]に分類される特許

541 - 560 / 569

適応型負性微分抵抗デバイス

【課題】 単一のシリコンウェーハ中に形成した互いに異なる回路に多様な負性微分抵抗(NDR)特性を付与できるように製造工程中または出荷後のフィールドでの通常動作中に最大電流対最小電流比(PVR)値などの特性値を調整できるようにしたNDRデバイスを提供する。

【解決手段】 互いに異なるNDRモードを発現するように動作中に多様にNDR特性を変える過程を含むNDR素子の制御の方法を開示している。NDR素子(シリコン利用のNDR FETなど)に印加するバイアスの条件を変えることによって、最大電流対最小電流比(PVR)値(またはそれ以外の特性)をNDR素子利用回路の所望の動作変化の実現のために動的に変えることができる。例えば、メモリ用または論理回路用では、動作電力の削減のために最小電流値を休止期間中に小さくすることができる。すなわち、適応型NDR素子を慣用の半導体回路の中で有利に活用することができる。

(もっと読む)

マルチレベルの仮想接地メモリのための読出方法

この発明は、両面ONOフラッシュメモリセル(500)におけるビットのレベルを決定するための技術(800)に関する。この場合、両面ONOフラッシュメモリセルのビットの各々は複数のレベル(540、542、544)にプログラミング可能である。この発明の1つ以上の局面は、1つのビット上の電荷のレベルが相補ビット妨害として公知である他のビットに及ぼす恐れのある影響を考慮に入れている。相互コンダクタンスとして公知の測定基準が、より高い解像度および精度をもたらすようビットレベルを決定する際に用いられる。この態様では、この発明の1つ以上の局面に従ったビットレベルの決定により、偽のまたは誤った読出が軽減される。  (もっと読む)

(もっと読む)

浮遊ゲート装置において結合係数が改善された自己整合シャロートレンチ分離

本発明は、表面(2)を有する基板上に浮遊ゲート型半導体装置を製造する方法、及びそれによって製造した浮遊ゲート型半導体装置を提供する。本方法は、絶縁膜(4)、浮遊ゲート材料の第1の層(6)及び犠牲材料の層(8)を備えるスタックを基板表面に形成し、スタックを通って、基板(2)中に、少なくとも1つの分離領域(18)を形成し、それによって浮遊ゲート材料の第1の層(6)が上表面及び側壁(26)を有し、犠牲材料(8)を除去し、それによって分離領域(18)及び浮遊ゲート材料の第1の層(6)の上表面によって画定される空所(20)を残し、空所(20)を浮遊ゲート材料の第2の層(22)で充填し、それによって浮遊ゲート材料の第1の層(6)及び浮遊ゲート材料の第2の層(22)が共に浮遊ゲート(24)を形成する工程を備える。  (もっと読む)

(もっと読む)

容量素子とその製造方法

【課題】 キャパシタ誘電体膜の歪みの低減、比誘電率の増大、及びリーク電流の低減の全てを同時に実現することが可能な容量素子とその製造方法を提供すること。

【解決手段】 シリコン基板(基材)1と、シリコン基板1の上に形成された下地絶縁膜2と、下地絶縁膜2の上に下部電極4a、キャパシタ誘電体膜5a、及び上部電極6aを順に形成してなるキャパシタQとを有し、キャパシタ誘電体膜5aが、(Ba1-y,Sry)mYpTiQO3+δ(0<p/(p+m+Q)≦0.015、−0.5<δ<0.5)で表される材料により構成されることを特徴とする容量素子による。

(もっと読む)

メモリセル構造

【課題】 従来技術の問題およびその他の問題を解決するメモリセル構造のシステムを提供する。

【解決手段】 SRAMデバイスは基板中のディープNウェル領域中にあるSRAMセルを含む。SRAMセル中のPウェル領域は、SRAMセルの65%よりも少ないセル領域を占める。SRAMセルは、セル領域の長辺と短辺との比率が1.8よりも大きい。SRAMセル中の複数のNMOSトランジスタ中にある活性領域が占める総面積は、SRAMセル領域の25%よりも少ない。SRAMセル中のプルアップトランジスタのチャネル幅とSRAMセル中のプルダウントランジスタのチャネル幅との比率は0.8よりも大きい。SRAMセルは、ホウ素を含まない層間絶縁膜層と、誘電率が3よりも小さい金属間絶縁膜層と、厚みが20ミクロンよりも小さいポリイミド層とをさらに含む。

(もっと読む)

容量素子およびそれを用いた半導体装置、半導体装置の製造方法

【課題】スパッタ法により形成したペロブスカイト型酸化物高誘電体薄膜を用いた容量素子において、低リーク電流と高比誘電率の両立を可能とし、高品質の容量素子を提供する。

【解決手段】本発明の容量素子は、Ti膜103/Pt膜104からなる下部電極とPt膜108からなる上部電極との間にSrTiO3膜からなる容量誘電体膜を備えている。容量誘電体膜は2層に分かれており、主要部分はSrを過剰に含むSrTiO3膜105で、上部電極側の層はTiを過剰に含むSrTiO3膜107からなる。

(もっと読む)

電子装置、及びキャパシタへの電圧印加方法

【課題】 キャパシタ誘電体膜の劣化を防止してキャパシタを長寿命化させることができる電子装置、及びキャパシタへの電圧印加方法を提供すること。

【解決手段】 シリコン基板(基材)1と、シリコン基板1の上に形成された下地絶縁膜2と、下地絶縁膜2の上に下部電極4a、キャパシタ誘電体膜5a、及び上部電極6aを順に形成してなるキャパシタQと、下部電極4aと上部電極6aの少なくとも一方に両極性の波形を有する電圧を供給する電圧供給回路12とを有し、この電圧の振幅が、5×105d(V)(d:上部電極6aと下部電極4aとの間隔(cm))以下であることを特徴とする電子装置による。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、信頼性の高く、且つしきい値電圧の変化量を高めることが可能な半導体不揮発性記憶素子を有する半導体装置の作製方法を提供する。また、信頼性の高い半導体不揮発性記憶素子を有する半導体装置を、大面積基板を用いて製造する方法を提供する。

【解決手段】本発明は、固溶限界を超えるシリコンを有する固溶体をターゲットとしてスパッタリングを行い、固溶体の主成分である金属元素の導電層と、シリコン粒子とからなる導電膜を成膜した後、金属元素の導電層を除去してシリコン粒子を露出する。また、当該シリコン粒子をフローティングゲート電極とする半導体不揮発性記憶素子を有する半導体装置を作製する。

(もっと読む)

スピントランジスタ、プログラマブル論理回路および磁気メモリ

【課題】増幅機能を有するスピントランジスタを提供すること。

【解決手段】スピントランジスタ100は、半導体基板10と、半導体基板10上において第1方向に磁化された強磁性体で形成される第1導電層12と、半導体基板10上において第1方向とその第1方向に対して反平行の第2方向とのいずれか一方に磁化される強磁性体で形成された第2導電層14と、第1導電層12と第2導電層14の間に位置し、第1導電層12と第2導電層14との間で電子スピンを導くチャネル部と、チャネル部の上方に位置するゲート電極40と、第1導電層12および第2導電層14の少なくとも一方とチャネル部との間に位置するトンネルバリア膜11a,11bと、を備える。

(もっと読む)

自己スイッチングメモリデバイス

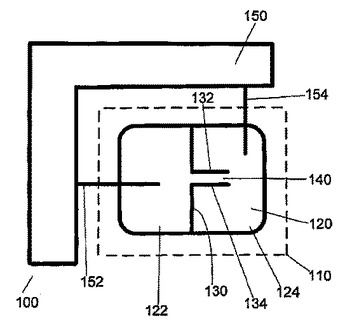

メモリデバイス、及び関連する製造及び動作の方法を説明している。該メモリデバイスは、移動電荷キャリアを支持する基板(120)を具えている少なくとも1つのメモリユニットを含む。該基板表面上には絶縁部(130、132、134)が形成され、該絶縁部の両側に第1及び第2基板領域(122、124)を形成している。該第1及び第2基板領域は、絶縁部によって形成された細長チャネル(140)によって接続されている。メモリユニットは、前記第1及び第2領域間の所定の電位差でチャネルが第1及び第2領域間に第1のコンダクタンスを与える第1の状態と、前記所定の電位差でチャネルが第1及び第2領域間に第2の異なるコンダクタンスを与える第2の状態との間で切り換え可能である。メモリユニットを第1の状態に変更するため、前記メモリユニットの第1及び第2領域に第1の電位差を、そしてメモリユニットを第2の状態に変更するため第2の異なる電位差を印加するよう、書き込み回路(150)が構成されている。メモリユニットの状態を読み出すため、メモリユニットの第1及び第2領域に前記所定の電位差を印加するよう、読み出し回路(150)が構成されている。  (もっと読む)

(もっと読む)

不揮発性メモリーデバイスおよびそれの形成方法

一実施形態において半導体デバイス(10)は、半導体基板(20)中に均一に注入された第1の導電型を有する高ドープ層(26)を有し、基板(20)の頂部表面と高ドープ層(26)との間にはチャンネル領域(28)が配置されている。別の実施形態では半導体デバイス(70)は、カウンタドープされたチャンネル(86)およびそのチャンネルの下のパンチスルー防止領域(74)を有する。ゲートスタック(32)を基板(20)上に形成する。第2の導電型を有するソース(52)およびドレイン(54,53)をその基に注入する。得られた不揮発性メモリーセルは、低い自然閾値電圧を与えることで、読取サイクル時の閾値電圧ドリフトを小さくする。さらに、第2の導電型を有し、ドレイン側に斜めで注入されたハロー領域(46)を用いて、熱キャリア注入を支援することができ、それによってより高いプログラミング速度が可能となる。  (もっと読む)

(もっと読む)

Al2O3誘電体を用いるメモリ・セルの絶縁構造

【構成】この発明は,一例示的実施形態では,基板上に形成され,基板をバイアスし,集積回路構造(たとえば,DRAMメモリ・セル)の隣接する動作領域間を絶縁する絶縁ゲートを提供する。ゲート誘電体として,従来のゲート酸化物層ではなく,酸化アルミニウム(Al2O3)を用いて,トレンチ(溝)絶縁領域の下および近くに正孔過剰な蓄積領域を形成する。この発明の別の例示的実施形態は,シャロー・トレンチ(溝)絶縁(STI)領域の効果を高めるために絶縁領域内のライナとして利用される酸化アルミニウム層を提供する。これらの実施形態は,絶縁領域において一緒に用いることも可能である。 (もっと読む)

半導体記憶装置およびその製造方法並びに携帯電子機器

【課題】微細化が容易な半導体記憶装置を提供する。

【解決手段】半導体基板211上には、ゲート絶縁膜214を介して単一のゲート電極217を形成している。ゲート電極217の両側には、第1,第2のメモリ機能体261,262を形成している。半導体基板211のゲート電極217側の表面部にはP型のチャネル領域472を形成し、チャネル領域472の両側にN型の第1,第2の拡散領域212,213を形成している。チャネル領域472は、第1,第2のメモリ機能体261,262下に位置するオフセット領域401と、ゲート電極217下に位置するゲート電極下領域402とで構成されている。オフセット領域401にP型の導電型を与える不純物の濃度は、ゲート電極下領域402にP型の導電型を与える不純物の濃度に比べて実効的に薄くなっている。

(もっと読む)

ナノクラスタ電荷蓄積デバイスの形成方法

一実施形態では、ナノクラスタ電荷蓄積デバイスを形成する方法が提供される。半導体装置(10)の第1の領域(26および30)が1つまたは複数の非電荷蓄積デバイスを配置するために特定される。この半導体装置の第2の領域(28)が1つまたは複数の電荷蓄積デバイスを配置するために特定される。この1つまたは複数の非電荷蓄積デバイスのゲート絶縁体として使用されるゲート酸化物(22)がこの半導体装置の第1の領域(26および30)中に形成され、引き続きナノクラスタ電荷蓄積層がこの半導体装置の第2の領域(28)中に形成される。  (もっと読む)

(もっと読む)

半導体装置及びその作製方法

【課題】本発明は、低コストで大量生産が可能である半導体装置及びその作製方法を提供する。また、非常に膜厚の薄い集積回路を用いた半導体装置、及びその作製方法を提供する。更には、低消費電力である半導体装置及びその作製方法を提供する。

【解決手段】本発明は、絶縁表面上に半導体不揮発性記憶素子トランジスタを有し、メモリトランジスタのフローティングゲート電極が、複数の導電性粒子又は半導体粒子で形成されていることを特徴とする半導体装置である。

(もっと読む)

電気デバイスおよびその製造方法

本発明は、パンチスルーダイオード(S)と直列に接続されたプログラマブル抵抗器(PR)を有する電気デバイス(図6)に関する。本発明はまた、そのような電気デバイスの製造方法に関する。前記方法は、第1の導電型とは反対の第2の導電型の半導体材料からなる第2の層と第3の層との間に配置された、第1の導電型の半導体材料からなる第1の層を含む積層体を設けるステップと、プログラマブルな抵抗率を有する材料の層であって、半導体材料の第2および第3の層のうちの1つと電気的に接触している、プログラマブルな抵抗率を有する材料の層を設けるステップとを含む。  (もっと読む)

(もっと読む)

分離領域上に消去ゲートを有する不揮発性メモリ

本発明は、不揮発性メモリ装置及びそのような装置の製造方法を提供する。この装置は、浮遊ゲート(16)と、制御ゲート(19)と、分離した消去ゲート(10)とを備える。消去ゲート(10)は、基板(1)内に設けられた分離領域(2)中に、又はその上に設けられる。そのため消去ゲート(10)は、セル・サイズを増加させない。消去ゲート(10)と浮遊ゲート(16)との間の容量は、制御ゲート(19)と浮遊ゲート(16)との間の容量に比べて小さく、消去ゲート(10)と浮遊ゲート(16)との間の酸化物層を介してファウラー・ノルドハイム・トンネルによって浮遊ゲート(16)の帯電が消去される。  (もっと読む)

(もっと読む)

アレイ状に配置された垂直型カーボン・ナノチューブ電界効果トランジスタを製造する方法、並びに、それによって形成された電界効果トランジスタ及びアレイ

【課題】 カーボン・ナノチューブ電界効果トランジスタと、カーボン・ナノチューブ電界効果トランジスタのアレイと、デバイス構造体とを製造するための方法、及び、該方法によって形成されたデバイス構造体のアレイを提供する。

【解決手段】 本方法は、ゲート電極層と、各々がソース/ドレイン・コンタクトと電気的に結合された触媒パッドとを含む積層構造体を形成することを含む。ゲート電極層は多数のゲート電極に分割され、少なくとも1つの半導体カーボン・ナノチューブが、化学気相堆積プロセスによって触媒パッドの各々の上に合成される。完成したデバイス構造体は、ゲート誘電体によって覆われた側壁を有するゲート電極と、該ゲート電極の該側壁に隣接する少なくとも1つの半導体カーボン・ナノチューブとを含む。ソース/ドレイン・コンタクトを半導体カーボン・ナノチューブの両端と電気的に結合することによって、デバイス構造体が完成する。多数のデバイス構造体は、メモリ回路又は論理回路のいずれかとして構成することができる。

(もっと読む)

トンネル層に量子ドットを有するトランジスタ

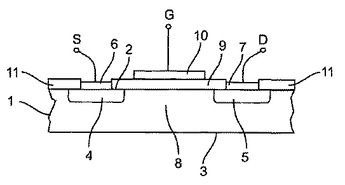

本発明は、半導体本体(1)内に配置された半導体部品を記述したもので、前記半導体部品は、第1の導電型である少なくとも1つのソース領域(4)及び少なくとも1つのドレイン領域(5)を有し、ソース領域とドレイン領域の間に配置された第2の導電型である少なくとも1つの本体領域(8)を有し、絶縁層(9)により半導体本体から絶縁された少なくとも1つのゲート電極(10)を有し、前記絶縁層(9)は好ましくは焼結された一体化量子ドット含有層である。本発明は更に、量子ドット含有誘電性懸濁液が半導体本体に塗布され、次に例えば焼結によって一体化される上記の半導体部品の作製方法を記述する。  (もっと読む)

(もっと読む)

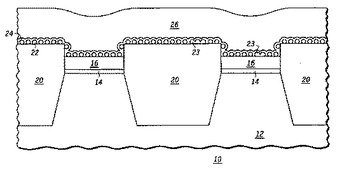

改良された表面形状を用いるメモリ構造の形成方法及びその構造。

半導体装置10のゲートカップリング比を増大させるため、超微細結晶等の個別素子22が浮遊ゲート16上に析出される。一実施形態において、個別素子22は、蒸気相中で予め形成され、静電気力によって半導体装置10に吸着される。一実施形態において、個別素子22は、それらが吸着されるチャンバとは異なるチャンバ内で予め形成される。更に別の実施例において、同じチャンバが全ての析出工程に使用される。界面層17は、必要に応じて、浮遊ゲート16と個別素子22との間に形成される。  (もっと読む)

(もっと読む)

541 - 560 / 569

[ Back to top ]