Fターム[5F083HA06]の内容

Fターム[5F083HA06]に分類される特許

341 - 360 / 569

シリコン系ナノスケールクロスバーメモリ

本願はクロスバーメモリアレイを記載する。メモリアレイは、第1の材料からなる並列ナノワイヤの第1のアレイ、および第2の材料からなる並列ナノワイヤの第2のアレイを含む。第1のアレイおよび第2のアレイは互いにある角度で方向付けられる。アレイは、さらに、第1の材料からなるナノワイヤと第2の材料からなるナノワイヤとの間において2つのアレイの各交差部に配置される非結晶質シリコンからなる複数のナノ構造を含む。ナノ構造は第1の材料からなるナノワイヤおよび第2の材料からなるナノワイヤとともに抵抗メモリセルを形成する。  (もっと読む)

(もっと読む)

窒化シリコン電荷トラップ層を有する不揮発性メモリ

フラッシュメモリデバイス及びフラッシュメモリデバイスを形成する方法を提供する。1つのバージョンでは、フラッシュメモリデバイスは、炭素、ホウ素、又は酸素を含むドーパントを有するドープト窒化シリコン層を含む。ドープト窒化シリコン層は、層中に発生する窒素ダングリングボンド及びシリコンダングリングボンドの数及び濃度を増大させ、不揮発性メモリデバイスのユニットセルの電荷保有能力及び電荷保持時間を増加させる。  (もっと読む)

(もっと読む)

スプリットゲート・メモリセルの形成方法

方法は、半導体基板(12)上にゲート材料の第一層(18)を形成すること、第一層上にハードマスク層(20)を形成すること、開口(22)を形成すること、ハードマスク層上と開口内とに電荷蓄積層(24)を形成すること、電荷蓄積層上にゲート材料の第二層(26)を形成すること、ハードマスク層を被覆している、第二層の一部と電荷蓄積層の一部とを除去することであって、第二層の第二部分が開口内に残存している、除去すること、ハードマスク層上と第二部分上とに、第一ビットセル及び第二ビットセルの両方を画定するパターン化されたマスク層(28、30、32)を形成すること、パターン化されたマスク層を用いて第一ビットセル及び第二ビットセルを形成することを含み、第一ビットセル及び第二ビットセルはそれぞれ、第一層から形成された選択ゲート(38、40)と、第二層から形成された制御ゲート(34、36)とを含む。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置

【課題】プログラム時にヒューズ素子の絶縁膜に金属原子が侵入するのを抑制する。

【解決手段】ヒューズ素子11のMOSトランジスタのシリサイド層47a、47bは、サイドウォール49a、49bからそれぞれ所定の間隔を隔てて不純物拡散層46a、46b上に形成するとともに、シリサイド層47dは、ゲート酸化膜43上のゲート電極44上を避けるようにしてゲート電極44上のコンタクト領域に形成する。

(もっと読む)

半導体記憶装置、及び半導体装置

【課題】記憶装置へのデータの書き込みまたは読み出しの際の誤動作が少なく、及び/または記憶素子の集積度の向上を図れるアンチヒューズ型の記憶装置を提供することを課題の1つとする。

【解決手段】複数のワード線と、複数のビット線と、複数のワード線のいずれか、及び複数のビット線のいずれか、の交差部に応じて設けられたメモリセルと、を有し、メモリセルは、pin型ダイオード及びアンチヒューズを有し、pin型ダイオードの陽極は、ビット線のいずれかに電気的に接続され、pin型ダイオードの陰極は、アンチヒューズの第1端子に電気的に接続され、アンチヒューズの第2端子は、ワード線のいずれかに電気的に接続され、アンチヒューズは、電極に挟持されたシリコン層及び絶縁層を有する。

(もっと読む)

電子デバイス材料の製造方法

【課題】電気的特性の優れた絶縁膜のプラズマ処理方法を提供する。

【解決手段】本発明に係るプラズマ処理方法の一形態は、絶縁膜が形成された基板を真空容器内に搬入する工程と、上記真空容器内に供給された処理ガスに300MHz以上2500MHz以下の周波数を有する高周波電力を供給することによりプラズマを生成し、上記プラズマにより、上記絶縁膜を改質する工程と、を含むプラズマ処理方法であって、上記処理ガスは、希ガスと酸素を含む混合ガス、または希ガスと窒素を含む混合ガスであり、上記プラズマは、上記処理ガスが希ガスと酸素を含む混合ガスの場合、上記酸素ガスの流量を1〜1000sccm、上記希ガスの流量を200〜3000sccmとして、上記処理ガスが希ガスと窒素を含むガスの場合、窒素ガスの流量を10〜500sccm、上記希ガスの流量を200〜3000sccmとして生成される。

(もっと読む)

金属酸化物層の製造方法

【課題】金属酸化物層の表面のアモルファス層を低減し、金属酸化物層の誘電率を向上させること。

【解決手段】金属酸化物の前駆体層を分解して金属酸化物層を形成する工程と、金属酸化物層にレーザを照射して前記金属酸化物層を結晶化する工程と、結晶化された金属酸化物層に対して、10〜300Hzの間隔で、最初のパルスの照射フルエンスを60〜100mJ/cm2とし、最後のパルスの照射フルエンスを10mJ/cm2以下とし、照射フルエンスの減少速度Vが−150≦V[mJ/(cm2min)]<0となるように、各パルスの照射フルエンスを減少させながらパルスレーザを照射する除冷工程と、を備える金属酸化物層の製造方法。

(もっと読む)

半導体装置、半導体製造装置および半導体装置の製造方法

【課題】半導体基板上の凹部が逆テーパ形状やオーバーハング形状を有する場合においても、埋め込み性や膜質の劣化を抑制しつつ、埋め込み絶縁膜の応力を低減することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上にトレンチ5を形成し、熱CVD法を用いることで、トレンチ5内の一部を埋め込む埋め込み絶縁膜6を半導体基板1上に成膜し、埋め込み絶縁膜6の成膜時よりも高い温度にて埋め込み絶縁膜6を熱処理した後、熱CVD法を用いることで、トレンチ5内の一部を埋め込む埋め込み絶縁膜7を埋め込み絶縁膜6上に成膜し、埋め込み絶縁膜7の成膜時よりも高い温度にて埋め込み絶縁膜7を熱処理した後、熱CVD法を用いることで、トレンチ5内を完全に埋め込む埋め込み絶縁膜を埋め込み絶縁膜7上に成膜し、埋め込み絶縁膜の成膜時よりも高い温度にて埋め込み絶縁膜を熱処理する。

(もっと読む)

拡幅活性領域を有する半導体素子

半導体素子(10)を半導体層内に、そして半導体層の上に形成する方法が実現される。トレンチ(18,20,22)は、第1活性領域(24,26,28,30)に隣接して形成される。前記トレンチには、絶縁材料(32,34,36)が充填される。マスクパターン(48,50,52)を前記トレンチの中央部分の上に形成して、前記トレンチのうち、前記マスクパターンの第1側部と前記第1活性領域との間に位置する第1側部を露出させる。前記トレンチの前記第1側部を掘り込むエッチングを行なう工程によって、第1窪み(54,56,58,60)が前記トレンチに残る。第1エピタキシャル領域(62,66)を前記第1窪みに成長させて、前記第1活性領域を延長して前記第1窪みを包含することにより、第1拡幅活性領域を形成する。  (もっと読む)

(もっと読む)

記憶素子及び記憶素子の作製方法

【課題】低電圧で書き込み、読み出しを行うことができる、消費電力の小さい安価な記憶素子と、その製造方法を提供する。

【解決手段】絶縁性基板100上の第1の導電体101上に、0.1μm以上10μm以下の大きさの導電性を有する粒子、溶媒及び樹脂を含む導電性ペースト102を配置し、溶媒を気化させて導電性ペースト102中に含まれる導電性を有する粒子103同士を接触させ、導電性ペースト102の導電性を向上させる。一方、第1の導電体101と導電性を有する粒子103の間には、薄い樹脂の層105が残存し、樹脂の層105は、電圧印加によって絶縁破壊させることが可能である。そのため、樹脂の層105は、メモリ層として機能させることが可能である。このように、メモリ層を有する第2の導電体106を形成することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】CMP(Chemical Mechanical Polishing)ストッパ膜を終点検出膜として利用しつつ、CMPによる平坦化精度を向上させる半導体装置及びその製造方法の提供。

【解決手段】ゲート電極3a上にはシリサイド層7aを形成するとともに、ゲート電極3b上にはシリサイド防止膜4bを形成し、半導体基板1上の第1の領域においては、シリサイド防止膜4bが露出するように、犠牲膜10、CMPストッパ膜9および層間絶縁膜8のCMPを行い、第2の領域においては、CMPストッパ膜9が露出するように、犠牲膜10のCMPを行うことで、第1の領域R1および第2の領域R2を平坦化する。

(もっと読む)

半導体記憶装置

【課題】高耐圧トランジスタのオフ時のリーク電流を抑制し、周辺回路内部の電圧を安定化することが可能な、NAND型フラッシュメモリ等に適用される半導体記憶装置を提供する。

【解決手段】周辺回路領域PRにおいて、シリコン基板11の一部にシリコンよりバンドギャップの広いSiCやGaN等の半導体層14が形成されている。メモリセル13は、シリコン基板11内に形成されている。周辺回路を構成するトランジスタ15は半導体層14内に形成されている。半導体層14のバンドギャップは、シリコンのバンドギャップより広いため、トランジスタ15がオフ状態において、トンネル電子が発生しない。このため、GIDLの発生を抑制することができる。

(もっと読む)

不揮発性メモリデバイスを製作する方法

半導体デバイスを製作する方法は、絶縁層(108)に取り囲まれた柱形半導体デバイスを形成するステップであって、絶縁層内のコンタクトホール(111)が半導体デバイスの上面を露出させるステップを含む。この方法はまた、絶縁層(108)上にシャドウマスク層(302)を形成するステップであって、シャドウマスク層(302)の一部分がコンタクトホール(111)の一部分に突出するステップと、導電層を形成するステップであって、導電層の第1の部分(304)がコンタクトホール内に露出する半導体デバイスの上面に位置し、導電層の第2の部分(306)がシャドウマスク層(302)上に位置するステップと、シャドウマスク層(302)と導電層の第2の部分(306)とを除去するステップと、を含む。  (もっと読む)

(もっと読む)

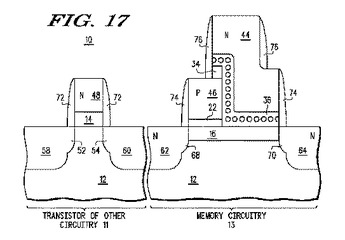

スプリット・ゲート・メモリ・デバイスの形成方法および装置

スプリット・ゲート・メモリ・デバイス(10)は、第1の仕事関数を有する選択ゲート(46)を基板(12)の第1の部分の上に有する。第2の仕事関数を有する制御ゲート(44)は、第1の部分に隣接する基板の第2の部分の上にある。スプリット・ゲート・メモリ・デバイス(10)の多数キャリアが電子であるとき、第1の仕事関数は第2の仕事関数よりも大きい。スプリット・ゲート・メモリ・デバイス(10)の多数キャリアがホールであるとき、第1の仕事関数は第2の仕事関数よりも小さい。基板(12)内の第1の電流電極(62)および第2の電流電極(64)は、制御ゲートおよび選択ゲートの下にあるチャネルによって分離される。制御ゲートおよび選択ゲートの異なる仕事関数は、デバイス性能を最適化するために各ゲートに対して異なる閾値電圧をもたらす。nチャネルデバイスでは、選択ゲートはp導電型であり、制御ゲートはn導電型である。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法、および光変調装置およびその製造方法

【課題】自己整合でエッチング可能かつ製造方法の容易な光変調装置およびその製造方法を提供する。

【解決手段】下部電極2と、下部電極2上に配置される強誘電体膜3と、強誘電体膜3上に配置される上部電極4とを備えた強誘電体キャパシタを含む光変調装置であって、上部電極4が、強誘電体膜3のエッチングマスクとして強誘電体膜3と自己整合パターニングされた導電膜を含んでいることを特徴とし、さらに強誘電体キャパシタを駆動するための制御回路を半導体基板10上に有するとともに、強誘電体キャパシタを、下部電極2と上部電極4間に印加する電界に応じて強誘電体膜3の屈折率が変化するファブリーペロー型の共振器6として機能させる。

(もっと読む)

別々の読み出し及び書き込みアクセストランジスタを有するゲート型横型サイリスタベースランダムアクセスメモリ(GLTRAM)セル並びにそれを組み込んだメモリデバイス及び集積回路

【解決手段】

書き込みビット線(452)、読み出しビット線(454)、及び少なくとも1つのメモリセル(410)を含むメモリデバイス(340)が提供される。メモリセル(410)は、書き込みアクセストランジスタ(470)と、読み出しビット線(454)及び先の書き込みアクセストランジスタ(470)に結合される読み出しアクセストランジスタ(480)と、先の書き込みアクセストランジスタ(470)に結合されるゲート型横型サイリスタ(GLT)デバイス(460)とを含む。その多くの特徴の中でも、メモリセル(410)は、読み出し及び書き込みビット線(454,452)を分離することによって読み出し動作中の読み出し障害を回避する。

(もっと読む)

ゲート型横型サイリスタベースランダムアクセスメモリ(GLTRAM)セルを製造するための方法

【解決手段】

ゲート型横型サイリスタベースメモリデバイス(gltram)を製造するための方法が提供される。半導体層(406)内の第1の伝導性タイプの第1、第2、第3及び第4のウエル領域(463,471,486,493)を含む半導体層(406)が設けられる。第1のゲート構造(465/408)は第1のウエル領域(463)上にあり、第2のゲート構造(475/408)は第2のウエル領域(471)上にあり、第3のゲート構造(485/408)は第3のウエル領域(486)上にあり且つ第2のゲート構造(475/408)と一体であり、第4のゲート構造(495/408)は第4のウエル領域(493)上に配置される。第1のゲート構造(465/408)の第1の側壁(414)及び第2乃至第4のゲート構造(475/408,485/408,495/408)の側壁(412,413,416,417,418,419)に隣接して側壁スペーサ(469)が形成される。また、第1のウエル領域(463)の部分(468)及び第1のゲート構造(465/408)の部分を覆う絶縁スペーサブロック(467)が形成される。絶縁スペーサブロック(467)は第1のゲート構造(465/408)の第2の側壁(415)に隣接する。第1のゲート構造(465/408)に隣接して第1のソース領域(472)が形成され、第1及び第2のゲート構造(465/408,475/408)の間に共通ドレイン/カソード領域(474/464)が形成され、第3のゲート構造(485/408)に隣接して第2のソース領域(482)が形成され、第3及び第4のゲート構造(485/408,495/408)の間に共通ドレイン/ソース領域(484/492)が形成され、第4のゲート構造(495/408)に隣接してドレイン領域(494)が形成される。第1のゲート構造(465/408)に隣接する絶縁スペーサブロック(467)の下で第1のウエル領域(463)内に延在する第1のベース領域(468)が形成され、第1のベース領域(468)に隣接する第1のウエル領域(463)内に延在するアノード領域(466)が第1のウエル領域(463)内に形成される。

(もっと読む)

強誘電体メモリ装置およびその製造方法

【課題】酸素バリア性と水素バリア性を有し、強誘電体キャパシタの構造が簡単で製造方法が容易な強誘電体メモリ装置およびその製造方法を提供する。

【解決手段】プラグ電極24に接続された導電性バリア膜1と、導電性バリア膜1上に配置され、導電性バリア膜1を介してプラグ電極24に接続された下部電極2と、下部電極2上に配置された強誘電体膜3と、強誘電体膜3上に配置された上部電極4と、上部電極4上に配置された導電性水素バリア膜5と、導電性水素バリア膜5上に配置され、導電性水素バリア膜5を介して上部電極4に接続されたVIA電極26と、導電性水素バリア膜5上、および導電性バリア膜1,下部電極2、強誘電体膜3,上部電極4,および導電性水素バリア膜5の側壁上に配置された絶縁性水素バリア膜6とを備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル当たり2ビットを記憶可能な不揮発性半導体記憶装置を提供することを課題とする。

【解決手段】半導体基板の表面層に備えられたチャネル領域を挟む一対の不純物拡散領域と、チャネル領域上に備えられたゲート絶縁膜をチャネル長方向で挟む一対の電荷保持膜と、ゲート絶縁膜及び一対の電荷保持膜上に備えられた単一層からなるゲート電極とを含むメモリセルを、チャネル長方向及びチャネル幅方向のそれぞれに少なくとも2つずつ隣接して有し、チャネル長方向に隣接するメモリセル間の不純物拡散領域が、隣接するメモリセルで共有され、チャネル長方向に隣接するメモリセルのゲート電極上に、チャネル長方向に隣接するメモリセルで共有されるワード線を備え、一対の不純物拡散領域が、チャネル幅方向で隣接するメモリセルにおいてそれぞれビット線として共有された不揮発性半導体記憶装置により上記課題を解決する。

(もっと読む)

半導体記憶装置、及び半導体装置

【課題】トランジスタを絶縁破壊させることなく、記憶素子において確実にデータの書き込みを行うことを課題とする。

【解決手段】半導体記憶装置は、電位制御回路100と、ゲート端子、ソース端子、及びドレイン端子を有するトランジスタ101と、電位供給端子102と、第1端子及び第2端子を有する記憶素子103と、を有する。データ書き込み時において、記憶素子103の第2端子には負電位が与えられる。また、トランジスタ101のゲート端子とソース端子の電位差が、トランジスタ101の閾値電圧以上であり、且つトランジスタ101の絶縁耐圧以下である。また、記憶素子103の第1端子と第2端子の電位差が、トランジスタ101の絶縁耐圧より高く、且つ記憶素子103の書き込みに必要な電圧以上である。

(もっと読む)

341 - 360 / 569

[ Back to top ]