Fターム[5F083HA06]の内容

Fターム[5F083HA06]に分類される特許

221 - 240 / 569

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】ゲート電極を形成し、ゲート電極上に第1の絶縁膜を形成し、第1の絶縁膜にハロゲンドープ処理を行って、第1の絶縁膜にハロゲン原子を供給し、第1の絶縁膜上に、ゲート電極と重畳して酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供給し、酸素原子が供給された酸化物半導体膜に熱処理を行い、酸化物半導体膜上に接して、ソース電極およびドレイン電極を形成し、第2の絶縁膜を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の長時間にわたる保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと、第2のトランジスタと、を含む複数のメモリセルと、増幅回路と、スイッチ素子と、を含む読み出し回路と、リフレッシュ制御回路と、を有し、第1のチャネル形成領域と第2のチャネル形成領域は、異なる材料を主成分として構成され、第1のゲート電極と、第2のソース電極および第2のドレイン電極の一方は電気的に接続され、第2のソース電極および第2のドレイン電極の他方と、増幅回路の入力端子の一は電気的に接続され、増幅回路の出力端子は、スイッチ素子を介して第2のソース電極および第2のドレイン電極の他方と接続され、スイッチ素子の導通状態または非導通状態は、リフレッシュ制御回路によって制御される半導体装置である。

(もっと読む)

半導体集積回路装置及び半導体集積回路装置の製造方法

【課題】メモリ及びメモリと周辺回路部との接続部を安定して形成することができ、安定してメモリを動作させることが可能な構成の半導体集積回路装置を提供する。

【解決手段】抵抗変化材料から成り、抵抗値により情報が記録される記憶層21と、記憶層21が複数個のメモリセルに共通して形成され、半導体基板1の上方に形成されたメモリ20と、制御回路を含む回路素子が半導体基板1に形成された、周辺回路部31と、周辺回路部31の回路素子と電気的に接続され、半導体基板1上の絶縁層12内に形成された、プラグ層11とを含み、メモリ20を構成する各層21,22が、プラグ層11上にまで延長して形成されてプラグ層11と電気的に接続された接続部25では金属元素が拡散しており、抵抗値が他の部分よりも低くなっている、半導体集積回路装置を構成する。

(もっと読む)

シングルゲートフィンFET及びその製造方法

【課題】新規なFinFET構造及びその製造方法を提供する。

【解決手段】シングルゲートフィンFET構造100は、2つの拡大された頭部、及び当該拡大された頭部と下層の超薄型ボディとを連結する2つの徐々に細くなる首部を有するアクティブフィン構造を含む。2つのソース/ドレイン領域102,104が、2つの拡大された頭部にそれぞれドープされる。絶縁領域26が、2つのソース/ドレイン領域の間に挿入される。溝分離構造24が、音叉形状のフィン構造の一方の側に配置される。片面サイドウォールゲート電極12bが、アクティブフィン構造における、溝分離構造とは反対側の垂直なサイドウォールに配置される。

(もっと読む)

不揮発性メモリ素子及びその製造方法、並びにそれを含むメモリ・モジュール及びシステム

【課題】不揮発性メモリ素子及びその製造方法、並びにそれを含むメモリ・モジュール及びシステムを提供する。

【解決手段】ストライエーション現象が改善された不揮発性メモリ素子であり、基板、基板から突設されるチャネル層、チャネル層を取り囲むゲート導電層、チャネル層とゲート導電層との間に位置するゲート絶縁層、及びチャネル層と離隔されつつゲート導電層の上下に位置する第1絶縁層を含み、ゲート絶縁層は、ゲート導電層と第1絶縁層との間に延びることを特徴とする不揮発性メモリ素子である。

(もっと読む)

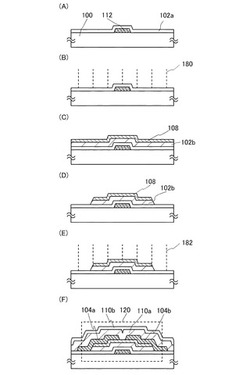

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜に酸素ドープ処理を行って、第1の絶縁膜に酸素原子を供給し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜に酸素ドープ処理を行って、第2の絶縁膜中に酸素原子を供給し、第2の絶縁膜上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面に第1の絶縁膜を形成し、第1の絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて第1の絶縁膜にエッチング処理を行うことにより、第2の絶縁膜を形成し、第2の絶縁膜を覆うように第1の導電膜を形成し、第1の導電膜および第2の絶縁膜に研磨処理を行うことにより、等しい厚さの第3の絶縁膜、ソース電極およびドレイン電極を形成し、第3の絶縁膜、ソース電極およびドレイン電極上に酸化物半導体膜を形成し、酸化物半導体膜上にゲート絶縁膜を形成し、ゲート絶縁膜上の第3の絶縁膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

限られたチャージ拡散を有するチャージトラップメモリ

【課題】隣接メモリセルへの漏洩電流を減らすフラッシュメモリ、特にチャージトラップメモリおよびそれを形成するプロセスフローの提供。

【解決手段】セルチャンネル620を含む半導体線が、STI領域120上に形成される。セルチャンネルは、トンネル酸化物層621、トラッピング誘電体層623、およびブロッキング誘電体層628を含む活性誘電体スタックで覆われる。結果として得られるセルチャンネルを分離するトレンチ625は、伝導層460で少なくとも部分的に充填され得る。活性誘電体層および/または伝導層の部分は、セルチャンネルの下、たとえば、セルチャンネルおよびSTI領域の間の界面695の下に位置し得る。そのような構成は、活性誘電体スタックおよび/または半導体層がセルチャンネルの下に位置しない構成に比べて、あるセルチャンネルから隣接セルチャンネルに拡散する荷電粒子670に対して経路長の増大をもたらす。

(もっと読む)

半導体装置

【課題】メモリ回路を含む半導体装置の低消費電力化を図ることを課題とする。

【解決手段】メモリ回路を含む半導体装置において、メモリ回路はワード線とビット線で規定される領域に設けられた半導体素子を有するメモリセルと半導体素子を有さないメモリセルを含み、該半導体素子には、酸化物半導体を用いて形成したオフ電流が極めて低いトランジスタを用いるため、読み出し精度が高まり、低電圧動作が可能となる。また、メモリセルは、ハイまたはローのいずれか一方のデータを記憶し、半導体素子を有するメモリセルは、前記データを構成するハイおよびローのうち、少ない方を記憶し、半導体素子を有さないメモリセルは、多い方を記憶する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。また、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、半導体装置の各メモリセルを構成する、酸化物半導体を用いたトランジスタを直列に接続することにより、隣り合うメモリセルにおいて、酸化物半導体を用いたトランジスタのソース電極またはドレイン電極をお互いに接続させることができ、メモリセルの占有面積を低減することができる。

(もっと読む)

半導体記憶素子、及び半導体記憶装置

【課題】 高効率に電荷を蓄積及び消去することができ、かつ蓄積した電荷を長時間保持することができる半導体記憶素子、及び半導体記憶装置を提供する

【解決手段】 半導体層19と、半導体層19上に設けられたトンネル絶縁膜18と、トンネル絶縁膜18上に設けられ、膜厚が0.9nm以上2.8nm以下であり、立方晶ハフニア粒子17を含む電荷蓄積膜16と、電荷蓄積膜16上に設けられたブロック絶縁膜15と、ブロック絶縁膜15上に設けられた制御電極13とを備えることを特徴とする半導体記憶素子。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、容量素子は、第2のトランジスタのソース電極またはドレイン電極と、ゲート絶縁層と、第2のトランジスタを覆う絶縁層上に設けられた容量素子用電極を含み、第2のトランジスタのゲート電極と、容量素子用電極とは、絶縁層を介して少なくとも一部が重畳して設けられる半導体装置を提供する。第2のトランジスタのゲート電極と、容量素子用電極とを、異なる層で形成することで、半導体装置の集積度を向上させることができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用トランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態とすることにより、書き込み用トランジスタのソース電極(またはドレイン電極)と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタとして、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

記憶装置、半導体装置

【課題】データの書き込み不良を抑えつつ、面積を小さく抑えることができる不揮発性の記憶装置、または当該不揮発性の記憶装置を用いた半導体装置の提供を目的の一とする。

【解決手段】不揮発性の記憶素子を有する第1の記憶部と、上記第1の記憶部へのデータの書き込みが正確に行われたかどうかを検証するベリファイ動作において、上記データを一時的に保存するための第2の記憶部(データバッファ)とを有する。そして、第2の記憶部が、記憶素子と、当該記憶素子における電荷の保持を制御するための、オフ電流またはリーク電流が極めて小さい絶縁ゲート電界効果型トランジスタとを有する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図ることを目的の一つとする。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】絶縁層と、絶縁層中に埋め込まれたソース電極、およびドレイン電極と、絶縁層表面、ソース電極表面、およびドレイン電極表面、の一部と接する酸化物半導体層と、酸化物半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さ(RMS)が1nm以下であり、絶縁層表面の一部とソース電極表面との高低差、または絶縁層表面の一部とドレイン電極表面との高低差は、5nm未満の半導体装置である。

(もっと読む)

半導体記憶装置、及びその製造方法

【課題】 高効率に電荷を蓄積及び消去することができ、かつ蓄積した電荷を長時間保持することができる半導体記憶装置、及びその製造方法を提供する。

【解決手段】 半導体記憶装置10は、半導体基板11と、半導体基板11内に離間して設けられたソース領域3及びドレイン領域2と、ソース領域3とドレイン領域2との間であって半導体基板11上に設けられたトンネル絶縁膜12と、トンネル絶縁膜12上に設けられ、酸化物クラスターを含む電荷蓄積膜13と、電荷蓄積膜13上に設けられたブロック絶縁膜14と、ブロック絶縁膜14上に設けられたゲート電極15とを備える。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の駆動方法

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを保存する半導体装置を提供する。

【解決手段】書き込みトランジスタのドレインと読み出しトランジスタのゲート、および、前記ドレインとキャパシタの一方の電極を接続した記憶セルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に、書き込みトランジスタのソースを書き込みビット線に、読み出しトランジスタのソースとドレインとを、それぞれ、読み出しビット線及びバイアス線に接続する。さらに、キャパシタの他方の電極を読み出しワード線に接続する。配線数を減らすために、読み出しワード線を、前記書き込みトランジスタのゲートが接続していない書き込みワード線で代用する、さらに読み出しビット線を書き込みビット線で代用する。

(もっと読む)

221 - 240 / 569

[ Back to top ]