Fターム[5F083JA60]の内容

Fターム[5F083JA60]に分類される特許

201 - 220 / 2,015

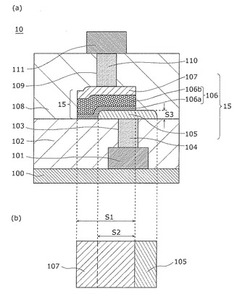

不揮発性記憶素子及びその製造方法並びに不揮発性記憶装置

【課題】不揮発性記憶素子の初期化電圧のばらつきの発生を抑えつつ、従来に比べて初期化電圧の低減を図ることができる抵抗変化型の不揮発性記憶素子を提供する。

【解決手段】第1の層間絶縁層102、下部電極105、上部電極107及び抵抗変化領域106を備え、抵抗変化領域106は積層された第1の抵抗変化領域106bと第2の抵抗変化領域106aを有し、第1の抵抗変化領域106bは第1の遷移金属酸化物で構成され、第2の抵抗変化領域106aは第2の遷移金属酸化物で構成され、第2の遷移金属酸化物の酸素不足度は第1の遷移金属酸化物の酸素不足度より小さく、抵抗変化領域106の上面は上部電極107と接し、抵抗変化領域106の底面は下部電極105及び第1の層間絶縁層102と接し、抵抗変化領域106の底面と下部電極105の接する面の面積は抵抗変化領域106の上面と上部電極107の接する面の面積より小さい。

(もっと読む)

不揮発性抵抗変化素子

【課題】抵抗を可逆的に変化させことを可能としつつ、データ保持特性を向上させる不揮発性抵抗変化素子を提供する。

【解決手段】第1電極1と、第2電極3と、可変抵抗層2とを備え、第2電極3は、Al元素が添加された1B族元素を有し、可変抵抗層2は、第1電極1と第2電極3との間に配置され、シリコン元素を有する。可変抵抗層2は非晶質シリコン層であってもよいし、多結晶シリコン層であってもよいし、単結晶シリコン層であってもよい。第1電極1は不純物ドープシリコンおよびTi、Ni、Co、Fe、Cr、Cu、W、Hf、Ta、Pt、Ru、ZrまたはIrや、その窒化物あるいは炭化物あるいはカルコゲナイド材料などを用いることができる。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート

電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第

2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジ

スタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトラ

ンジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

混合原子価導電性酸化物を用いたメモリ

【課題】混合原子価導電性酸化物を用いたメモリを提供する。

【解決手段】酸化されていない状態で導電性を有し、酸素欠乏状態で導電性が下がる混合原子価導電性酸化物酸素リザーバ635と、酸素に対する電解質であり、酸素イオンの移動を引き起こすのに有効な電場を促進する電解質トンネル障壁505と、を備える。

(もっと読む)

半導体不揮発性記憶装置およびその製造方法

【課題】高い信頼性で書き込み・消去・読み出しが可能な低コストの半導体不揮発性記憶装置およびその製造方法を提供する。

【解決手段】実施形態の半導体不揮発性記憶装置は、基体Sと、第1の電極2と、機能膜10と、第2の電極50と、を持つ。前記第1の電極2は、前記基体S上に設けられる。前記機能膜10は、前記第1の電極2上に成膜されて記憶媒体をなす。前記第2の電極50は、上面に凸の曲面を有するように、前記機能膜10上または前記機能膜10内に設けられる。

(もっと読む)

非揮発性メモリ装置及びセンシング方法

【課題】抵抗変化を利用したマルチレベルのデータをセンシングする非揮発性メモリ装置において、読出し動作の回数を減らし、読出し動作の制御に係わる回路の面積を縮小する。

【解決手段】非揮発性メモリ装置は、1つ以上の単位セルを含んでデータの読出し又は書込みが行なわれるセルアレイと、単位セルに格納されたデータに対応するセンシング電圧SAIと基準電圧REFを比較及び増幅して出力し、ビットラインがプリチャージされた以後にセンシングイネーブル信号SENの活性化区間で、単位セルの抵抗値に応じてセンシング電圧がディスチャージされる時間の差を測定し、データをセンシングするセンシング部100とを含む。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供すること。また、安定した電気的特性が付与された、信頼性の高い半導体装置を提供すること。

【解決手段】絶縁層に凸状構造体を形成し、該凸状構造体に接して酸化物半導体層のチャネル形成領域を設けることで、チャネル形成領域を3次元方向(基板垂直方向)に延長させる。これによって、トランジスタの微細化を達成しつつ、実効的なチャネル長を延長させることができる。また、凸状構造体の上面と側面とが交わる上端コーナー部に曲面を形成し、酸化物半導体層が当該曲面に垂直なc軸を有する結晶を含むように形成する。これによって、酸化物半導体層の可視光や紫外光の照射による電気的特性の変化を抑制することができる。

(もっと読む)

酸化物材料および半導体装置

【課題】トランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。また、このような半導体装置を実現する酸化物材料を提供する。

【解決手段】それぞれ、c軸配向し、ab面、上面または被形成面に垂直な方向から見て少なくとも三角形状または六角形状の原子配列を有し、c軸においては、金属原子が層状または金属原子と酸素原子とが層状に配列しており、In2SnZn2O7(ZnO)m(mは0または自然数。)で表される、ab面(または上面または被形成面)においては、a軸またはb軸の向きが異なる二種以上の結晶部分を含む酸化物膜を用いる。

(もっと読む)

半導体装置

【課題】不揮発性であって、作製が簡単であり、追記が可能な記憶回路を有する半導体装置の提供を課題とする。

【解決手段】本発明の半導体装置は、複数のトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記複数のトランジスタのうちの1つの上に設けられた記憶素子及びアンテナとして機能する導電層とを有し、前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、アンテナとして機能する前記導電層と前記複数のトランジスタのソース配線又はドレイン配線として機能する導電層とは、同じ層上に設けられていることを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】絶縁層に凸状部またはトレンチ(溝部)を形成し、該凸状部またはトレンチに接して半導体層のチャネル形成領域を設けることで、チャネル形成領域を基板垂直方向に延長させる。これによって、トランジスタの微細化を達成しつつ、実効的なチャネル長を延長させることができる。また、半導体層成膜前に、半導体層が接する凸状部またはトレンチの上端コーナー部に、R加工処理を行うことで、薄膜の半導体層を被覆性良く成膜する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板の転移を防止しつつ、絶縁膜の埋め込み性を確保するとともに、エッチング耐性を向上させる。

【解決手段】シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素を含有させ、塗布法などの方法にてトレンチ6内に埋め込まれるようにしてシリコン含有無機ポリマー膜8をライナー膜7上に形成し、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜8の酸化処理を行うことにより、シリコン含有無機ポリマー膜8をシリコン酸化膜9に変化させる。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2

の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上

に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を

有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第

3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のド

ーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

半導体基板、半導体装置及びその製造方法

【課題】キャリア移動度(チャネル移動度)を増加させて、オン電流を増加させること。

【解決手段】トランジスタを形成するための半導体基板(10)は、主面(11a)を持つシリコン基板(11)と、このシリコン基板(11)の主面(11a)上に形成された歪緩和SiGe層(12)と、この歪緩和SiGe層(12)上に形成された歪Si層(13)と、を含む。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接する、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタを有し、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第1の酸化絶縁膜上に位置する。

(もっと読む)

記憶素子および信号処理回路

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路を提供する。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、アモルファスシリコン、ポリシリコン、微結晶シリコン、あるいは酸化物半導体等の化合物半導体をチャネル形成領域に含み、そのチャネル長が最小加工線幅の10倍以上あるいは、1μm以上であるトランジスタを用いる。上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

抵抗変化型不揮発性メモリセルおよび抵抗変化型不揮発性記憶装置

【課題】電流制御素子が破壊されにくい、抵抗変化型不揮発性メモリセルおよび抵抗変化型不揮発性記憶装置を提供する。

【解決手段】極性の異なる電気的信号を印加することにより抵抗値の異なる複数の抵抗状態の間を可逆的に遷移する抵抗変化素子103と、抵抗変化素子103に直列に接続し、所定の印加電圧の範囲において印加電圧の絶対値が大きくなるにしたがい電圧電流曲線の傾きが大きくなる非線形の電圧電流特性を有する電流制御素子104と、層間絶縁層108、109、110を貫通するホールの内部に形成され、抵抗変化素子103もしくは電流制御素子104の少なくとも一方に接触し、かつ、負荷抵抗部131A、131B、131Cを有する、プラグ105,106,107と、を備える。

(もっと読む)

不揮発性半導体記憶装置および同装置の製造方法

【課題】高抵抗状態と低抵抗状態の抵抗値の比を大きくする素子の構成及び方法並びに素子間ばらつきの低減方法を提供する。

【解決手段】ペロブスカイト酸化物の一面に特定金属が設けられるとともに、前記ペロブスカイト酸化物から前記金属へ当該ペロブスカイト酸化物の酸素が移動することで当該金属の酸化と当該ペロブスカイト酸化物の還元が進行するために必要な活性化エネルギー以上のエネルギーが与えられるように加熱することによって得られる酸素欠乏層領域が前記ペロブスカイト酸化物の前記金属と接触した近傍の領域に存在するようになし、前記金属よりなる一方の電極と前記酸素欠乏層を介して対となる他方の電極間の電圧−電流特性のヒステリシス特性を利用することを特徴とする不揮発性半導体記憶装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】 層間絶縁膜をCMP法で研磨、平坦化する際、MOS型トランジスタのチャネル領域に応力を与えるためにゲート電極を覆うように形成される応力ライナー膜が研磨されて、トランジスタ特性の変動やバラツキが発生しないようにする。

【解決手段】 第1活性領域(例えばPチャネルトランジスタ形成領域)上のゲート電極(シリコン膜14と金属シリサイド膜15との積層膜)上には第1応力膜(圧縮応力ライナー膜)16のみを形成し、第2活性領域(例えばNチャネルトランジスタ領域)上のゲート電極上には第2応力膜(引っ張り応力ライナー膜)18のみを形成する。一方、素子分離10上のゲート電極上には第1および第2応力膜16、18の積層膜を形成する。層間絶縁膜20のCMP法による研磨は、素子分離10上の第2応力膜18の露出後に停止する。

(もっと読む)

201 - 220 / 2,015

[ Back to top ]