Fターム[5F083KA18]の内容

Fターム[5F083KA18]に分類される特許

1 - 20 / 50

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてバンドギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

(もっと読む)

不揮発性メモリ装置

【課題】 パストランジスタ間の空間確保が可能な不揮発性メモリ装置を提供する

【解決手段】 不揮発性メモリ装置100が備える行デコーダ120は、パストランジスタ部123_L、123_Rを含む。パストランジスタ部123_L、123_Rは、メモリブロック110の左右に配列される。ブロック選択信号BLKWL1によって共通ゲートを形成するパストランジスタ端Pass TR 0とパストランジスタ端Pass TR 8とは、選択的に活性化される第1駆動信号ラインSI1及び第2駆動信号ラインSI2によって独立して駆動される。互に異なるブロック選択信号BLKWLによって駆動されるパストランジスタは、1つの活性領域の上に形成され得る。これにより、1つの活性領域の上に2つのパストランジスタを形成する場合、パストランジスタ部123_L、123_Rのチャンネル方向の大きさを減らすことができる。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】良好な伝送性能と小さい配置面積を両立可能なデータバスを備える半導体装置を提供する。

【解決手段】本発明の半導体装置は、配線層M1、M2と、複数のデータ入出力端子と、N本のデータ線(DU、DL)を含むデータバスとを備え、N本のデータ線は所定の配線長の長短に応じた2種類のデータ線群を含む。配線層M1、M2にはデータ線(DL、DU)の各々に隣接する複数のシールド線(Sa、Sb、Sc)が配置され、各データ線(DL、DU)は、配線層M1、M2の積層方向で互いに重ならない位置に配置される。このような配線構造により、各データ線(DL、DU)の間のカップリング容量を抑え、データバスのクロストークを防止することができる。

(もっと読む)

半導体装置の製造方法

【課題】的確かつ効果的にパターンを形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地領域上に、第1のピッチで配置された複数のダミーラインパターン21cを形成する工程と、ダミーラインパターン21cの両長側面に形成された所定マスク部分を有し、ダミーラインパターンを囲む閉ループ形状のマスクパターン25cを形成する工程と、ダミーラインパターン21cを除去する工程と、マスクパターン25cの両端部分を除去して所定マスク部分を残す工程と、所定マスク部分をマスクとして用いて下地領域をエッチングする工程とを備える。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】不揮発性記憶装置およびその製造方法に関し、抵抗変化材料を利用したメモリの信頼性の向上を実現する。

【解決手段】積半導体素子を形成する基板の上方に、第1方向に延伸するように複数の金属配線層2を設け、金属配線層2のさら上方に、前記第1方向に直交する第2方向に延伸するように複数の金属配線層3を設ける。また、金属配線層2と金属配線層3とが交差する空間のそれぞれにメモリセルを設ける。前記メモリセルは、選択素子と相変化材料層7とが並列接続された構成とする。ここで、前記選択素子の前記第1方向の寸法が、相変化材料層7の前記第1方向の寸法よりも大きくなるように加工する。

(もっと読む)

半導体装置及びその製造方法

【課題】デバイス特性及びプロセスのばらつきを低減できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板10と、下部ゲート層BGと、積層体と、ダミー電極層DWLと、絶縁膜30と、チャネルボディ20,45とを備えた。下部ゲート層BGは、基板10上に設けられた。積層体は、下部ゲート層BG上にそれぞれ交互に積層された複数の絶縁層と複数の電極層WLとを有する。ダミー電極層DWLは、下部ゲート層BGと積層体との間に設けられ、電極層WLと同じ材料からなり、各々の電極層WLよりも厚い。絶縁膜30は、積層体及びダミー電極層を貫通して形成されたホールMHの側壁に設けられた電荷蓄積膜を含む。チャネルボディ20,45は、ホールMH内における絶縁膜30の内側に設けられた。

(もっと読む)

半導体装置

【課題】不揮発性メモリと容量素子を有し、性能を向上させる半導体装置を提供する。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MG6nとp型ウエルPW1との間および制御ゲート電極CG4nとメモリゲート電極MG6nとの間には、内部に電荷蓄積層5bを有する絶縁膜5が形成されている。この絶縁膜5は、酸化シリコン膜5aと、その上に形成された窒化シリコン膜5bと、その上に形成された酸化シリコン膜5cと、その上に形成されかつ酸化シリコン膜5cよりも薄い絶縁膜5dとの積層膜からなる。この絶縁膜5dは、ポリシリコンからなるメモリゲート電極MG6nに接している。絶縁膜5dは、Hf,Zr,Al,Ta,Laのうちの少なくとも1種を含む金属化合物により形成されているため、フェルミピニングを生じることができ、誘電率が高い。

(もっと読む)

不揮発性半導体記憶装置

【課題】集積度が高い不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置において、それぞれ複数の絶縁膜及び電極膜14が交互に積層された積層体と、この積層体内に埋設され、絶縁膜及び電極膜14の積層方向に延びるシリコンピラー31と、電極膜14とシリコンピラー31との間に設けられた電荷蓄積層26と、を設ける。そして、電極膜14を、それぞれが電荷蓄積層26を挟んでシリコンピラー31に対向する複数の制御ゲート電極CGa及びCGbに分割する。

(もっと読む)

半導体装置の製造方法

【課題】レジスト膜のスリミング時にその膜厚の消費を抑制する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基体11上に複数の絶縁層25と複数の導電層WLとを交互に積層して積層体を形成する工程と、積層体上にレジスト膜50を形成する工程と、レジスト膜50をマスクにして絶縁層25及び導電層WLをプラズマエッチングする工程と、ホウ素、リン及びヒ素の少なくとも1つを含むガスを用いたプラズマ処理により、レジスト膜50の上面に、ホウ素、リン及びヒ素の少なくとも1つを含む硬化層51を形成する工程と、レジスト膜50の上面に硬化層51が形成された状態で、酸素を含むガスを用いたプラズマ処理によりレジスト膜50の平面サイズをスリミングする工程と、を備えた。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の駆動方法

【課題】隣接セル間の干渉の影響を抑制し、データリテンション特性の向上を図ること。

【解決手段】本発明は、メモリ部と、制御部と、を備え、制御部は、複数の記憶領域MEの全てに消去の情報を設定し、メモリセルトランジスタTrの全てについて消去の閾値に設定した後、記憶領域MEにn(nは2以上の整数)値の情報を書き込み、記憶領域MEに設けられたメモリセルトランジスタTrをn値の情報に応じた閾値に設定した状態で、情報の書き込み済みの記憶領域MEに隣接する少なくとも1つの書き込み前の記憶領域MEの情報が、メモリセルトランジスタTrの閾値として、消去の閾値よりも、n値の情報に応じた閾値に近い値になるよう制御する。

(もっと読む)

半導体装置

【課題】チップ面積を縮小しつつ、高信頼性を実現する半導体装置を提供する。

【解決手段】半導体装置は、第1、第2配線S1,S2を有する第1回路部210と、第3、第4配線S3、S4を有する第2回路部220と、それらの間に設けられ、第1回路部210から第2回路部220に向かう方向に直交する方向に沿って隣接する第1、第2トランジスタTR1、TR2を有する中間部230と、を備え、第1トランジスタTR1の一方の拡散層DA1の第1接続領CA1内の高濃度領域CAI1は第1配線S1に、他方の拡散層DB1は第3配線S3に接続される。第1接続領域CA1とゲートG01との距離は、第2接続領域CA2とゲートG02との距離よりも長い。第1トランジスタTR1の一方の拡散層DA1の第1接続領域CA1とゲートG01との間には、第1接続領域CA1よりも幅が狭い延在領域EA1が設けられる。

(もっと読む)

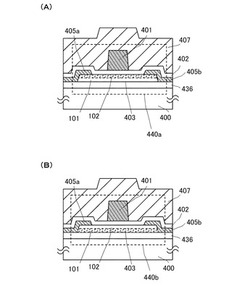

半導体装置及びその製造方法

【課題】強誘電体キャパシタの下部電極材料の選択自由度が高く、ビア工程の少ない半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板101上に形成されたスイッチングトランジスタ301A,301Bと、拡散層121と、トランジスタ301上に形成された層間絶縁膜131と、下部電極211、強誘電体膜212、及び上部電極213を含む強誘電体キャパシタ201A,201Bと、上部電極213の上方に形成された配線層141と、上部電極213と配線層141とを電気的に導通させる第1のプラグTWと、拡散層121と配線層141とを電気的に導通させる第2のプラグV1A,V1Bと、下部電極211の側方に配置されており、下部電極211と拡散層121とを電気的に導通させる第3のプラグCSFとを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】動作の信頼性が高い不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置にメモリセルアレイ及び制御回路を設け、メモリセルアレイには、それぞれ複数の絶縁膜及び電極膜が交互に積層された積層体を設け、この積層体に積層方向に延びる貫通ホールを形成し、その内部にシリコンピラーを埋設し、電極膜とシリコンピラーとの間に電荷蓄積膜を設ける。これにより、電極膜とシリコンピラーとの交差部分毎にメモリセルが形成される。そして、制御回路は、フォーマット時に、全てのメモリセルに値「0」を書き込み、全てのメモリセルに対して値「0」を消去する動作を行い、積層体の最上段に形成されたメモリセルに記憶された値を読み出し、値「0」が読み出されたメモリセルについては、消去動作が不良であったと判定し、以後不使用とする。

(もっと読む)

不揮発性半導体記憶装置

【課題】集積度が高まった場合においても、読み出し電流の低下を抑制する3次元構造の半導体記憶装置を提供する。

【解決手段】メモリストリングMSの各々は、2本の柱状部CLmn、及びそれらの下端を連結する連結部JPmnを有するボディ半導体層SCmnを有する。ビット線BL、ソース線SLは、カラム方向を長手方向として交互に形成され、連結部JPmnは、カラム方向を長手方向として形成される。メモリストリングMSは、基板上においてジグザグ状に形成され、1本の柱状部CLmnに沿って形成される4個のメモリトランジスタMTrに接続されるワード線WLを共有する。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】安定した動作を実行可能な不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】メモリストリングMSは、基板上に積層方向に延びる柱状部45Aを含むU字状半導体層45と、柱状部45Aを取り囲むように形成された電荷蓄積層44bと、電荷蓄積層44bを取り囲むように積層されたワード線導電層41a〜41dとを備える。ドレイン側選択トランジスタSDTrは、柱状部45Aの上面に接して積層方向に延びるドレイン側柱状半導体層57と、ドレイン側柱状半導体層57を取り囲むように形成された電荷蓄積層55bと、電荷蓄積層55bを取り囲むように形成されたドレイン側導電層51とを備える。電荷蓄積層55bは、ドレイン側導電層51の下層からドレイン側導電層51の上端近傍まで形成され、且つその上端近傍よりも上層には形成されていない。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】セルトランジスタの微細化に適した構造の選択トランジスタを有するNAND型不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置は、基板101と、基板内に形成された拡散層121により互いに直列接続されている複数のセルトランジスタ141と、複数のセルトランジスタ141と直列接続されている選択トランジスタ142とを備え、選択トランジスタ142は、第1の絶縁膜161と、第1の電極層162A、B、第2の絶縁膜163A,B、及び第2の電極層164A,Bを含む第1及び第2の積層体171A,Bと、第1の積層体と第2の積層体との間に形成され、第1の積層体171Aの第1及び第2の電極層と第2の積層体171Bの第1及び第2の電極層とを電気的に接続する第3の電極層181とを備え、第3の電極層181は、第1及び第2の積層体171A,Bの上面よりも上方に突出した突出部191を有する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】シリコンをエピタキシャル成長させて得られた単結晶シリコン層の結晶欠陥の部分にメモリセルを形成することなくメモリセルの積層を実現する不揮発性半導体記憶装置を提供する。

【解決手段】層間絶縁膜16上にシリコンをエピタキシャル成長させて得られた単結晶シリコン層200、204の結晶欠陥26bの部分にソース線コンタクトホールを形成する。これによって、結晶欠陥26bの部分に、接合リークにより特性の劣化したメモリセルを形成することなく、メモリセルを二層以上積層することができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】正確な読み出しを実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリトランジスタMTr1〜8が直列に接続された複数のメモリストリングMSと、メモリストリングMSの一端に一端を接続されたドレイン選択トランジスタSDTrと、複数のドレイン側選択トランジスタSDTrの他端に共通接続されたローカルビット線LBLと、ローカルビット線LBLに一端を接続されたスイッチ回路SWと、複数のスイッチ回路SWの他端に共通接続されたグローバルビット線GBLとを備える。メモリストリングMSは、柱状部を含むU字状半導体層と、柱状部の側面を取り囲むように形成された電荷蓄積層と、電荷蓄積層を取り囲むように形成されたワード線導電層とを備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高集積化されたスプリットゲート型不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板1の表面に第1の柱状凸部2aと第2の柱状凸部2bが離間して形成され、第1、第2の柱状凸部2a,2bは、周辺部と先端部とにソースドレイン3,8の一方と他方とが形成され、周辺部と先端部との間の側壁の表面に、電荷蓄積膜4とメモリゲート線5とが積層された第1積層構造と、ゲート酸化膜6と制御ゲート線7とが積層された第2積層構造と、が形成されたスプリットゲート型の不揮発性メモリセルを、それぞれ含み、第1積層構造が第1、第2の柱状凸部2a,2bの間にも形成され、それによって、第1の柱状凸部2aと第2の柱状凸部2bとで、メモリゲート線5が共通に接続されている

(もっと読む)

半導体装置の製造方法

【課題】高アスペクト比のコンタクトホールを容易な加工で形成可能な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、基板10上に第1の加工層を形成する工程と、第1の加工層に第1のコンタクトホールCS1を形成する工程と、第1のコンタクトホールCS1内に犠牲膜42aを埋め込む工程と、犠牲膜42aが埋め込まれた第1のコンタクトホールCS1上に第2の加工層44を形成する工程と、犠牲膜42a上の第2の加工層44に犠牲膜42aに達する第2のコンタクトホールCS2を形成する工程と、第2のコンタクトホールCS2を通じて第1のコンタクトホールCS1内から犠牲膜42aを除去し、第1のコンタクトホールCS1と第2のコンタクトホールCS2とを連通させる工程と、を備えた。

(もっと読む)

1 - 20 / 50

[ Back to top ]