Fターム[5F083KA20]の内容

Fターム[5F083KA20]に分類される特許

101 - 120 / 150

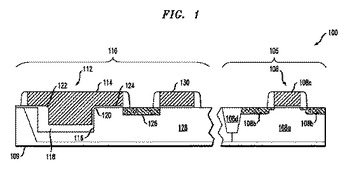

ランダム・アクセス・メモリ・デバイスのトレンチ・キャパシタ漏洩電流を低減する方法

本発明は、一態様では、半導体デバイスを製造する方法を提供する。この方法は、半導体基板(109)のダイナミック・ランダム・メモリ領域(DRAM)(110)内にトレンチ分離構造(118)を形成すること、ならびにトレンチ分離構造(118)の上に、トレンチ分離構造(118)の一部分を露出するようにエッチング・マスクをパターニングすることを含む。露出したトレンチ分離構造(118)の一部分を除去してその中に、半導体基板によって形成された第1の角部と、トレンチ分離構造によって形成された第2の角部とを含むゲート・トレンチ(116)を形成する。エッチング・マスクをDRAM領域(110)から除去し、ゲート・トレンチの少なくとも第1の角部に丸みをつけて、丸みをつけた角部(120)を形成する。この後に、ゲート・トレンチ(116)の側壁の上、第1の丸みをつけた角部(120)の上、およびゲート・トレンチ(116)に隣接する半導体基板(109)の上の酸化物層(124)の形成を続ける。トレンチ(116)をゲート材料で充填する。  (もっと読む)

(もっと読む)

半導体装置

【課題】横方向および斜め上方向からの光の進入を低減でき、特性の変動が抑制されたフローティングゲート電極を有する不揮発性メモリの半導体装置を提供する。

【解決手段】メモリセルの周囲に設けられた第1遮光壁50により画定された第1被遮光領域10Aと、メモリセルの周囲に設けられた第2遮光壁により画定された第2被遮光領域10A´と、第1遮光壁50に設けられた第1開孔52と、第2遮光壁に設けられ第1開孔52と対向して位置する第2開孔52´と、メモリセルと接続され、第1開孔52から第1被遮光領域10Aの外側に引き出された第1配線層24a,24b,24cと、メモリセルと接続され、第2開孔52´から第2被遮光領域10A´の外側に引き出された第2配線層24a´,24b´,24c´と、少なくとも、第1被遮光領域10Aと第2被遮光領域10A´とに挟まれた領域の上方に設けられた遮光膜と、を含む。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】素子の微細化によっても、機械的強度に優れ、微細加工が容易であり、かつ十分な記憶容量を確保したキャパシタを有する半導体装置を提供する。

【解決手段】柱状の下部電極(101、201、301)、容量絶縁膜(102、202、302)及び上部電極(103、203、303)を有するキャパシタが層間膜を介して複数積層されており、下層キャパシタの下部電極(101)上端から上層キャパシタの下部電極(201)下端を接続するコンタクトプラグ(104)と、各層キャパシタの上部電極を接続するコンタクトプラグ(22)を有する半導体記憶装置。

(もっと読む)

局部エッチング阻止物質層を有するビットラインスタッド上のビットラインランディングパッドと非境界コンタクトとを有する半導体素子及びその製造方法

【課題】局部エッチング阻止物質層を設けたビットラインランディングパッドと非境界コンタクトとを有する、比較的密集された構造の半導体素子及びその製造方法を提供する。

【解決手段】層間コンタクトスタッド220a、220bを形成し、層間コンタクトスタッド220b上には導電性ライン222を設ける。これらの上に第1エッチング阻止物質層224a、第2エッチング阻止物質層224bを選択的に設ける。導電性ライン222には側壁絶縁膜226を設ける。第1エッチング阻止物質層と側壁絶縁膜とはエッチング選択比の異なる物質を用いる。これらのエッチング阻止物質層は、続く製造工程中に不純物のガス抜けを許す、とともに上部のコンタクトホール229a、229bを形成する際に整列ターゲットとしての役割をする。

(もっと読む)

半導体集積回路装置

【課題】多層信号配線の特性の均一化を図った半導体集積回路装置を提供する。

【解決手段】複数の拡散層が形成された半導体基板と、前記半導体基板に積層されて、前記各拡散層に対してビアコンタクトを介して接続される複数層の信号配線とを備え、第1の信号配線とそれより上層の第2の信号配線について、第2の信号配線を前記拡散層に接続するビアコンタクトの数が第1の信号配線のそれより多く設定されている。

(もっと読む)

NORフラッシュデバイス及びその製造方法

【課題】本発明は、NORフラッシュデバイス及びその製造方法を提供する。

【解決手段】バックエンドオブライン(BEOL)構造を有するNORフラッシュデバイスにおいて、BEOL構造は導電領域を有する基板と、基板上に形成された第1層間絶縁膜と、導電領域に形成される第1金属ラインと、該第1金属ラインと第1層間絶縁膜を覆う第2層間絶縁膜と、第2層間絶縁膜を貫通する第1コンタクト及び第1コンタクトを通じて第1金属ラインと連結される第2金属ラインを具備して、第1コンタクト、第1及び第2金属ラインのうちで少なくとも一つは銅であり、第1及び第2層間絶縁膜のうちで少なくとも一つは、低誘電物質を含む。

(もっと読む)

半導体装置の製造方法

【課題】

大型ウエハにおいても均一な丸め込み酸化が行なえ、かつ増加する工程が過度の負担にならない半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、シリコン基板の表裏両面上方に窒化シリコン膜、その上にTEOS酸化シリコン膜をCVDで堆積する工程と、表面側TEOS酸化シリコン膜を除去する工程と、TEOS酸化シリコン膜を脱ガスアニールする工程と、表面側窒化シリコン膜をエッチングマスクとしてシリコン基板に素子分離溝をエッチングする工程と、1000℃以上の温度の丸め込み酸化をバッチ処理で行なう工程と、HDP酸化シリコン膜で素子分離溝を埋め込む工程と、を含む。

(もっと読む)

半導体装置

【課題】トランジスタの主電極領域上のコンタクト接続不良並びに制御電極上のコンタクト接続不良を防止することができる半導体装置を提供する。

【解決手段】半導体装置(強誘電体記憶装置1)において、トランジスタ3と、強誘電体キャパシタ8とを備える。トランジスタ3の制御電極32と強誘電体キャパシタ8を被覆するバリア膜(水素バリア膜)10との間の層間絶縁膜4において、制御電極32上の第3のプラグ5(3)の上面の基板2からの高さが、第2の主電極領域34(2)上の第2のプラグ5(2)の上面の基板2からの高さに比べて高く設定されている。

(もっと読む)

半導体装置の作製方法

【課題】大面積基板に、高性能な半導体素子、及び集積回路を高スループットで生産性よく作製することを目的とする。

【解決手段】単結晶半導体基板(ボンドウエハー)より単結晶半導体膜を転置する際、単結晶半導体基板を選択的にエッチング(溝加工ともいう)し、作製する半導体素子の大きさに複数に分割された複数の単結晶半導体層を、異種基板(ベース基板)に転置する。従って、ベース基板には、複数の島状の単結晶半導体層(SOI層)を形成することができる。

(もっと読む)

半導体装置

【課題】半導体記憶装置に係り、特に、高集積化されたDRAMを、少ない工程数で、且つ微細なセル面積で実現できる半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体基板10に形成されたメモリセルトランジスタと、メモリセルトランジスタのゲート電極20の上面及び側面を覆う絶縁膜42と、ソース拡散層24上に開口したスルーホール40と、ドレイン拡散層26上に開口したスルーホール38とが形成された層間絶縁膜36と、スルーホール40内壁及び底部に形成され、ソース拡散24層に接続されたキャパシタ蓄積電極46と、キャパシタ蓄積電極46を覆うキャパシタ誘電体膜48と、キャパシタ誘電体膜48を覆うキャパシタ対向電極54とを有するキャパシタと、スルーホール38の内壁及び底部に形成され、ドレイン拡散層と接続されたコンタクト用導電膜44とにより構成する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】書き込み時の消費電力が小さく、読み出し専用の記憶装置のメモリ素子に用いられるアンチヒューズを提供する。

【解決手段】アンチヒューズは、第1導電層11と、第1導電層11上に非晶質シリコン膜13と絶縁膜14とを交互に積層した2層以上の多層膜20と、多層膜20上に第2導電層12を有する。第1導電層11と第2導電層12の間に電圧を印加して、多層膜20の抵抗を低下させることで、メモリ素子にデータを書き込む。第1導電層11と第2導電層12の間に非晶質シリコン13よりも抵抗が高い絶縁膜14を形成することで、書き込み時にアンチヒューズに流れる電流が低減される。

(もっと読む)

半導体装置の製造方法

【課題】ボンディングパッドやヒューズ窓の形成に際して、MISFETの特性の劣化を抑制する。

【解決手段】半導体装置の製造方法は、半導体基板の上部に、MISFETに接続された配線15を形成するステップと、配線15上にパッシベーション膜16を形成するステップと、パッシベーション膜16をエッチングし、配線15の所定部分を露出する開口18を形成するステップと、開口18から露出した配線15を含む半導体基板を、H2ガス雰囲気中でアニールするステップと、を有する。配線15は、順次に積層された、バリアメタル層12、メタル層13、及び、キャップメタル層14を含む。

(もっと読む)

半導体記憶装置

【課題】通常のCMOSプロセスにおいてDRAMを作製でき、低い製造コストで製造可能なDRAMの混載した半導体記憶装置を提供する。

【解決手段】半導体基板上に形成された第1及び第2のトランジスタT1、T2と、セルデータ電荷を保持するための2つのノードSNt、SNcと、周囲に形成されたシールド電極により構成される1ビットのメモリセル11領域であって、各々のノードSNt、SNcは第1、第2のトランジスタT1、T2のドレインに接続されており、第1及び第2のトランジスタT1、T2のゲートはともに同一のワード線WL0に接続されており、第1及び第2のトランジスタT1、T2のソースは第1、第2のビット線BLt0、BLc0に接続され、第1及び第2のビット線BLt0、BLc0は、同一のセンスアンプSA12に接続され、1ビットのメモリセル領域が2次元的にアレイ状に形成される。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】ワード線電極へのコンタクトの加工工程を短縮してコスト削減を可能とする、メモリセルを三次元的に積層した不揮発性半導体記憶装置を提供する。

【解決手段】基板と、前記基板に対して垂直に形成された柱状半導体と、前記柱状半導体の周りに形成された第1の絶縁膜と、前記第1の絶縁膜の周りに形成された電荷蓄積層と、前記電荷蓄積層の周りに形成された第2の絶縁膜と、前記第2の絶縁膜の周りに形成された導電体層7とを有する電気的に書き換え可能なメモリセルが直列に接続されたメモリストリングスと、前記導電体層7と駆動回路3とを接続するコンタクトとを備え、前記導電体層7の端部は前記基板に対して上方に折り曲げられ、且つ折り曲げられた前記導電体層7の各端面上に前記コンタクトが設けられていることを特徴とする不揮発性半導体記憶装置1を構成する。

(もっと読む)

クロスバーメモリシステム及びクロスバーメモリシステムのクロスバーメモリ接合部に対して書込み及び読出しを行なう方法

本発明の種々の実施形態は、クロスバーメモリシステム、並びに係るシステムに情報を書き込む方法及び係るシステムに格納されている情報を読み出す方法に関する。本発明の一実施形態では、クロスバーメモリシステム(1300)は、第1の層のマイクロスケール信号線(808)と、第2の層のマイクロスケール信号線(810)と、それぞれが第1の層の各マイクロスケール信号線(808)に重なるように構成される、第1の層のナノワイヤ(804)と、それぞれが第2の層の各マイクロスケール信号線(810)に重なり、且つ第1の層の各ナノワイヤ(804)に重なるように構成される、第2の層のナノワイヤ(806)とを備える。そのクロスバーメモリシステムは、第1の層のナノワイヤ(804)を第1の層のマイクロスケール信号線(808)に選択的に接続し、且つ第2の層のナノワイヤ(806)を第2の層のマイクロスケール信号線(810)に選択的に接続するように構成される非線形トンネル抵抗器(1526,1528)を含む。また、そのクロスバーメモリシステム(1300)は、各クロスバー交差部において第1の層の各ナノワイヤ(2008)を第2の層の各ナノワイヤ(2012)に接続するように構成される非線形トンネルヒステリシス抵抗器(1318)も含む。 (もっと読む)

NANDメモリーアレイおよびNANDフラッシュアレイ

【課題】ストラップされたストリング選択ラインを持つフラッシュメモリー装置を提供する。

【解決手段】NANDメモリーアレイは、第1選択ラインに連結された第1選択トランジスターと、第2選択ラインに連結された第2選択トランジスターと、ワードライン等に各々連結され、第1及び第2選択トランジスターの間に直列に連結されたメモリーセル等と、そして、第1選択ラインに電気的に連結されたストラッピングラインを含む。

(もっと読む)

ReRAM

【課題】ReRAMに関し、電極(ビア)及びReRAM素子の配置構造に簡単な改変を加え、微細化すべきメモリセル選択トランジスタアレイには所要の加工ルールを適用して加工し、且つ、ReRAM素子には別の加工ルールを適用して加工することを可能にし、ReRAM素子の間隔がルール違反にならないようにする。

【解決手段】ワード線WL(ゲート)で代表されるメモリセル選択トランジスタ上に形成された多層メタル配線層M1・・・・と、多層メタル配線層M1・・・・の上層に在って且つ素子ピッチPR が前記多層メタル配線層M1・・・・の下層に在る配線のピッチPL に比較して広いピッチで形成されたReRAM素子7を備える。

(もっと読む)

半導体集積回路装置の製造方法および半導体集積回路装置

【課題】SRAMの蓄積ノード間容量と、アナログ容量を有する素子とを単一の基板上に形成した半導体集積回路装置の性能の向上を図る。

【解決手段】メモリセル形成領域(SRAM)の一対のnチャネル型MISFET上の酸化シリコン膜21中にプラグP1を形成し、酸化シリコン膜21およびプラグP1の上部に、一対のnチャネル型MISFETのそれぞれのゲート電極とドレインとを接続する局所配線LIc(M0c)を形成した後、さらに、この上部に、容量絶縁膜23および上部電極24を形成し、また、アナログ容量形成領域(Analog Capacitor)の酸化シリコン膜21およびこの膜中のプラグP1上に、メモリセル形成領域に形成される前記局所配線、容量絶縁膜および上部電極と同一工程で、局所配線LIc(M0c)、容量絶縁膜23および上部電極24を形成する。

(もっと読む)

半導体記憶装置

【課題】プレート線の数およびリセット線の数を低減させた半導体記憶装置を提供する。

【解決手段】強誘電体メモリは、セルトランジスタCTおよび強誘電体キャパシタからなるメモリセルMCを、半導体基板上に行列状に配列したセルアレイCAと、メモリセルの列に対して設けられたビット線BLと、メモリセルの行に対して設けられたワード線WLと、強誘電体キャパシタに接続されたプレート線PLであって、セルアレイをm列(m≧2)ごとに分割したn個(n≧2)のカラムブロックCBに対応して設けられたn本のプレート線PLと、ビット線とプレート線との間に接続されたリセットトランジスタRTと、カラムブロック内のm列のそれぞれに対応して設けられたm本のリセット線であって、n個のカラムブロックから1列ずつ、計n列に設けられたn個のリセットトランジスタRTのゲートに接続されたリセット線RSとを備えている。

(もっと読む)

半導体記憶装置

【課題】センス動作の初期における低位側書き込み電位の変動を抑制することにより、高速なセンス動作を行う。

【解決手段】メモリセルに高位側書き込み電位VARY及び低位側書き込み電位VSSAを供給する複数のセンスアンプSAと、センスアンプSAに高位側書き込み電位VARYを供給するドライバ回路121と、センスアンプSAに低位側書き込み電位VSSAを供給するドライバ回路122と、センスアンプSAに低位側書き込み電位又はこれよりも低い補助電位VSSを供給する補助ドライバ回路124とを備えている。これにより、センス動作の開始時における低位側書き込み電位VSSAの浮き上がりを抑制することができることから、従来に比べてセンス動作を高速化することが可能となる。

(もっと読む)

101 - 120 / 150

[ Back to top ]