Fターム[5F083KA20]の内容

Fターム[5F083KA20]に分類される特許

21 - 40 / 150

半導体装置

【課題】製造時以外にデータの追記が可能であり、書き換えによる偽造等を防止可能な不揮発の記憶装置及びそれを有する半導体装置を提供することを課題とする。また、信頼性が高く、安価な不揮発の記憶装置及び半導体装置の提供を課題とする。

【解決手段】絶縁表面上に形成される第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層に挟持される第1の絶縁層と、第1の導電層の一部を覆う第2の絶縁層とを有し、第1の絶縁層は第1の導電層の端部、絶縁表面、及び第2の絶縁層を覆うことを特徴とする記憶装置である。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】安定した性能と高い生産性とを実現する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、メモリセルアレイ部と、第1平面内においてメモリセルアレイ部と並置されたコンタクト部と、を備えた不揮発性半導体記憶装置が提供される。メモリセルアレイ部は、積層体、半導体層、メモリ膜を含む。積層体は、第1平面に対して垂直な第1軸に沿って積層された複数の電極膜とそれらの間の電極間絶縁膜とを含む。半導体層は電極膜の側面に対向する。メモリ膜は電極膜と半導体層との間に設けられ電荷保持層を含む。コンタクト部は、コンタクト部絶縁層と複数のコンタクト電極とを含む。コンタクト部絶縁層は、コンタクト部絶縁膜と粒子とを含む。コンタクト電極はコンタクト部絶縁層を第1軸に沿って貫通する。コンタクト電極は電極膜に接続される。

(もっと読む)

半導体装置の製造方法及びコンピュータ記録媒体

【課題】効率良く多段の良好な形状の階段状の構造を形成することのできる半導体装置の製造方法及びコンピュータ記録媒体を提供する。

【解決手段】第1の誘電率の第1の膜と、第1の誘電率とは異なる第2の誘電率の第2の膜とが交互に積層された多層膜と、多層膜の上層に位置しエッチングマスクとして機能するフォトレジスト層とを有する基板をエッチングして、階段状の構造を形成する半導体装置の製造方法であって、フォトレジスト層をマスクとして第1の膜をプラズマエッチングする第1工程と、水素含有プラズマにフォトレジスト層を晒す第2工程と、フォトレジスト層をトリミングする第3工程と、第3工程によってトリミングしたフォトレジスト層及び第1工程でプラズマエッチングした第1の膜をマスクとして第2の膜をエッチングする第4工程とを有し、第1工程乃至第4工程を繰り返して行うことにより、多層膜を階段状の構造とする。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、少ない工程で多層配線化を実現し、小面積で高機能な機能回路を有する配線基板及び半導体装置を提供する。またこのような高機能な機能回路を表示装置と同一基板上に一体形成した半導体装置を提供することを課題とする。

【解決手段】本発明は、絶縁表面を有する基板上に、第1の配線と、第2の配線と、第3の配線と、第1の層間絶縁膜と第2の層間絶縁膜と、第1のコンタクトホールと第2のコンタクトホールを有し、前記第2の配線の幅を前記第1の配線の幅より広いか、あるいは前記第3の配線の幅を前記第1の配線の幅もしくは前記第2の配線の幅より広く、且つ前記第2のコンタクトホールの直径を前記第1のコンタクトホールの直径より大きく形成することを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】論理回路の動作特性に優れた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、多層配線層と、第1能動素子3a、容量素子19および周辺回路を有する記憶回路200と、第2能動素子3bを有する論理回路100と、記憶回路領域200に形成されており、能動素子3aと容量素子19とを電気的に接続する容量コンタクト13cと、論理回路領域100に形成されており、能動素子3bと第1配線8aとを電気的に接続する接続コンタクト13aと、を備え、第1配線8aは、容量素子19が埋め込まれた配線層のうち最下層の配線層の層間絶縁膜7aに位置しており、接続コンタクト13aは、容量コンタクト13cと同一層に設けられており、第1配線8aと接続コンタクト13aは、デュアルダマシン構造を有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子の容量の増大が実現される半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、半導体基板1内の記憶回路領域に形成されており、多層配線層内に設けられた凹部40内に埋め込まれた少なくとも1以上の容量素子19および周辺回路を有する記憶回路200と、平面視において、半導体基板1内の記憶回路領域とは異なる領域である論理回路領域に形成された論理回路100と、当該凹部40内において、下部電極14、容量絶縁膜15、及び上部電極16から構成される前記容量素子19上に積層している上部接続配線18と、容量素子19が埋め込まれている配線層のうち最上層に設けられた論理回路100を構成する配線8bの上面に接するように設けられたキャップ層6cと、を備え、上部接続配線18の上面30とキャップ膜6cの上面34とが、同一面を構成している。

(もっと読む)

半導体記憶装置

【課題】高速動作が可能な半導体記憶装置を提供する。

【解決手段】実施形態によれば、基板、配線層、メモリ層、回路層及び第1、第2コンタクト配線を含む半導体記憶装置が提供される。配線層は、基板に平行な第1方向に沿う第1配線と、第2配線と、を含む。メモリ層は基板と配線層との間に設けられる。メモリ層は、第1配線と接続されたメモリセルを含む第1メモリセルアレイ部と、第1メモリセルアレイ部と第1方向に沿って並置され第1配線と接続されたメモリセルを含む第2メモリセルアレイ部と、を含む。回路層はメモリ層と基板との間に設けられ、回路部を含む。第1コンタクト配線は、第1メモリセルアレイ部と第2メモリセルアレイ部との間で、回路部の一端と第1配線とを接続する。第2コンタクト配線は、第1メモリセルアレイ部の第1コンタクト配線とは反対の側で、回路部の他端と第2配線とを接続する。

(もっと読む)

半導体装置およびその製造方法

【課題】DRAMセルとロジックを混載したLSIデバイスにおけるアスペクト比の大きいコンタクト構造において、素子分離絶縁膜および不純物拡散層のオーバエッチングを抑制して、接合リークを抑制することを課題とする。

【解決手段】周辺MOSトランジスタを覆う第1エッチングストッパ層121と、DRAMメモリセルのキャパシタ部上層に第2エッチングストッパ層122が形成され、周辺MOSトランジスタの不純物拡散層113は、第1、第2エッチングストッパ層121、122を貫通する電極層131により、上記キャパシタ部上層に形成された金属配線層と接続され、不純物拡散層113の少なくとも一つは素子分離絶縁膜102の境界上に電極層131を接続し、素子分離絶縁膜102上に形成された電極層131の底部の不純物拡散層113表面からの深さ寸法は、不純物拡散層113の接合深さ寸法もより短く形成されたものである。

(もっと読む)

半導体装置

【課題】半導体装置を高集積化する。

【解決手段】本実施形態の半導体装置は、絶縁体内に設けられ、半導体集積回路を含んでいる半導体基板70と、絶縁体の開口部POPを介してその上面が露出するパッド90と、パッド90下方において半導体基板70のキャパシタ領域91内に設けられる複数のキャパシタ1と、を具備し、キャパシタ1は、所定の被覆率を満たすように、パッド90下方のキャパシタ領域91内に設けられ、キャパシタ1の2つの電極にそれぞれ接続されるコンタクト18A,18Gは、開口部POPと上下に重ならない位置に設けられている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】データの取り扱いが容易な半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、基板と、前記基板上に設けられ、それぞれ複数の絶縁膜及び電極膜が交互に積層され、前記基板の上面に対して平行な第1の方向側の端部において、それぞれが各前記電極膜の上面によって構成された複数のテラスが前記第1の方向のみに沿って階段状に形成された積層体と、前記テラスに接続され、前記電極膜を、前記基板の上面に平行な方向であって前記第1の方向に対して直交する第2の方向に引き出し、前記基板に接続する導電部材と、前記積層体の中央部に設けられ、前記絶縁膜及び前記電極膜の積層方向に延びる半導体ピラーと、前記電極膜と前記半導体ピラーとの間に設けられた電荷蓄積層と、を備える。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】良好な伝送性能と小さい配置面積を両立可能なデータバスを備える半導体装置を提供する。

【解決手段】本発明の半導体装置は、配線層M1、M2と、複数のデータ入出力端子と、N本のデータ線(DU、DL)を含むデータバスとを備え、N本のデータ線は所定の配線長の長短に応じた2種類のデータ線群を含む。配線層M1、M2にはデータ線(DL、DU)の各々に隣接する複数のシールド線(Sa、Sb、Sc)が配置され、各データ線(DL、DU)は、配線層M1、M2の積層方向で互いに重ならない位置に配置される。このような配線構造により、各データ線(DL、DU)の間のカップリング容量を抑え、データバスのクロストークを防止することができる。

(もっと読む)

半導体装置の製造方法

【課題】フローティングゲートへの帯電電荷を、別途工程を追加することなく除去できる半導体装置の製造方法を提供する。

【解決手段】半導体基板10の一主面11に少なくともフローティングゲート25を含む電極層22を形成し、電極層22上に層間絶縁膜40を形成し、層間絶縁膜に電極層22を露出するビアホール42と、半導体基板の一主面を露出するビアホール48を形成し、ビアホール42を介して電極層22と電気的に接続され、ビアホール48を介して半導体基板10と電気的に接続される配線層60を形成し、配線層60をパターニングして少なくとも電極層22のみに接続されている配線62を形成する。

(もっと読む)

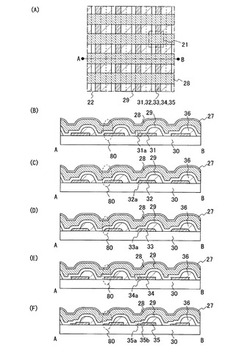

不揮発性半導体記憶装置

【課題】柱状のチャネル層となる半導体層に沿って、複数の浮遊ゲート型の不揮発性メモリセルが積層された構造の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、柱状の半導体膜131の側面にトンネル誘電体膜141、浮遊ゲート電極膜142、ゲート間絶縁膜143および制御ゲート電極膜144を備えるメモリセルMCが半導体膜131の延在方向に複数設けられるメモリセル列を、半導体基板101上に略垂直に複数配置した不揮発性半導体記憶装置が提供される。ここで、浮遊ゲート電極膜142と制御ゲート電極膜143は、柱状の半導体膜131の全周のうち特定の方向の側面にのみ形成されている。

(もっと読む)

半導体記憶装置

【課題】給電セルのレイアウト面積を縮小することによりメモリアレイ全体のレイアウト面積をさらに縮小することが可能な半導体記憶装置を提供する。

【解決手段】第1の金属配線層に、Nウェル電圧VDDBを供給するメタル312を設ける。メタル312は、共有コンタクト216および219によりNウェル領域に設けられた活性層300と電気的に結合され、Nウェル領域に対してNウェル電圧VDDBが供給される。第3の金属配線層にPウェル電圧VSSBを供給するメタル332,333を設ける。Nウェル電圧VDDBを供給するメタル312は、第1の金属配線層のメタルを用いた構成としているため下層へのくい打ち領域を必要とせず、Pウェル電圧VSSBのメタル332,333の下層へのくい打ち領域のみ確保すればよい。したがって、給電セルPMCのY方向の長さを縮小して、給電セルのレイアウト面積を縮小することができる。

(もっと読む)

半導体装置

【課題】CMOSインバータを含むメモリセルにおいて、リーク電流によるゲート配線の制約やデザインルールの制約を起因とするメモリセルの面積の増大を抑える。

【解決手段】第1のインバータIV1と第2のインバータIV2を含むメモリセル1Aの第1の金属層として、第1の配線FL1及び第2の配線FL2が配置されている。第1の配線FL1は、第1のインバータIV1の2つのドレインDと第2のインバータIV2の第2のゲート配線GL2と接続している。第2の配線FL2は、第2のインバータIV2の2つのドレインDと第1のインバータIV1の第1のゲート配線GL1と接続している。第1の配線FL1は第2のゲート配線GL2と重畳し、第2の配線FL2は第1のゲート配線GL1と重畳して配置される。第1の金属層よりも上層には、第2の金属層と、その上層の第3の金属層が配置されている。

(もっと読む)

半導体記憶装置

【課題】従来の半導体記憶装置は、配線間の負荷のばらつきに起因して性能及び信頼性が低下する問題があった。

【解決手段】本発明の半導体記憶装置は、メモリセルC1〜C6が配置され、半導体基板に対して垂直方向に積層されるメモリ素子層ML1〜ML6と、ワード線W0〜W6が配置される第1の配線層群(L2、L4、L6)と、最上層配線層L1の配線を含む第1の配線(ビット線B0)と最下層配線層L7の配線を含む第2の配線(ビット線B1)とを含む第2の配線層群(L1、L3、L5、L7)と、を有し、メモリ素子層ML1〜ML6には、それぞれ同一の数のメモリセルが配置され、第1の配線B0と第2の配線B1は、第2の配線層群において交互に配置され、第1の配線B0は、最上層配線と、他の配線層に属し最上層配線と接続される配線とを含み、第2の配線B1は、最下層配線と、他の配線層に属し最下層配線と接続される配線とを含む。

(もっと読む)

ストリング選択線及びビット線の改善されたコンタクトレイアウトを有する3次元メモリアレイ

【課題】インターコネクト及びコンタクト用の実装面積が小さい3次元集積回路メモリ用の構造を低製造コストで提供する。

【解決手段】3次元メモリデバイスは、絶縁材料21,22,23,24で分離され、復号化回路を介してセンスアンプに結合可能なビット線BLnとして導電材料の複数の帯片の形状をしている。導電材料帯片11,12,13,14は、スタック横面に側面を有する。ワード線WLn,WLn+1の複数の導電線16,17は行デコーダに結合でき、複数のスタック上で直交して延びる。導電線は、スタックの表面に共形である。記憶素子は、スタック上の半導体材料帯片の側面と導電線の間の交点の界面領域の多層アレイに設けられる。3次元メモリは、複数層に対する2つの最小線幅のマスクで作られる。半導体材料帯片の端部に階段構造が含まれる。半導体材料帯片に平行な金属層上と、ワード線に平行な上部金属層上にSSLインターコネクトを含む。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子のビア構造物及び導電構造物を提供する。

【解決手段】前記ビア構造物は、平坦部及び突出部を含む表面を有する。前記導電構造物は前記平坦部のうち、少なくとも一部上に形成され、前記突出部のうち、少なくとも一部上には形成されない。例えば、前記導電構造物は前記平坦部上のみに形成されて前記突出部上には全く形成されない。これによって、前記導電構造物と前記ビア構造物との間に高品質の接続を形成することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】歩留まりに優れた構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、基板内の記憶回路領域に形成されており、多層配線層内に埋め込まれた少なくとも1以上の容量素子および周辺回路を有する記憶回路と、平面視において、基板内の憶回路領域とは異なる領域である論理回路領域に形成された論理回路と、を備え、容量素子は、下部電極、容量絶縁膜、上部電極、埋設電極および、上部接続配線で構成されており、上部接続配線と埋設電極とは、同一の材料かつ一体に構成されており、上部接続配線と下部電極との間には、論理回路を構成する前記配線が少なくとも1以上設けられており、上部接続配線の上面と、上部接続配線と同じ配線層に形成された論理回路を構成する配線の上面とが、同一面を構成する。

(もっと読む)

ノードコンタクト構造体

【課題】ノードコンタクト構造体を有する半導体素子と、その製造方法を提供する。

【解決手段】半導体基板の上に形成されソース/ドレイン領域を有するバルクモストランジスタを備える。該バルクモストランジスタ上に層間絶縁膜が形成され、該層間絶縁膜上にソース/ドレイン領域を有する薄膜トランジスタが形成される。該バルクモストランジスタのソース/ドレイン領域上に半導体プラグが形成され、該半導体プラグは該層間絶縁膜の少なくとも一部を介して延長される。該薄膜トランジスタのソース/ドレイン領域及び該半導体プラグは金属プラグと接触し、該金属プラグは該層間絶縁膜の少なくとも一部を介して延長される。該半導体プラグ及び該金属プラグは多層のプラグを構成する。

(もっと読む)

21 - 40 / 150

[ Back to top ]