Fターム[5F083LA12]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | 配線レイアウト (4,019) | ビット線 (1,534)

Fターム[5F083LA12]の下位に属するFターム

オープンビット線 (46)

折り返し(フォールディッド)ビット線 (43)

交差型(ツイスティッド)ビット線 (22)

Fターム[5F083LA12]に分類される特許

161 - 180 / 1,423

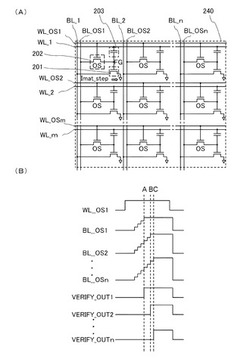

半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな駆動方法を提供する。また、新たな駆動方法により、メモリ素子への書き込み電位のばらつきを低減し、信頼性を向上させる。

【解決手段】半導体装置の駆動方法において、書き込み電位を段階的に上昇させて、同時に読み出し電流を確認し、読み出し電流の結果を書き込み電位に利用して書き込みを行う。つまり、正しい電位で書き込みが行われたか確認しながら書き込みを行うことで、信頼性の高い書き込みを行うことが可能である。

(もっと読む)

半導体装置

【課題】小型化が可能な不揮発性メモリを備えた半導体装置を提供する。

【解決手段】基板901上に画素と不揮発性メモリとを備え、不揮発性メモリは、基板901上に形成される半導体活性層と、半導体活性層上に形成される絶縁膜923と、絶縁膜923上に形成されるフローティングゲイト電極907と、フローティングゲイト電極907を酸化して得られる酸化膜908,915,922と、酸化膜908,915,922に接して形成されるコントロールゲイト電極929と、を備え、画素と不揮発性メモリとは、基板901上に一体形成される。

(もっと読む)

スイッチアレイ

【課題】 スイッチアレイの占有面積の縮小を図る。

【解決手段】本実施形態のスイッチアレイは、基板上に設けられる2つのスイッチと、第1の方向に延在する第1及び第2の制御線と、を具備し、スイッチのそれぞれは、メモリセルトランジスタが設けられる第1のアクティブ領域と、パストランジスタが設けられる第2のアクティブ領域と、を含み、アクティブ領域内でトランジスタのチャネル長方向に隣接するメモリセルトランジスタはソース又はドレインを共有し、第1及び第2のアクティブ領域は、トランジスタのチャネル幅方向に互いに隣接している。

(もっと読む)

半導体記憶装置

【課題】SRAMのゲート配線形成にあたって、ゲート形状を複雑に変形させることなく転写及び加工マージンを確保する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1組及び第2組のドライバトランジスタ11、ロードトランジスタ12及びアクセストランジスタ13とを備えたメモリセルが半導体基板上に2次元配列されたメモリセルアレーと、複数のワードラインと、複数のビットラインと、第1組のドライバトランジスタ11とロードトランジスタ12とを接続し、直線状の側辺を有する長方形状の第1ゲート配線3aと、アクセストランジスタ13と接続され、直線状の側辺を有する長方形状の第2ゲート配線3cと、第1ゲート配線3aと、第2組のドライバトランジスタ11とロードトランジスタ12とを接続する第1コネクタ5aと、第2ゲート配線3cとワードラインとを接続する第2コネクタ5cとを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】高速動作が可能な半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、第1の方向に平行に延在する第1素子分離溝部とそれに交差する方向に延在する第2素子分離溝部とが交互に連なってなる素子分離溝に第1絶縁膜を埋め込んで形成された素子分離領域を複数備え、素子分離領域間に第1素子形成部と第2素子形成部とが交互に連なってなる素子形成領域を複数備え、各第1素子形成部は所定数の第1半導体ピラーを備え、各第2素子形成部は第2半導体ピラーを備え、各素子形成領域はピラーの下部に不純物拡散層からなる第1のビット線を備え、ピラーの上部に上部不純物拡散層を備え、各素子形成領域の第2半導体ピラーの上部不純物拡散層に電気的に接続する第1のビット線より低抵抗の第2のビット線を備え、ピラーの下部側壁に第2絶縁膜を介して第2の方向に延在するワード線を備えることを特徴とする。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置の加工精度をより向上させる。

【解決手段】不揮発性半導体記憶装置の製造方法は、制御ゲート電極膜と絶縁膜とが交互に積層された積層膜の上に、積層膜の主面に対して垂直な方向からみて、ストライプ状の第1マスク膜と、ストライプ状の犠牲膜と、が第1方向に交互に配列された層を形成する工程と、配列された層の上に選択的に形成される複数の第2マスク膜であって、犠牲膜のいずれかと、いずれかの犠牲膜に隣接する一方の第1マスク膜および他方の第1マスク膜を複数の第2マスク膜のそれぞれにより被覆し、第1方向に隣接する第2マスク膜のあいだの犠牲膜を表出する複数の第2マスク膜を形成する工程と、複数の第2マスク膜から表出された犠牲膜のそれぞれを選択的に除去した後、複数の第1マスク膜および複数の第2マスク膜から表出された積層膜を選択的に除去する工程と、を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】安定した動作を実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、複数のセルユニットを有し且つ複数のセルユニットに保持されたデータを消去する消去動作実行の単位とされる複数のメモリブロックを備える。セルユニットは、メモリストリング、第1トランジスタ、第2トランジスタ、及びダイオードを備える。第1トランジスタは、メモリストリングの一端に一端を接続されている、第2トランジスタは、メモリストリングの他端と第2配線との間に設けられている。ダイオードは、第1トランジスタの他端と第1配線との間に設けられている。ダイオードは、基板に対して垂直方向に延びる第1導電型の第2半導体層と、第2半導体層の上面に接して基板に対して垂直方向に延びる第2導電型の第3半導体層とを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択メモリセルから確実にデータを読み出すことのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施の形態に係る不揮発性半導体記憶装置は、複数の不揮発性メモリセルに接続されるワード線と不揮発性メモリセルを選択してデータ読み出し動作を制御する制御回路とを備える。制御回路はデータ読み出し動作実行の際、選択メモリセルに接続された選択ワード線に、隣接する閾値電圧分布の中間電圧に第1の調整電圧を加えた電圧を印加し、選択ワード線に隣接する第1の非選択ワード線に、不揮発性メモリセルを導通させ得る読み出しパス電圧から第2の調整電圧を引いた電圧を印加し、第1の非選択ワード線に隣接する第2の非選択ワード線に、読み出しパス電圧に第2の調整電圧を加えた電圧を印加し、第1の非選択ワード線及び第2の非選択ワード線を除く非選択のワード線に、読み出しパス電圧を印加する。

(もっと読む)

不揮発性半導体記憶装置

【課題】安定した動作を実行可能な不揮発性半導体記憶装置法を提供する。

【解決手段】制御回路は、消去動作時、選択セルユニットに接続された第1配線の電圧を、選択セルユニットに含まれる第1トランジスタのゲートの電圧よりも第1電圧だけ大きくする。制御回路は、消去動作時、非選択セルユニットに接続された第1配線の電圧と、非選択セルユニットに含まれる第1トランジスタのゲートの電圧との間の電圧差を第1電圧と異なる第2電圧とする。また、制御回路は、消去動作時、選択セルユニット及び非選択セルユニットにおいて、ダミーメモリストリング中の少なくとも1つのダミーメモリトランジスタのゲートに第3電圧を印加し、ダミーメモリストリング中の別のダミーメモリトランジスタのゲートに第3電圧よりも低い第4電圧を印加する。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】1つの実施形態は、絶縁膜に形成された溝に導電物質を容易に埋め込むことができる半導体装置の製造方法、及びそのような製造方法に適した半導体装置を提供する。

【解決手段】1つの実施形態によれば、コンタクトプラグを形成し、コンタクトプラグを覆うエッチングストッパー膜を形成し、エッチングストッパー膜を覆う絶縁膜を形成し、絶縁膜及びエッチングストッパー膜にコンタクトプラグの表面を露出する溝を形成し、エッチングストッパー膜のエッチングレートに対し絶縁膜のエッチングレートの方が高くなる条件で、コンタクトプラグとコンタクトプラグの周辺とを含む領域を選択的にエッチバックし、エッチバックを行った後に溝に導電物質を埋め込んでラインパターンを形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】微細化が進展しても読み出し動作時の電流を維持する。

【解決手段】複数のメモリサブブロックの各々は、第1ノードと第2ノードとの間に並列接続された複数のメモリトランジスタを含む。メモリサブブロックは、第1導電層と、第2導電層と、半導体層と、第3導電層とを備える。第1導電層は、層間絶縁膜を貫通して半導体基板に対し垂直な第1方向に延びるように形成され第1ノードとして機能する。第2導電層は、層間絶縁膜を貫通して半導体基板に対し第1方向に延びるように形成され第2ノードとして機能する。半導体層は、第1導電層と第2導電層とを接続するように半導体基板と平行な第2方向に延びるように形成されメモリトランジスタのチャネル層として機能する。第3導電層は、半導体層上にゲート絶縁膜を介して形成される。ゲート絶縁膜は、電荷蓄積膜を一部に含み第3導電層を囲う閉ループ状に形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】安定した動作を実行可能な不揮発性半導体記憶装置法を提供する。

【解決手段】メモリストリングは、電気的に書き換え可能な複数のメモリトランジスタ、及びスペアメモリトランジスタを直列接続してなる。ワード線は、メモリトランジスタのゲートに接続されている。スペアワード線は、スペアメモリトランジスタのゲートに接続されている。メモリストリングは、第1半導体層、電荷蓄積層、複数の第1導電層、及び第2導電層を備える。第1半導体層は、基板に対して垂直方向に延びる第1半導体層を含む。電荷蓄積層は、第1半導体層の側面を取り囲む。複数の第1導電層は、電荷蓄積層を介して第1半導体層の側面を取り囲みワード線として機能する。第2導電層は、電荷蓄積層を介して第1半導体層の側面を取り囲み、スペアワード線として機能する。制御回路は、ワード線に代えてスペアワード線を駆動可能である。

(もっと読む)

不揮発性半導体記憶装置

【課題】高品質な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1は、可変抵抗素子24と非線形な電流電圧特性を有する電流制限素子22とを含むメモリセルCUsをマトリクス状に配置したメモリセルアレイ2と、メモリセルCUsにセル電流icellを流して、可変抵抗素子24の抵抗値を変化させるドライバ30と、セル電流icellの大きさに基づいてメモリセルCUsの抵抗値の変化を検知する検出部31と検出部31に、セル電流icellの代わりにダミー電流idummyを流すダミー電流部32とを具備する。

(もっと読む)

不揮発性半導体記憶装置の製造方法及び不揮発性半導体記憶装置

【課題】シリサイド工程による不具合を抑制しつつ、十分な量のシリサイドを形成することのできる不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】不揮発性半導体記憶装置の製造方法は、浮遊ゲート電極、浮遊ゲート電極上の第1の電極間絶縁膜及び第1の電極間絶縁膜上の制御ゲート電極を有するメモリセルトランジスタを形成し、下側ゲート電極、第2の電極間絶縁膜及び第2の電極間絶縁膜上の上側ゲート電極を有する電界効果トランジスタを形成する。制御ゲート電極及び上側ゲート電極の上面が露出するように層間絶縁膜を形成する。制御ゲート電極及び上側ゲート電極の上面が層間絶縁膜の上面よりも低くなるようにエッチバックする。制御ゲート電極、上側ゲート電極及び層間絶縁膜上の全面に第1の導電膜を形成する。第1の層間絶縁膜をエッチバックする。制御ゲート電極、上側ゲート電極及び第1の導電膜上に金属を堆積してシリサイド化する。

(もっと読む)

半導体装置の製造方法

【課題】隣接する活性領域の間で横方向に成長するシリコン膜が連結されることを防ぎつつ、活性領域上に十分な厚みのシリコン膜を形成可能とした半導体装置の製造方法を提供する。

【解決手段】ゲート電極6aを挟んだ両側の活性領域5上に第1のシリコン膜12aを選択的にエピタキシャル成長させる工程と、複数のワード配線層WLの各間に第1のシリコン膜12aを覆うのに十分な厚みでマスク絶縁膜を埋め込んだ後、このマスク絶縁膜を第1のシリコン膜12aの表面が露出するまでエッチングにより除去する工程と、第1のシリコン膜12a上に第2のシリコン膜12bを選択的にエピタキシャル成長させる工程とを含む。

(もっと読む)

多値抵抗変化メモリ

【課題】書き込み制御性が良く、高信頼性の多値抵抗変化メモリを提案する。

【解決手段】実施形態に係わる多値抵抗変化メモリは、一端が第1のノードN1に接続され、他端が第2のノードN2に接続される第1の抵抗変化膜RW1、一端が第3のノードN3に接続され、他端が第2のノードN2に接続される第2の抵抗変化膜RW2、及び、第1及び第2のノードN1,N2の間に接続されるキャパシタCPを備えるメモリセルMCと、第1及び第2の抵抗変化膜RW1,RW2を含む第1のパスAを通過する第1の電圧パルス、及び、第2の抵抗変化膜RW2及びキャパシタCPを含む第2のパスBを通過する第2の電圧パルスを生成する電圧パルス生成回路21と、書き込み時に第1及び第2の電圧パルスを用いてメモリセルMCに多値データを記憶させる制御回路22とを含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込みを高速化した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置110は、ベース半導体層10aと、電極70aと、チャネル半導体層30aと、ベーストンネル絶縁膜20aと、チャネルトンネル絶縁膜40aと、電荷保持層50aと、ブロック絶縁膜60aと、を有するメモリ部MC1を備える。チャネル半導体層30aは、ベース半導体層10aと電極70aとの間に設けられ、電極70aに対向するチャネル部31aを含む。ベーストンネル絶縁膜20aは、ベース半導体層10aとチャネル半導体層30aとの間に設けられる。チャネルトンネル絶縁膜40aは、電極70aとチャネル部31aとの間に設けられる。電荷保持層50aは、電極70aとチャネルトンネル絶縁膜40aとの間に設けられ、電荷を保持する。ブロック絶縁膜60aは、電極70aと電荷保持層50aとの間に設けられる。

(もっと読む)

不揮発性半導体記憶装置

【課題】 データ保持特性に優れた不揮発性半導体記憶装置を提供する。

【解決手段】 第1電極2と、第1電極2より仕事関数の大きい第2電極3、両電極の間に介装された可変抵抗体4を備え、一方の電極が可変抵抗体4とオーミック接合し、他方の電極が可変抵抗体4と非オーミック接合し両電極間に電圧印加することで抵抗状態が2以上の異なる抵抗状態間で遷移する可変抵抗素子1と、第1電極2を基準として第2電極3に正または負の書き込み電圧を選択的に印加することで、可変抵抗素子1の抵抗状態を低抵抗状態から高抵抗状態または高抵抗状態から低抵抗状態へ遷移させる書き込み動作を実行する書き込み回路と、第1電極2を基準として第2電極3に正の読み出し電圧を印加することで、第2電極3から第1電極2に向けて流れる電流を検知して可変抵抗素子1の抵抗状態を判定する読み出し回路を備えてなる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】選択トランジスタのカットオフ特性を維持しつつ、オフセット特性の悪化を抑制する。

【解決手段】半導体基板の表層部を活性領域に分離する素子分離絶縁膜と、前記半導体基板の活性領域上のゲート絶縁膜上に形成され第1の導電層、電極間絶縁膜および第2の導電層を有するメモリゲート電極および前記メモリゲート電極の両脇に位置する前記活性領域に形成された第1のソース/ドレイン領域を備えたメモリセルトランジスタと、前記メモリセルトランジスタに隣接して配置され、前記第1のゲート絶縁膜上に導電層を積層した選択ゲート電極および前記選択ゲート電極の両脇に位置する前記活性領域に形成された第2のソース/ドレイン領域を備えた選択ゲートトランジスタとを有し、前記活性領域に形成される少なくとも前記第2のソース/ドレイン領域は、前記活性領域の表層部が掘り下げられた凹部に設けられていることを特徴とする。

(もっと読む)

記憶装置

【課題】電荷の漏洩による出力信号の誤出力が抑制可能な記憶装置、及び当該記憶装置を用いた表示装置を得ることを課題とする。

【解決手段】光信号を電気信号に変換する光電変換素子と、当該光電変換素子に電気的に接続され、チャネル形成領域に酸化物半導体膜を有するトランジスタと、当該トランジスタに電気的に接続され、当該電気信号を蓄積することで出力電圧を生成する保持容量とを有する記憶装置、及び当該記憶装置を用いた表示装置に関する。

(もっと読む)

161 - 180 / 1,423

[ Back to top ]