Fターム[5F083LA12]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | 配線レイアウト (4,019) | ビット線 (1,534)

Fターム[5F083LA12]の下位に属するFターム

オープンビット線 (46)

折り返し(フォールディッド)ビット線 (43)

交差型(ツイスティッド)ビット線 (22)

Fターム[5F083LA12]に分類される特許

201 - 220 / 1,423

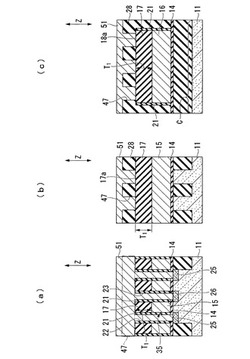

半導体装置の製造方法

【課題】ゲート電極に形成された研磨後のキャップ絶縁膜の厚さを容易に推定できる半導体装置の製造方法を提供する。

【解決手段】半導体装置形成領域に第1の導電膜よりなるゲート電極15、半導体装置非形成領域に絶縁膜形成部16、及び絶縁膜よりなり、ゲート電極の上面及び絶縁膜形成部の上面を覆うキャップ絶縁膜17を形成し、次いで、キャップ絶縁膜を覆う層間絶縁膜28を形成し、次いで、キャップ絶縁膜上に形成された層間絶縁膜にゲート電極の延在方向と交差する方向に延在する溝47を形成すると共に、溝の下方に位置する層間絶縁膜に不純物拡散層を露出するコンタクトホール22,23を形成し、次いで、溝及びコンタクトホールを埋め込む第2の導電膜51を形成し、次いで、CMP法により第2の導電膜を研磨することでコンタクトプラグを形成し、その後、絶縁膜形成部に形成されたキャップ絶縁膜の厚さを測定する。

(もっと読む)

半導体メモリ装置

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを保存する半導体メモリ装置を提供する。

【解決手段】書き込みトランジスタのドレインと読み出しトランジスタのゲート、および、前記ドレインとキャパシタの一方の電極を接続した記憶セルを2つ用いて形成された記憶ユニットのマトリクスにおいて、第1の記憶セルの書き込みトランジスタのゲートを第1のワード線に、キャパシタの他方の電極を第2のワード線に接続する。また、第2の記憶セルの書き込みトランジスタのゲートを第2のワード線に、キャパシタの他方の電極を第1のワード線に接続する。さらに、集積度を高めるために、各記憶セルの読み出しトランジスタのゲートを互い違いに配置する。

(もっと読む)

半導体装置及びその製造方法

【課題】デバイス特性及びプロセスのばらつきを低減できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板10と、下部ゲート層BGと、積層体と、ダミー電極層DWLと、絶縁膜30と、チャネルボディ20,45とを備えた。下部ゲート層BGは、基板10上に設けられた。積層体は、下部ゲート層BG上にそれぞれ交互に積層された複数の絶縁層と複数の電極層WLとを有する。ダミー電極層DWLは、下部ゲート層BGと積層体との間に設けられ、電極層WLと同じ材料からなり、各々の電極層WLよりも厚い。絶縁膜30は、積層体及びダミー電極層を貫通して形成されたホールMHの側壁に設けられた電荷蓄積膜を含む。チャネルボディ20,45は、ホールMH内における絶縁膜30の内側に設けられた。

(もっと読む)

半導体装置

【課題】集積度の高い相変化メモリを実現する。

【解決手段】本発明による半導体装置は、複数のワード線と、複数のワード線と直交する複数のビット線との交点に配置された複数のメモリセル群を有する。複数のメモリセル群は、直列接続された第一乃至第二のメモリセルを有する。第一乃至第二のメモリセルの各々は、並列接続される選択トランジスタと抵抗性記憶素子とを有する。第一のメモリセルにおける選択トランジスタのゲート電極は、第一のゲート線に接続され、第二のメモリセルにおける選択トランジスタのゲート電極は、第二のゲート線に接続される。そして、複数のワード線を駆動する第一の回路ブロック(ワードドライバ群WDBK)は、第一乃至第二のゲート線を駆動する第二の回路ブロック(相変化型チェインセル制御回路PCCCTL)と、複数のメモリセル群(メモリセルアレーMA)との間に配置される。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルに書き込み用のトランジスタ、読み出し用のトランジスタおよび選択用のトランジスタを備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】記憶素子の下にあるコンタクトプラグの上面の平坦性を改善し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、半導体基板上に設けられた複数のスイッチングトランジスタと、隣接する2つのスイッチングトランジスタ間に埋め込まれ、該隣接する2つのスイッチングトランジスタの各ゲートから絶縁されかつ該隣接する2つのスイッチングトランジスタのソースまたはドレインに電気的に接続され、上面がスイッチングトランジスタの上面よりも高い位置にあるコンタクトプラグと、コンタクトプラグの上面上に設けられ、データを記憶する記憶素子と、記憶素子上に設けられた配線とを備えている。

(もっと読む)

抵抗変化素子の駆動方法及び不揮発性記憶装置

【課題】安定した多値記憶動作を実現することができる抵抗変化素子の駆動方法を提供する。

【解決手段】第1の極性の複数の異なる電圧値の書き込み電圧パルスのうちの一つの書き込み電圧パルスを抵抗変化素子10に与える(S101、S102)書き込み工程と、第1の極性とは異なる第2の極性の複数の異なる電圧値の読み出し電圧パルスを電圧値が小さい方から順次抵抗変化素子10に与える(S205〜S209)読み出し工程とを実行する。この読み出し工程では、読み出し電圧パルスが順次与えられたときの抵抗変化素子の抵抗状態の変化に応じて、何れの電圧値の書き込み電圧パルスによって書き込み工程が行われたのかを判別する(S210)。

(もっと読む)

不揮発性可変抵抗素子、及び、不揮発性半導体記憶装置

【課題】 大容量で安価、回り込み電流が抑制され、且つ、高速動作が可能な不揮発性の可変抵抗素子を用いる不揮発性半導体記憶装置を実現する。

【解決手段】

膜中の酸素濃度により抵抗が変化する金属酸化膜からなる可変抵抗体13と、可変抵抗体上に形成された絶縁膜16と、可変抵抗体を挟持する第1の電極14および第2の電極15と、絶縁膜16を介して可変抵抗体13と対向する第3の電極17を備える不揮発性可変抵抗素子を用いてメモリセルアレイを構成する。第3の電極17を介して電圧を印加し、可変抵抗体13と絶縁膜16の界面に垂直な方向に閾値以上の電界を誘起することで書き換えを行うとともに、第1の電極14と第2の電極15間に電圧を印加することで可変抵抗体の抵抗状態を読み出す。

(もっと読む)

マスタスライス方式メモリセル

【課題】複数種類の回路構成をマスタスライス方式で対応可能なメモリセル専用のマスタスライス方式メモリセルを提供すること。

【解決手段】メモリユニットが2行2列に配置されてメモリセルを構成する。メモリユニットは、行方向に沿って並置され列方向に伸長される第1〜第3拡散層を備え、各拡散層で並列接続のトランジスタが構成される。第1および第2ワード線は第1〜第3拡散層の両端部外方に配置される。第1〜第3拡散層の第1コンタクト層とゲート層の第2コンタクト層との間、第1コンタクト層と第1/第2ワード線との間に、行方向に沿って第1のメタル配線領域が確保される。第1のメタル配線領域には、第2または第3メタル層の何れかが配線可能である。第1及び第2拡散層、第2及び第3拡散層の間には、列方向に沿って第2のメタル配線領域が確保される。第2のメタル配線領域には第3メタル層が配線可能である。

(もっと読む)

半導体メモリ

【課題】 センスアンプの活性化タイミングをリアルメモリセルの電気的特性に合わせて最適に設定する。

【解決手段】 半導体メモリは、センスアンプイネーブル信号の活性化に応答して動作し、リアルセルトランジスタに流れるセル電流により変化するビット線の電圧に応じて、メモリセルに保持されている論理を判定するセンスアンプと、第1ノードと接地線の間に直列に接続されたレプリカセルトランジスタと、タイミング生成部とを有している。タイミング生成部は、レプリカセルトランジスタを介して接地線に接続される第1ノードが高レベルから低レベルに変化するときにセンスアンプイネーブル信号を活性化する。レプリカセルトランジスタは、定電圧を受けるコントロールゲートと、コントロールゲートに接続されたフローティングゲートとを含んでいる。

(もっと読む)

抵抗変化メモリ

【課題】非オーミック素子の厚さを薄くする。

【解決手段】本発明の例に係わる抵抗変化メモリは、第1方向に延びる第1の配線と、第2方向に延びる第2の配線と、第1の配線と第2の配線との交点に設けられ、抵抗状態の変化に応じてデータを記憶するメモリ素子20と非オーミック素子30とが直列接続されたセルユニットセルユニットCUと、を具備し、非オーミック素子30Aは、メタル層31と、第1の半導体層33と、半導体層33とメタル層31との間に設けられ、第1のメタル層31との界面に偏在層38bを有する第2の半導体層38とを含む。

(もっと読む)

不揮発性記憶装置及びその製造方法

【課題】バイポーラ駆動でセット動作、リセット動作を確実に行うことができる不揮発性記憶装置及びその製造方法を提供する。

【解決手段】第1電極であるワード線WLと、第2電極であるビット線BLと、ワード線WLとビット線BLとの間に設けられ、第1抵抗状態と第2抵抗状態とのあいだを遷移する抵抗変化部25と、抵抗変化部25とワード線WLとの間に設けられ、p形半導体を含むp層22pと真性半導体を含むi層22iとn形半導体を含むn層22nとを有し、真性半導体よりもバンドギャップエネルギーの小さい不純物220であって、i層22iにおける濃度のピークがi層22iの層厚における中央部にある不純物220を含む選択素子22と、を備える。

(もっと読む)

半導体記憶装置

【課題】 高度に微細化されていても、チップ面積の増大を招くことなく所望の配線を配置可能な半導体記憶装置を提供する。

【解決手段】 半導体記憶装置は、半導体基板内に形成された活性領域12、複数の第1ビット線SABLを含む。第1配線BLCRLは、複数の第1ビット線と交わる方向に沿って延び、半導体基板上に形成された複数のメモリセルと接続された複数の第2ビット線BLのうちの非選択の第2ビット線に印加される制御電位を伝送する。第2配線21は、第1配線と電気的に接続され、第1ビット線に沿って延びる。第3配線23は、第2配線と電気的に接続され、第1ビット線と交わる方向に延びる。第4配線34は、第3配線と、活性領域の制御電位を印加されるノードに相当する部分内の不純物拡散層と、を電気的に接続する。

(もっと読む)

半導体装置およびその製造方法

【課題】スプリットゲート構造の不揮発性メモリセルを有する半導体装置において、製造歩留まりを向上できる技術を提供する。

【解決手段】給電領域に位置するCGシャント部の選択ゲート電極CGの半導体基板1の主面からの第2高さd2が、メモリセル形成領域の選択ゲート電極CGの半導体基板1の主面からの第1高さd1よりも低くなるように、CGシャント部の選択ゲート電極CGを形成する。

(もっと読む)

抵抗変化メモリ

【課題】メモリセルアレイの面積を縮小する。

【解決手段】抵抗変化メモリ10は、第1の方向に延在する複数のビット線BLと、第2の方向に延在する複数のワード線WLと、複数のメモリセルMCを備えたメモリセルアレイ11とを含む。各メモリセルMCは、可変抵抗素子21と選択トランジスタ22とを有し、可変抵抗素子21の第1の端子は第1のビット線に接続され、可変抵抗素子21の第2の端子は選択トランジスタ22のドレインに接続され、選択トランジスタ22のソースは第2のビット線に接続され、選択トランジスタ22のゲートはワード線に接続される。第1の方向に順に並んだ第1乃至第4の可変抵抗素子のレイアウトにおいて、第1及び第2の可変抵抗素子は1本のワード線を挟み、第2及び第3の可変抵抗素子は2本のワード線を挟み、第3及び第4の可変抵抗素子は1本のワード線を挟む。

(もっと読む)

半導体装置

【課題】高集積なCMOS型SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体137と第1の第2導電型半導体104との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、第1の第1導電型半導体137の上下に配置された第1の第2導電型高濃度半導体182と、第2の第2導電型高濃度半導体141と、第1の第2導電型半導体104の上下に配置された第1の第1導電型高濃度半導体186と、第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート導電体167と、を有するインバータを用いてSRAMを構成する。

(もっと読む)

半導体装置の製造方法

【課題】検査コストや解析コスト、製品コストを低減可能な半導体装置の製造方法を提供する。

【解決手段】例えば、ウエハ検査工程(S1003)で、半導体ウエハ上のロジック回路を対象とした電気的検査(ロジック部テスト)(S1003a)と、メモリ回路を対象とした電気的検査(メモリ部テスト)(S1003b)を行い、それぞれの検査結果から得られた故障箇所を複合マップ24上に重ねて表示する。この複合マップ24を用いると、例えば、ロジック故障22とメモリ故障23が併存して分布する領域を判別でき、この領域に対してメモリ故障23に対する詳細解析を優先的に行うことで、特にロジック故障22とメモリ故障23の故障原因が共通であった場合に効率的な詳細解析を行うことが可能となる。

(もっと読む)

半導体記憶装置

【課題】 製造コストおよびプロセス歩留りの改善が可能となる、抵抗変化素子を含む半導体記憶装置を提供すること。

【解決手段】 第1の方向に並んで設けられた第1および第2のMOSFETと、前記第1および第2のMOSFETの上方に設けられ下端が前記第1および第2のMOSFETのドレインに接続された第1の抵抗変化素子と、第1の方向に並んで設けられた第3および第4のMOSFETと、前記第3および第4のMOSFETの上方に設けられ下端が前記第3および第4のMOSFETのドレインに接続された第2の抵抗変化素子と、前記第1および第2のMOSFETのソースに接続され第1の方向に延びる第1の配線と、前記第3および第4のMOSFETのソースに接続され第1の方向に延びる第2の配線と、前記第1の抵抗変化素子の上端と前記第2の抵抗変化素子の上端とを接続する上部電極と、前記上部電極に接続され第1の方向に延びる第3の配線とを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】動作時の電流の上限値を適切に設定してメモリセルの破壊等を防止しつつも、動作時間を短縮する。

【解決手段】メモリセルは、第1配線と第2配線との間に配置され可変抵抗素子を有する。制御回路は、第1及び第2配線を介してメモリセルの動作に必要な電圧を印加する。電流制限回路は、第1配線に接続され動作時にメモリセルに流れる電流を所定の制限値に制限する。制御回路は、第1配線に第1の電圧を与える一方、第2配線には前記第1の電圧よりも小さくその電圧値が時間の経過と共に低下する第2の電圧を与える。

(もっと読む)

不揮発性半導体記憶装置

【課題】生産性及び動作安定性の向上を可能とする不揮発性半導体記憶装置を提供する。

【解決手段】交互に積層された複数の電極膜14及び絶縁膜を含み、X軸方向に延在する第1、第2積層構造体Sa1、Sa2と、これらに積層された第1、第2選択ゲート電極SGa1、SGa2と、これらのそれぞれを貫通し、下端が接続された第1、第2半導体ピラーSPa1、SPa2と、電極膜14と記憶層と、X軸方向と交差する第1、第2配線LL1、LL2と、交互に積層された複数の電極膜14及び絶縁膜を含む積層構造体Sbと、それに積層された選択ゲート電極SGbと、これらを貫通し下端が接続された第1及び第2選択部半導体ピラーSPb1,SPb2と、第4方向に延在する第3、第4配線LL3,LL4と、第4配線LL4は第2配線LL2に接続され、第3配線LL3の上に設けられ第3配線L3に接続された第5配線LL5と、を備える。

(もっと読む)

201 - 220 / 1,423

[ Back to top ]