Fターム[5F083LA12]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | 配線レイアウト (4,019) | ビット線 (1,534)

Fターム[5F083LA12]の下位に属するFターム

オープンビット線 (46)

折り返し(フォールディッド)ビット線 (43)

交差型(ツイスティッド)ビット線 (22)

Fターム[5F083LA12]に分類される特許

141 - 160 / 1,423

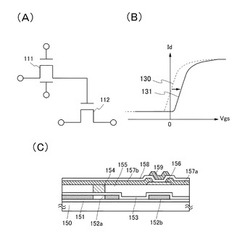

半導体装置及び半導体記憶装置

【課題】データの保持期間を長くする半導体装置又は半導体記憶装置を提供する。

【解決手段】一対の不純物領域を有する第1の半導体層152aと、第1の半導体層と同じ材料であり、第1の半導体層と離間する第2の半導体層152bと、第1、第2の半導体層の上に設けられた第1の絶縁層153と、第1の絶縁層153を介して第1の半導体層に重畳する第1の導電層154と、第1の絶縁層153を介して第1の導電層に重畳し、第1の半導体層と異なる材料である第3の半導体層156と、第1の導電層及び第3の半導体層に電気的に接続される第2の導電層157bと、第3の半導体層156に電気的に接続され、第2の導電層と同じ材料である第3の導電層157aと、第3の半導体層、第2の導電層、及び第3の導電層の上に設けられた第2の絶縁層158と、第2の絶縁層を介して第3の半導体層に重畳する第4の導電層159と、を含む。

(もっと読む)

記憶装置

【課題】高密度化および大容量化が可能な記憶装置を提供する。

【解決手段】基板11上に複数の平行なワード線WLと複数の平行な第1ビット線1BLとが互いに垂直な方向に設けられている。隣接する2本のワード線WLの間に、ビットコンタクト電極BCが設けられている。ビットコンタクト電極BCを挟んで隣接する2本のワード線WLのそれぞれを間にしてビットコンタクト電極BCと反対側に、ノードコンタクト電極NCが設けられている。ノードコンタクト電極NCは、接続層23を介して下部電極21に接続されている。下部電極21は、基板11の表面に平行な面内においてノードコンタクト電極NCの直上からビットコンタクト電極BCに近づく方向にずれた位置に設けられている。複数の第2ビット線2BLの各々は、第1ビット線1BLの両側のノードコンタクト電極NCに接続された下部電極21に重なっている。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】カーボンナノチューブを可変抵抗素子として用い消費電力の抑制とスイッチの誤作動の低減を両立した不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】実施形態の不揮発性半導体記憶装置の製造方法は、半導体基板9上に、下部電極を形成する工程と、前記下部電極の上にカーボンナノチューブを含む可変抵抗層11を形成する工程と、前記可変抵抗層に電子線或いは光子線を照射する照射工程と、前記照射工程の後に、前記可変抵抗層の上に上部電極を形成する工程とを含む。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】レンチ2内に埋め込まれた埋め込み絶縁膜3の一部を除去することで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1を形成し、空隙AG1は、制御ゲート電極8下に潜るようにしてトレンチ2に沿って連続して形成する。

(もっと読む)

半導体装置

【課題】配線の引き出し性が向上されているとともに、配線間の短絡などの電気的問題が生じるおそれが抑制されており、かつ、配線が形成される領域の省スペース化が図られた半導体装置を提供する。

【解決手段】半導体装置1が備える基板4上の所定の層内に、第1の配線3が複数本並べられて設けられている。各第1の配線3は、それらの並べられた方向に沿って一方の側から他方の側へ向かうに連れて長く延ばされて形成されているか、あるいは短く縮められて形成されている。それとともに、各第1の配線3は、隣接するそれぞれの一端部3aが並べられた方向と直交する方向において互いにずれた位置に配置されている。

(もっと読む)

強誘電体メモリおよびその動作方法

【課題】ワード線を昇圧せずにセル内のノードを電源電圧に駆動する。

【解決手段】強誘電体メモリは,複数のワード線と複数のプレート線と複数のビット線対と複数のチャージ線とメモリセルとを有する。メモリセルは,ワード線にゲートが接続されビット線対に第一のソース・ドレインがそれぞれ接続された一対の第一導電型MOSFETと,一対の第一導電型MOSFETの第二のソース・ドレインとプレート線との間にそれぞれ設けられた一対の強誘電体キャパシタと,一対の強誘電体キャパシタとチャージ線との間に設けられゲートとドレインとが交差接続された一対の第二導電型MOSFETとをそれぞれ有する。そして,チャージ線駆動回路は,読み出し動作時および書き込み動作時にチャージ線を電源電圧に駆動する。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】占有面積の増大を抑制した不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1領域、第2領域、及び複数のワード線を備える。第1領域は、電気的に書き換え可能な複数のメモリトランジスタを有する。第2領域は、第1領域の周辺に位置する。複数のワード線は、複数のメモリトランジスタのゲートに各々接続されている。複数のワード線は、各々、配線部、及び接続部を備える。配線部は、第1領域から第2領域に向かうように第1方向に延び且つ第1方向に直交する第2方向に所定距離をもって配列されている。接続部は、配線部から延びて第2領域に設けられ且つ積層方向に延びるコンタクトと電気的に接続されている。複数の接続部の端部は、第2方向に延びる直線に沿って形成されている。

(もっと読む)

埋め込み配線を備える基板、その製造方法、これを利用する半導体装置およびその製造方法

【課題】 低抵抗の埋め込み配線を備える基板の製造方法を提供する。

【解決手段】 始めに半導体用基板100の第1面S1上に導電層120を形成する。次に、導電層120をパターニングして第1方向に延長する線形の導電層パターン122を形成する。導電層120をパターニングするとき露出する半導体用基板100をエッチングして導電層パターン120の下部に第1方向に延長する線形の半導体パターン104を形成する。次に導電層パターン120および半導体パターン104上に絶縁層150を形成する。半導体用基板100の第1面S1側の絶縁層150が支持基板160と当接するように支持基板160上に配置する。次に半導体用基板100のイオン注入層102側の絶縁層150が露出するように半導体用基板100を除去する。これにより、導電層パターン120は、半導体パターン104の埋め込み配線として利用することができる。

(もっと読む)

3次元半導体記憶素子

【課題】優れた信頼性を有し、高集積化のために最適化された3次元半導体記憶素子が提供される。

【解決手段】本発明の素子によれば、積層構造体が基板上に配置されて第1の方向に延長される。積層構造体は交互に反復的に積層されたゲートパターン及び絶縁パターンを含む。垂直形活性パターンが積層構造体を貫通する。積層構造体は第1の部分及び第2の部分を含み、積層構造体の第2の部分は第1の方向と垂直である第2の方向に第1の部分より小さい幅を有する。積層構造体の第2の部分の横にストラッピングコンタクトプラグが配置されて、共通ソース領域と接触される。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去状態におけるセル電流の値の変動を抑制可能な不揮発性半導体記憶装置の提供。

【解決手段】基板の主面に平行な第1の方向に延びるよう区画された複数の素子領域111と、前記素子領域上に形成された複数のメモリセルを含むメモリセルアレイ領域121と、前記第1の方向に延びるよう形成された複数のビット線131とを備え、前記複数のビット線の同じ側の端部に電気的に接続されたセンスアンプ回路141と、前記素子領域上に、前記素子領域と前記ビット線とを電気的に接続するよう形成された複数のビット線コンタクトCBとを備える。前記メモリセルアレイ領域は、第1から第Nの領域(N≧2)を含み、第Kの領域(2≦K≦N)は、第K−1の領域よりも前記センスアンプ回路から遠い位置に位置し、前記第Kの領域内の前記ビット線コンタクトのコンタクト抵抗は、前記第K−1の領域内の前記ビット線コンタクトのコンタクト抵抗よりも低い。

(もっと読む)

抵抗変化型メモリ

【課題】 メモリの動作特性の向上を図る。

【解決手段】実施形態の抵抗変化型メモリは、ビット線BLとワード線WLと、第1エミッタ21と、第1ベース23と、第1コレクタ22とを有する、第1駆動型の第1バイポーラトランジスタ2と、第2エミッタ31と、第2ベース33と、第2コレクタ32とを有する第2駆動型の第2バイポーラトランジスタ3と、第1及び第2端子を有する抵抗変化型メモリ素子1と、を具備し、メモリ素子1の第1端子は第1及び第2エミッタ21,31に接続され、メモリ素子1の第2端子は、ビット線BLに接続され、第1及び第2ベース23,33はワード線WLに接続される。

(もっと読む)

半導体装置の製造方法

【課題】フラッシュメモリセルと低電圧動作トランジスタや高電圧動作トランジスタを集積化し、異種トランジスタを混載する半導体装置の製造法を提供する。

【解決手段】半導体装置の製造方法は、(a)トンネル絶縁膜、Fゲート電極膜、電極間絶縁膜を堆積したFゲート電極構造を形成し(b)ゲート絶縁膜を形成し(c)導電膜、エッチストッパ膜を堆積し(d)エッチストッパ膜、導電膜をエッチングした積層ゲート電極構造を形成し(e)積層ゲート電極構造の側壁上に第1絶縁膜を形成し(f)積層ゲート電極側壁上に第1サイドウォールスペーサ層を形成し(g)エッチストッパ層を除去し(h)他の領域の導電層から、ゲート電極構造を形成し(i)積層ゲート電極構造、ゲート電極構造側壁上に第2サイドウォールスペーサを形成し(j)希弗酸水溶液で半導体基板表面を露出し(k)半導体基板表面にシリサイド層を形成する。

(もっと読む)

半導体装置

【課題】半導体装置の省スペース化を実現する。

【解決手段】半導体基板5に、センスアンプが備えられた周辺回路領域Sとメモリセル領域Mとが区画形成され、メモリセル領域Mにおいて、半導体基板5の一面に形成されたトレンチ溝内に、ゲート絶縁膜を介しゲート電極を含む埋込ワード線9とその上に位置する埋込絶縁膜とが埋め込まれ、前記トレンチ溝に隣接する半導体基板5一面の表面領域に不純物拡散層が形成され、前記不純物拡散層が形成された領域上にはビット配線15が形成されており、ビット配線15が周辺回路領域Sまで延長され、周辺回路領域Sにおいてビット配線15が前記センスアンプを構成するMOSトランジスタのゲート電極Gとされていることを特徴とする半導体装置を採用する。

(もっと読む)

強誘電体メモリおよびその制御方法

【課題】セルデータ読み出しのシグナルマージンを向上させることができる強誘電体メモリおよびその制御方法を実現する。

【解決手段】本発明の実施形態における強誘電体メモリは、セルキャパシタとセルトランジスタとが並列接続された複数のメモリセルと、隣り合う2つのメモリセルにおいてセルキャパシタの下部電極同士または上部電極同士が接続されるよう複数のメモリセルが直列に接続されて、その一端がビット線(/BL、BL)に接続され、他端がプレート線(/PL0、PL0)に接続されたセルブロック(MB0、MB1)と、下部電極がプレート線(/PL0、PL0)に電気的に接続される場合と、上部電極がプレート線(/PL0、PL0)に電気的に接続される場合とでセルキャパシタの電極間にかかる電界が同じ方向に印加されるようにプレート線(/PL0、PL0)およびビット線(/BL、BL)を制御する制御回路11および12を有する。

(もっと読む)

結晶性酸化物半導体膜の作製方法

【課題】優れた結晶性を有する酸化物半導体膜を作製する。

【解決手段】酸化物半導体の膜を形成するに際し、基板を第1の温度以上第2の温度未満に加熱しつつ、基板の、典型的な長さが1nm乃至1μmの部分だけ、第2の温度以上の温度に加熱する。ここで、第1の温度とは、何らかの刺激があれば結晶化する温度であり、第2の温度とは、刺激がなくとも自発的に結晶化する温度である。また、典型的な長さとは、その部分の面積を円周率で除したものの平方根である。

(もっと読む)

半導体記憶装置

【課題】

駆動回路からメモリセルへの寄生抵抗や寄生容量の影響により、非選択セルへの熱ディスターブ、印加電圧のばらつき、読み出し時の記憶素子の劣化等の課題があった。

【解決手段】

電流により記憶情報が書き込まれる記憶素子と、当該記憶素子に接続される選択素子と、を有するメモリセル(MC)の上方または下方にキャパシタ(C)を設け、当該キャパシタに蓄積された電荷によって記憶素子に書き込みを行う。

(もっと読む)

装置

【課題】ボイドが存在しても高い信頼性を確保可能な配線構造を提案する。

【解決手段】実施形態に係わる装置は、第1の溝10を有する絶縁層13と、第1の溝10内に形成され、上部に凹部16を有する銅を含む第1の配線層15と、第1の配線層15の凹部16の内面上に形成され、少なくとも1つのグラフェンシートから構成されるグラフェン層17とを備える。

(もっと読む)

半導体記憶装置の評価方法

【課題】半導体記憶装置のトンネル絶縁膜の電荷分布を評価することが可能な半導体記憶装置の評価方法を提供する。

【解決手段】半導体記憶装置の評価方法は、浮遊ゲート型の半導体記憶装置の評価方法である。時間の対数の変化に対する前記半導体記憶装置のメモリセルの閾値電圧Vtの変化率に、ε*Cr*2k/Tox/qを乗じる。なお、εはトンネル絶縁膜の誘電率であり、Crは前記メモリセルのカップリング比であり、Toxは前記メモリセルのトンネル酸化膜の膜厚であり、kは電荷がデトラップする時の存在確率の減衰率でありk=(2mE/(h/2π)2)0.5と表され、mは電子の質量、 Eは前記トンネル絶縁膜のトラップのエネルギー準位、hはプランク定数、πは円周率である。これにより、前記メモリセルのトンネル絶縁膜中の電子濃度分布を求める。

(もっと読む)

可変抵抗素子、及び、不揮発性半導体記憶装置

【課題】 電極材料に対する制約が緩和され、製造プロセス上容易な可変抵抗素子、及び、当該可変抵抗素子を備えた不揮発性半導体記憶装置を提供する。

【解決手段】

可変抵抗素子2は、第1電極12aと第2電極14の間に抵抗変化層13、及び、第2電極と接する低抵抗層14を挟持して構成される。低抵抗層14は、抵抗変化層13を構成する金属酸化膜と同一の金属元素の酸化膜であり、且つその抵抗値が前記抵抗変化層よりも低くなるように低抵抗化する処理がされている。低抵抗層14は、例えば、金属酸化膜に不純物をドーピングし、キャリア濃度を増加させることにより形成される。或いは、低抵抗層14は、n型の金属酸化物の場合、金属酸化膜の酸素欠損濃度を抵抗変化層13よりも高濃度にすることにより形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】 260℃付近の高温下でのデータ保持特性に優れた不揮発性半導体記憶装置を提供する。

【解決手段】 第1電極2と、第2電極3と、両電極の間に介装された金属酸化物からなる可変抵抗体4を備え、第1電極2が可変抵抗体4とオーミック接合を形成する導電性材料で形成され、第2電極3が可変抵抗体4と非オーミック接合を形成する導電性材料で形成され、両電極間に電圧を印加することにより抵抗状態が2以上の異なる抵抗状態間で遷移し、当該遷移後の抵抗状態を不揮発的に保持する可変抵抗素子を備えて構成されたメモリセルを複数配列して、ユーザデータの格納用としたメモリセルアレイを備えた不揮発性半導体記憶装置において、メモリセルアレイがユーザデータの格納用として使用される前の使用前状態において、メモリセルアレイ内の全てのメモリセルの可変抵抗素子を、2以上の異なる抵抗状態の内の最も高抵抗の抵抗状態に高抵抗化する。

(もっと読む)

141 - 160 / 1,423

[ Back to top ]