Fターム[5F083LA12]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | 配線レイアウト (4,019) | ビット線 (1,534)

Fターム[5F083LA12]の下位に属するFターム

オープンビット線 (46)

折り返し(フォールディッド)ビット線 (43)

交差型(ツイスティッド)ビット線 (22)

Fターム[5F083LA12]に分類される特許

101 - 120 / 1,423

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

半導体記憶装置

【課題】低消費電力且つ省スペースな半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、異なる抵抗状態によってデータを記憶する複数のメモリセルからなるメモリセル層を有するメモリセルアレイと、第1配線及び第2配線を介して前記メモリセルにアクセスするアクセス回路とを備え、メモリセルは、第1極性の所定の電圧が印加されると抵抗状態が第1抵抗状態から第2抵抗状態に遷移し、第2極性の所定の電圧が印加されると抵抗状態が第2抵抗状態から第1抵抗状態に遷移し、アクセス回路は、選択したメモリセルに接続された第1配線及び第2配線に前記メモリセルのアクセスに必要な電圧を印加する共に、非選択の前記メモリセルに接続された第1配線及び第2配線の少なくとも一方をフローティング状態にして、選択したメモリセルにアクセスすることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】露光パターンのピッチの1/4のピッチのパターンを形成する方法でありながら、形成されたパターンの本数を4の倍数以外の数にする。

【解決手段】第2のパターンおよび第2のマスクパターンを覆うと共に第1の膜の上に第3の膜を形成する工程と、第3の膜をエッチバック処理することにより、第2のパターンおよび第2のマスクパターンの側壁に第1の側壁ラインパターンおよび第1の側壁マスクパターンをそれぞれ形成する工程と、第2のマスクパターンおよび第1の側壁マスクパターンを覆うように第3のマスクパターンを形成する工程と、第3のマスクパターンをマスクとし、第2のパターンを第1の側壁ラインパターンに対して選択的にエッチングして除去した後、第3のマスクパターンを除去する工程とを備えた。

(もっと読む)

半導体装置及びその製造方法

【課題】ビット線が直線状であり、かつセルトランジスタの長手方向がビット線方向に平行であり、さらにビット線がセルトランジスタと平面視で重複する位置に配線された半導体装置を提供する。

【解決手段】第1及び第2のコンタクトプラグ6a,6bの上面に第1の絶縁層10aを介して設けられ、かつ第1の不純物拡散層4aと第2の不純物拡散層4bとを結ぶ方向に延伸するビット線BLと、第1の絶縁層10aを貫通して設けられ、ビット線BLと第1のコンタクトプラグ6aとを電気的に接続するビット線コンタクトプラグと、ビット線BLの一方側面側の側方に第1の下部電極7aを有する第1のセルキャパシタと、ビット線BLと第1の下部電極7aとを絶縁する第1の絶縁膜8aと、第1の下部電極7aの下端と第2のコンタクトプラグ6bの側面とを電気的に接続する第1のコンタクト導体9aとを備える。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体記憶装置

【課題】メモリセルのセルサイズを縮小することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセル(12)と、複数の第1および第2の制御線(112,111)と、複数のワード線(104,105)とを備え、複数のメモリセルは、2つのメモリセルからなるメモリセルペア(10)を備え、各メモリセルペアは、第1および第2の拡散領域(101,102)を有し、ワード線(104)がゲートとなるMOSトランジスタ(15)と、記憶素子(109A,109B)と、第2および第3の拡散領域(102,103)を有し、ワード線(105)がゲートとなるMOSトランジスタ(18)とを備えており、第1の拡散領域(101)から第2の拡散領域(102)へ向かう方向と、第3の拡散領域(103)から第2の拡散領域(102)へ向かう方向とがそれぞれ、第1の制御線(112)に対して傾いている。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリストリングと選択トランジスタとの間にダミーメモリトランジスタを接続された不揮発性半導体記憶装置における適正な動作を担保する。

【解決手段】素子分離絶縁膜は、第1領域においては第1の高さを有する一方、第2領域においては第1の高さよりも高い第2の高さを有する。ダミーメモリトランジスタのメモリストリング側の第1の端部に隣接する素子分離絶縁膜は前述の第1の領域に形成され、ダミーメモリトランジスタの選択トランジスタ側の第2の端部に隣接する素子分離絶縁膜は前述の第2の領域に形成されている。

(もっと読む)

半導体記憶装置

【課題】1つの実施形態は、例えば、信号線の波形を観測するための検査用電極を容易に設けることができる半導体記憶装置を提供することを目的とする。

【解決手段】1つの実施形態によれば、メモリセルアレイと、複数の信号線と、複数の信号線引き出し部とを備えた半導体記憶装置が提供される。メモリセルアレイでは、複数のメモリセルが配列されている。複数の信号線は、複数のメモリセルに接続されている。複数の信号線引き出し部は、メモリセルアレイの周辺に配され、複数の信号線に接続されている。複数の信号線引き出し部のそれぞれは、プラグを電極として有する。プラグは、上面及び側面が保護膜で覆われている。

(もっと読む)

抵抗メモリ素子および関連する制御方法

【課題】電圧制御されたプログラム可能な抵抗層を有する抵抗メモリ素子とプログラミング方法を提供する。

【解決手段】参照面に平行な面に横たわり、参照面上の垂直な投影で上部電極投影を有する上部電極素子12と、参照面に平行な面に横たわり、参照面上の垂直な投影で下部電極投影を有する下部電極素子14と、上部電極素子12と下部電極素子14との間に挿入された可変性の抵抗率を有する活性層16を含む抵抗メモリ素子10において、上部電極投影と下部電極投影との間にオーバーラップ領域L3があり、オーバーラップ領域L3は少なくとも上部電極投影のコーナーおよび/または少なくとも下部電極投影のコーナーを含み、オーバーラップ領域L3の面積は、参照面上の、上部電極素子12と下部電極素子14の全投影面積の10%以下を構成する。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲート電極および当該選択ゲート電極に隣接する他のゲート電極間の間隔を所望の距離に調整できるようにした不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】複数本のラインパターンのうち選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてマスクした条件にて複数本のラインパターンの側壁面をスリミングし、選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてパターン間膜を埋込むと共にスリミングされたラインパターンの側壁面に沿ってパターン間膜を形成し、選択ゲート電極の形成領域のラインパターンをマスクした条件にて当該ラインパターン以外のラインパターンを除去しマスクされたラインパターンを残留させ、パターン間膜および残留したラインパターンをマスクとして第1膜を異方性エッチングし、第1膜をマスクとして導電膜をエッチングする不揮発性半導体記憶装置の製造方法を提供する。

(もっと読む)

記憶素子および記憶装置

【課題】低電圧および低電流動作時における繰り返し特性が向上した記憶素子および記憶装置を提供する。

【解決手段】下部電極10、記憶層20および上部電極30をこの順に積層した記憶素子1において、記憶層20は、2.8mΩcm以上1Ωcm未満の抵抗率を有するイオン源層21と、抵抗変化層22とを有する。これにより、低電圧または低電流パルスを印加した際の記録状態から消去状態への抵抗変化層の抵抗値の回復が改善され、繰り返し特性が向上する。

(もっと読む)

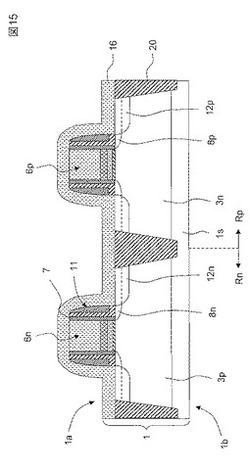

半導体装置及びその製造方法

【課題】本発明は、ボディ浮遊効果を抑制することが可能な半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成された埋め込み絶縁層2と、埋め込み絶縁層2上に形成された半導体層3とを備えるSOI構造の半導体装置であって、半導体層3は、第1導電型のボディ領域4、第2導電型のソース領域5及び第2導電型のドレイン領域6を有し、ソース領域5とドレイン領域6との間のボディ領域4上にゲート酸化膜7を介してゲート電極8が形成され、ソース領域5は、第2導電型のエクステンション層52と、エクステンション層52と側面で接するシリサイド層51を備え、シリサイド層51とボディ領域4との境界部分に生じる空乏層の領域に結晶欠陥領域12が形成されている。

(もっと読む)

半導体記憶装置

【課題】GIDLによるホールの発生効率を向上させることが可能な半導体記憶装置を提供する。

【解決手段】フィン3の両側にゲート絶縁膜5を介して設けられ、フィン3にチャネル領域を形成するゲート電極Gと、チャネル領域間のボディ領域にホールを閉じ込めるポテンシャルバリアを形成する不純物拡散層6と、チャネル領域を挟み込むようにしてフィン3に形成されたソース層S/ドレイン層Dとを備え、データ‘1’が書き込まれる際にゲート電圧が負電位かつ基板バイアス電圧およびドレイン電圧が正電位に設定される。

(もっと読む)

不揮発性半導体記憶装置及びフォーミング方法

【課題】フォーミング処理の時間を低減できる不揮発性半導体記憶装置を提供する。

【解決手段】複数の不揮発性メモリセルは、可変抵抗素子及び整流素子が直列接続されている。制御部は、第1のタイミングにおいて、Nを1以上の整数とするとき複数のワードラインからN本おきに第1のラインを多重選択して選択電位に設定するとともに、少なくとも多重選択されたワードラインに隣接する非選択のワードラインの電位を固定する。制御部は、第2のタイミングにおいて、上記の多重選択されたワードラインを浮遊状態にする。第2のタイミングは、第1のタイミングより後のタイミングである。制御部は、第3のタイミングにおいて、複数のビットラインから1本の第2のラインを選択してフォーミング電位に設定する。第3のタイミングは、第2のタイミングより後のタイミングである。

(もっと読む)

半導体メモリ素子及びその製造方法

【課題】垂直型トランジスタを形成する過程において、ゲートと接触する活性領域の面積を増加させてゲートの接触抵抗特性を改善し、チャネル幅を増加させる半導体メモリ素子及びその製造方法を提供する。

【解決手段】第1の方向に延長するように形成された下部ピラーと、下部ピラー上に第1の方向と垂直な第2の方向に突出するように形成された上部ピラー290と、下部ピラーの一側壁に配置された埋め込みビットライン接合領域265と、トレンチを一部埋め込む埋め込みビットライン280と、エッチング停止膜285a上に形成された少なくとも上部ピラーの外周側面の一部を露出するようにリセスされた第1の層間絶縁膜290と、第1の層間絶縁膜上に形成された第2の層間絶縁膜295と、側面の一部が露出した上部ピラーの外周側面を覆いつつ、埋め込みビットラインと相互交差するゲート320aとを備えるように形成される。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コンタクトとアクティブエリアとの間のショートマージンを確保できる半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板と、前記半導体基板の上層部分に形成され、前記上層部分を第1方向に延びる複数本のアクティブエリアに区画する複数本の素子分離絶縁体と、前記アクティブエリアに接続されたコンタクトと、を備える。そして、各前記アクティブエリアの上面のうち、前記第1方向における一部の領域には、前記第1方向に対して直交する第2方向において前記アクティブエリアの全体にわたって凹部が形成されている。前記第1方向において、隣り合う前記アクティブエリアにそれぞれ接続された2本の前記コンタクトの位置は相互に異なる。前記コンタクトは前記凹部の側面に接し、底面には接していない。

(もっと読む)

半導体記憶装置

【課題】擬似的に記憶容量を増加させる。

【解決手段】ダミービット線領域において半導体基板に対して垂直方向に延びる一対の柱状部およびその連結部に沿って形成されるメモリストリングを構成する第1シリコンピラーと、シャント領域において半導体基板に対して垂直方向に延びる一対の柱状部およびその連結部に沿って形成されるメモリストリングを構成する第2シリコンピラーと、第1シリコンピラーおよび第2シリコンピラーの一対の柱状部の一方に接続され、メモリストリングの上方に形成されたソース線と、第1シリコンピラーの一対の柱状部の他方に接続され、ソース線と同レベルに形成された第1配線、および第2シリコンピラーの一対の柱状部の他方に接続され、ソース線と同レベルに形成された第2配線と、を具備し、第1配線はダミービット線に接続され、第1配線および第2配線は同レベルで接続されている。

(もっと読む)

半導体装置

【課題】 電源遮断機能付きで記憶容量の増減変更を伴う設計が容易なSRAMマクロを有する半導体装置を提供する。

【解決手段】 本発明の半導体装置では、SRAMのメモリセルが複数配置されているメモリアレイと、メモリアレイへのデータの書き込みおよびメモリアレイからのデータの読み出しを行う第1の周辺回路と、メモリアレイおよび第1の周辺回路と電源線との接続を遮断するスイッチ群とを含むレイアウトの単位が複数配置されている。

(もっと読む)

101 - 120 / 1,423

[ Back to top ]