Fターム[5F083NA01]の内容

Fターム[5F083NA01]に分類される特許

2,141 - 2,160 / 3,470

半導体装置及びその製造方法

【課題】微細化加工において、コンタクトプラグとキャパシタの下部電極との接触界面抵抗を低下させ、歩留まりを向上させる構造の半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、半導体基板と、その表面に形成されたMOSトランジスタと、MOSトランジスタ上に設けられた第1の層間絶縁膜と、MOSトランジスタのゲート間において、第1の層間絶縁膜を貫通する第1の開口部に配置され、MOSトランジスタのソース及びドレインそれぞれに接続された多結晶シリコン膜のセルコンタクトプラグと、セルコンタクトプラグ上に設けられた第2の層間絶縁膜と、第2の層間絶縁膜を貫通する第2の開口部に配置され、平面視における面積が第2の開口部の面積より大きい突出部を有し、突出部の上に金属バリア層が形成された、多結晶シリコンのコンタクトプラグと、コンタクトプラグ上に設けられ、上部電極及び下部電極に誘電体が介挿されキャパシタとを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】DRAM素子の微細化を進めた場合における、周辺回路側のトランジスタの短チャネル効果を抑制すると共に、コンタクト抵抗を低減することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1と、半導体基板1の表面に形成されたMOSトランジスタTr2と、MOSトランジスタTr2のソース108A及びドレイン108Bにそれぞれ接続されるコンタクトプラグ11Aとを具備してなり、コンタクトプラグ11Aが、ソース108A及びドレイン108B上に形成されて不純物が拡散されたエピタキシャル成長層を含んでなることを特徴とする半導体装置を採用する。

(もっと読む)

半導体装置

【課題】SRAMやフラッシュメモリ等のメモリやロジックに用いられる、コンタクトや配線をできるだけ省略し、構造を簡略化することによって半導体装置の高集積化を図り、かつ、生産性を向上させるMOS型半導体装置を提供する。

【解決手段】MOS型半導体装置10では、半導体基板11と、半導体基板11にウェル領域12を備え、かつ、ゲート15とソース13/ドレイン14とを有し、ソース13の上部を形成するソース電極133が、ソース13を形成する拡散領域131を通過して、ウェル領域12又はボディ領域111に貫通していて、かつ、ドレイン14の上部を形成するドレイン電極は、ウェル領域12又はボディ領域111を貫通していない。

(もっと読む)

半導体装置及びその製造方法

【課題】MIM型のキャパシタを備える半導体装置の製造方法であって、MOSFETの特性低下を抑制しつつ、下地絶縁膜中の酸化性不純物の下部電極への拡散を抑制する。

【解決手段】ウエハ上にキャパシタ収容絶縁膜29を堆積するステップと、キャパシタ収容絶縁膜29を堆積したウエハを、予め所定温度に設定した加熱炉内に所定時間挿入し、キャパシタ収容絶縁膜29を緻密化するステップと、緻密化したキャパシタ収容絶縁膜29に形成したキャパシタ収容孔30内に、下部電極を構成する金属膜、容量絶縁膜、及び、上部電極を構成する金属膜を順次に堆積して、MIM型キャパシタを形成するステップと、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層を有する半導体装置の特性と製造歩留まりのバランスを向上させる。

【解決手段】半導体装置100においては、シリコン基板101に、容量素子を含むDRAM領域104と、ロジックNch領域102と、が設けられている。ロジックNch領域102に設けられたトランジスタの最小ゲート寸法は、DRAM領域104に設けられたトランジスタの最小ゲート寸法よりも小さい。DRAM領域104中の第一トランジスタ114の第一ソース・ドレイン領域113および第一ゲート電極117上にコバルトシリサイド層115が設けられている。また、ロジックNch領域102中の第二トランジスタ112の第二ソース・ドレイン領域103上および第二ゲート電極107上に、ニッケルシリサイド層105が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】積層ゲート電極の加工を容易にするNAND型フラッシュメモリ等の半導体装置およびその製造方法を提供する。

【解決手段】第1のゲート絶縁膜5上に浮遊ゲート電極FGとして機能し、素子分離領域Sbに対して自己整合的に構成されている第1の導電膜6、ONO膜等の第2のゲート絶縁膜7、制御ゲート電極として機能する第2の導電膜8を形成後、第1および第2の導電膜と第2のゲート絶縁膜7をゲート電極分離領域GVに沿って分離する。その後、第2の導電膜8の上に対してTi/TiN等によるバリアメタル膜9aにより下面および側面が覆われたタングステン等の金属層9bが積層されてなる第3の導電膜9が構成される。

(もっと読む)

半導体記憶装置

【課題】記憶部がDRAMによって構成されたTCAMを備えた半導体記憶装置において、プロセスコストを低減可能な半導体記憶装置を提供する。

【解決手段】不純物領域511および512に挟まれた領域にP型のウエル領域601が設けられ、当該ウエル領域601上に、ゲート絶縁膜GXを介してチャージライン402が設けられている。この、ゲート絶縁膜GXが、キャパシタC20のキャパシタ絶縁膜となり、ウエル領域601が電極キャパシタC20のストレージノードSN2として機能する。ウエル領域601の側面に接するようにP型の不純物領域512が設けられており、層間絶縁膜4を貫通して不純物領域512およびゲート配線405に達するように設けられたコンタクト部522により、ストレージノードSN2はトランジスタT22のゲート電極に電気的に接続される。

(もっと読む)

半導体装置の製造方法

【課題】強誘電体キャパシタが備えるキャパシタ誘電体膜の特性を向上させることが可能な半導体装置の製造方法を提供すること。

【解決手段】第1導電膜の上に、ゾル・ゲル法により強誘電体膜24を形成する工程と、強誘電体膜24上に第1導電性酸化金属膜25dを形成する工程と、第1導電性金属酸化膜25dに対して第1のアニールを行う工程と、第1導電性酸化金属膜25d上に第2導電性酸化金属膜25eを形成する工程と、第1導電膜23、強誘電体膜24、及び第2導電膜25をパターニングしてキャパシタを形成する工程とを有し、第1導電性酸化金属膜25dを形成する工程において、スパッタガスにおける酸素流量比が増大することにより強誘電体膜24の強誘電体特性が向上することを利用し、強誘電体特性を酸素流量比で調節する半導体装置の製造方法による。

(もっと読む)

半導体記憶装置

【課題】メモリセルの閾値電圧のばらつきを低減することによって不良ビット数を少なくする。

【解決手段】半導体記憶装置は、半導体層30と、半導体層の第1の表面に接するように形成されたチャージトラップ膜20と、半導体層の前記第1の表面に対して反対側の第2の表面に接するように形成されたゲート絶縁膜70と、チャージトラップ膜に接するように形成されたバックゲートBGと、ゲート絶縁膜に接するように形成されたゲート電極WLと、半導体層内に形成されたソース60およびドレイン40と、ドレインとソースとの間に設けられ、電気的に浮遊状態のボディ領域50とを備え、ソース、ドレインおよびゲート電極を含むメモリセルMCの閾値電圧またはドレイン電流は、ボディ領域内に蓄積された多数キャリアの数およびチャージトラップ膜にトラップされた電荷量によって変更される。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 素子分離絶縁膜の上部に形成される凹部を容易且つ確実に形成し、フローティングゲートの容量結合を効果的に防止する。

【解決手段】 素子分離絶縁膜30が、第1素子分離絶縁膜31と第2素子分離絶縁膜32の2つにより形成される。第1素子分離絶縁膜31は、素子分離溝13が平坦に埋まらず、窪み部31vが形成されるような厚さで、減圧CVD法によって全面堆積される。第2素子分離絶縁膜32としてのポリシラザン膜が窪み部31vを埋めるように全面塗布され、熱酸化により緻密化される。第1素子分離絶縁膜31と第2素子分離絶縁膜32は、CMP法により平坦化された後、第2素子分離絶縁膜32のエッチングレートの方が第1素子分離絶縁膜のそれよりも高いエッチング条件でエッチングされる。

(もっと読む)

リセスゲートを有する半導体素子の製造方法

【課題】バルブ型リセスパターンを形成するための側壁保護膜として熱酸化膜を形成するとき処理時間が増加し、厚さ調整が難しいことと、バルブ型リセスパターンにおいて第1リセス領域と第2リセス領域とのCDの差が大きい場合、シームが生じ、熱処理によってシームが移動して素子のリフレッシュ特性を低下させることとを防止可能な半導体素子の製造方法を提供する。

【解決手段】半導体基板51Bをエッチングして第1リセス領域55を形成するステップと、第1リセス領域55を備える半導体基板51Bの全面にプラズマ酸化膜を形成するステップと、プラズマ酸化膜をエッチングして第1リセス領域55の側壁に側壁保護膜56Aを形成するステップと、第1リセス領域55の底部を等方性エッチングして、第1リセス領域55よりも広い幅で、かつ、ラウンド形状の第2リセス領域57を形成するステップとを含む。

(もっと読む)

半導体装置とその製造方法

【課題】強誘電体キャパシタが備えるキャパシタ誘電体膜の特性を向上させることが可能な半導体装置とその製造方法を提供すること。

【解決手段】第1導電膜23の上に、少なくともゾル・ゲル法による成膜ステップを含む成膜方法により第1強誘電体膜24bを形成する工程と、第1強誘電体膜24bの上に、スパッタ法により第2強誘電体膜24cを形成する工程と、第2強誘電体膜24cの上に第2導電膜25を形成する工程と、第1導電膜23、第1、第2強誘電体膜24b、24c、及び第2導電膜25をパターニングして、下部電極23a、キャパシタ誘電体膜24a、及び上部電極25aを備えたキャパシタQを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】動作速度を低下させることなく、信号差を増大させることができ、かつ容易に製造することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板10と、半導体基板上に設けられた埋込み絶縁膜20と、埋込み絶縁膜上に設けられた半導体層30と、半導体層内に形成されたN型のソース層40と、半導体層内に形成されたN型のドレイン層50と、ソース層とドレイン層との間の半導体層に設けられ、電気的に浮遊状態であり、多数キャリアの蓄積状態によってデータを保持するボディ領域60と、ボディ領域上に設けられたゲート絶縁膜70と、ゲート絶縁膜上に設けられたゲート電極80と、ドレイン層の下にある半導体バルクの表面に設けられたP型の拡散層90とを備え、ボディ領域の下にある半導体バルクの表面はN型のままであることを特徴とする。

(もっと読む)

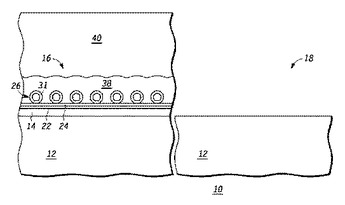

選択領域からナノクラスターを除去する方法

半導体素子を製造する方法は、不揮発性メモリ用の第1部分(16)と第1部分(16)を除く第2部分(18)とを有する半導体層(12)を備えた基板(12)を提供することを含む。半導体層上には第1の誘電体層(14)が形成される。第1の誘電体層上でプラズマ窒化が行なわれる。第1部分上には第1の複数のナノクラスター(20)が、第2部分上には第2の複数のナノクラスター(28)が形成される。第2の複数のナノクラスターは除去され、半導体層上に第2の誘電体層(38)が形成され、第2の誘電体層上に導電層(40)が形成される。  (もっと読む)

(もっと読む)

半導体装置

【課題】 セルの面積を大きくすることなく、かつ動作の安定性に優れた半導体装置を提供する。

【解決手段】 メモリセルが、第1及び第2のインバータ、及び第1及び第2の転送トランジスタを含む。第1の転送トランジスタは、半導体基板の表層部のうち一部の領域に形成された第1のウェル内に配置されている。第1のインバータの抵抗素子は、第1の転送トランジスタのドレインと第1のウェルとに逆方向バイアスを印加したときのリーク電流密度が、第1の転送トランジスタのソースと第1のウェルとに同一電圧の逆方向バイアスを印加したときのリーク電流密度よりも大きくなるような第1の高リーク電流構造を含む。第1の高リーク電流構造は、ドレインと第1のウェルとの界面に配置され、第1導電型の不純物濃度が第1のウェルの不純物濃度よりも高い高濃度領域を含む。第2の高リーク電流構造も同様の構成である。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】微細化によるメモリセル間の干渉を低減し、かつ、オフ状態でのリーク電流を抑制した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板10と、半導体基板に形成された複数の素子分離領域STIと、隣り合う素子分離領域間に設けられた素子形成領域AAであって、素子分離領域の隣接方向の断面において素子形成領域の側部の一部分の幅が該素子形成領域の上面の幅よりも狭い窪みCを有する素子形成領域と、素子形成領域上に設けられた第1のゲート絶縁膜20と、第1のゲート絶縁膜上に設けられたフローティングゲート電極FGと、フローティングゲート電極上に設けられた第2のゲート絶縁膜30と、第2のゲート絶縁膜上に設けられたコントロールゲート電極CGとを備え、素子分離領域の隣接方向の断面においてフローティングゲート電極の上辺の幅がフローティングゲート電極の下辺の幅よりも狭い。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】周辺領域に形成される素子分離膜の高さを下げるように形成して、ゲートパターニング後に実施する素子分離膜のエッチング工程を容易にするフラッシュメモリ素子の製造方法を提供する。

【解決手段】セル領域と周辺領域を設けた半導体基板100上にゲート絶縁膜102、第1導電膜104、そして窒化膜106を形成す。それら各膜と半導体基板100の一部をエッチングしてトレンチを形成する。このトレンチに素子分離膜108を形成し、セル領域と周辺領域における素子分離膜108を第一次エッチングする。続いて、窒化膜106を除去し、セル領域における素子分離膜108を第二次エッチングし、セル領域と周辺領域における素子分離膜108を第三次エッチングする。

(もっと読む)

半導体記憶装置

【課題】データ“0”と“1”との信号差が大きく、歩留まりの高い半導体記憶装置を提供する。

【解決手段】ソース層S、ドレイン層D、および該ソース層と該ドレイン層との間に設けられたフローティングボディBを含み、該フローティングボディ内の多数キャリアの数によってデータを記憶するメモリセルMCと、メモリセルのゲートに接続され第1の方向に延びるワード線WLと、メモリセルのドレイン層に接続され第1の方向とは異なる第2の方向に延びるビット線BLと、メモリセルのソース層に接続され第1の方向に延びるソース線SLと、ビット線に接続され選択されたメモリセルに記憶されたデータを検出するセンスアンプS/Aと、多数キャリア数が少ないことを示すバイナリデータをメモリセルに書き込むときに、メモリセルにチャネルが形成されるようにワード線に電圧を印加し、かつ逆方向にソース線の電圧を遷移させるドライバWLD,SLDとを備える。

(もっと読む)

不揮発性メモリ素子およびその製造方法

【課題】フローティングゲート用導電膜の形成時に、素子分離膜内のボイドの生成を抑制することで、セルとセル間の漏れ電流を防止して信頼性の高い不揮発性メモリ素子およびその製造方法を提供する。

【解決手段】活性領域および素子分離領域の半導体基板100上に第1絶縁膜112が形成される。また、活性領域の第1絶縁膜上にはフローティングゲートと素子分離領域の第1絶縁膜112上に、活性領域よりも低く形成されるギャップフィル導電膜114bを有し、該ギャップフィル導電膜の上部に形成された第2絶縁膜126および第3絶縁膜128からなる素子分離膜130が形成される。また、フローティングゲートおよび素子分離膜上に誘電体膜が形成され、この誘電体膜の上部にコントロールゲートが形成される。その場合に、第2絶縁膜126を含む半導体基板100の上部には、ギャップフィルのための第3絶縁膜128が形成され、好ましくは第3絶縁膜128は高密度プラズマ方式(HDP)を用いて埋め込み特性のよいHDP酸化膜で形成する。

(もっと読む)

半導体素子の素子分離膜形成方法

【課題】トレンチ内にボイドが形成される場合でも、ボイドが基板の高さより低いところに形成されて後続の工程に影響しないうえ、幅の狭いトレンチに素子分離膜を容易に形成して工程の再現性を確保すること。

【解決手段】半導体基板100の素子分離領域に第1トレンチ114を形成する段階と、第1トレンチ114の側壁にスペーサ116を形成する段階と、スペーサ116間の素子分離領域に、第1トレンチ114より幅が狭くて深い第2トレンチ118を形成する段階と、第2トレンチ118の側壁及び底面に第1酸化膜115を形成する段階と、第1トレンチ114を絶縁膜102で充填する段階とを含むことを特徴とする。

(もっと読む)

2,141 - 2,160 / 3,470

[ Back to top ]