Fターム[5F083PR39]の内容

Fターム[5F083PR39]に分類される特許

81 - 100 / 687

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと第2のトランジスタと容量素子とを各々含む複数のメモリセルをマトリクス状に配置し、メモリセルの一と他のメモリセルとを接続する配線(ビット線とも呼ぶ)と、第1のトランジスタにおけるソース電極またはドレイン電極と、が、第2のトランジスタにおけるソース電極またはドレイン電極を介して電気的に接続した構成とした半導体装置を提供する。これにより、第1のトランジスタにおけるソース電極またはドレイン電極と、第2のトランジスタにおけるソース電極またはドレイン電極と、を異なる配線に接続する場合と比較して配線の数を削減することができるため、半導体装置の集積度を向上させることができる。

(もっと読む)

不揮発性半導体記憶装置、及び不揮発性半導体記憶装置の製造方法

【課題】抵抗変化素子を含む不揮発性メモリセルの配置密度を容易に向上できる不揮発性半導体記憶装置、及び不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板の表面に略垂直な第1の面内に並んでおり、前記半導体基板の表面に沿ってそれぞれ延びた複数の第1のラインと、前記第1の面に沿った第2の面内に並んでおり、前記半導体基板の表面に略垂直にそれぞれ延びた複数の第2のラインと、前記複数の第1のラインと前記複数の第2のラインとの交差する位置に配された複数の不揮発性メモリセルとを備え、前記複数の不揮発性メモリセルのそれぞれは、抵抗変化素子と、前記抵抗変化素子に直列に接続された整流素子とを含み、前記抵抗変化素子は、前記第1の面と前記第2の面との間を前記複数の第2のラインに跨って連続的に延びた抵抗変化膜における前記第1のラインと前記第2のラインとの交差する部分を含む。

(もっと読む)

半導体装置の製造方法

【課題】サイドウォールスペーサを利用してリソグラフィー解像限界未満のパターンと任意の寸法のパターンとが混在するパターンを形成する。

【解決手段】窒化シリコン層3上に形成されたポリシリコン層をパターニングすることによってメモリセルアレイ領域1aにスリミングされたサイドウォールコア4を形成する。次に、サイドウォールコア4の少なくとも側面を覆う酸化シリコン層6、ポリシリコン層を順に成膜し、ポリシリコン層をエッチバックすることによって埋込ハードマスク7を形成する。その後、酸化シリコン層6をエッチングすることにより、サイドウォールコア4又は埋込ハードマスク7と重ならないメモリセルアレイ領域1a内の窒化シリコン層3と、目合わせモニタマーク8bと重なる周辺回路領域1b内の窒化シリコン層3を露出させ、被エッチング部材としての窒化シリコン層3をパターニングする。

(もっと読む)

半導体装置

【課題】不揮発性記憶装置と揮発性記憶装置の双方のメリットを享受する記憶装置を提供する。

【解決手段】基板または基板上に設けられた第1のトランジスタと、第1のトランジスタよりも上に設けられた第2のトランジスタを有する半導体装置において、第1のトランジスタと第2のトランジスタの少なくとも一部を重畳させ、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極を電気的に接続させる。第1のトランジスタとしてはシリコン単結晶により設けられたものが好ましく、第2のトランジスタとしてはオフ電流が極端に小さい酸化物半導体により設けられたものが好ましい。

(もっと読む)

半導体装置およびその製造方法

【課題】製造コストを増加させることなく、高アスペクト比のキャパシタ下部電極を保持するサポート膜構造を提供する。

【解決手段】サポート膜で保持された下部電極40を備えるキャパシタを複数含む半導体装置であって、前記サポート膜は、前記下部電極の高さ方向に複数層(例えば、16及び20の2層)形成され、各層のサポート膜は、前記下部電極間を接続するライン形状のパターンを有し、該パターンの延在方向が、隣接する二層間でそれぞれ異なることを特徴とする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、第1の信号線と、第2の信号線と、ワード線と、ソース線とビット線との間に、接続されたメモリセルと、ビット線と電気的に接続された第1の駆動回路と、第1の信号線と電気的に接続された第2の駆動回路と、第2の信号線と電気的に接続された第3の駆動回路と、ワード線及びソース線と電気的に接続された第4の駆動回路と、を有し、第1のトランジスタは、酸化物半導体以外の半導体材料を用いて構成され、第2のトランジスタは、酸化物半導体材料を含んで構成される。

(もっと読む)

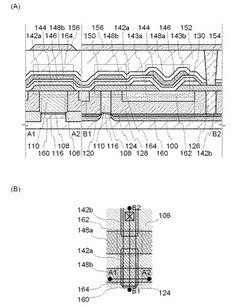

埋め込み絶縁層を貫いて半導体層間に接触を有するデバイス、およびこのデバイスの製造プロセス

【課題】簡潔な方法で、SeOI基板上の半導体デバイスの半導体領域に接続するラインを提供すること。

【解決手段】第1の側面によると、本発明は埋め込み絶縁層(3、BOX)によってベース基板(2)から隔離された半導体材料の薄い層(1)を含むSeOI(Semiconductor−On−Insulator)基板上に作製された半導体デバイスに関し、デバイスは、薄い層内に第1の伝導領域(1、D1、S、E)と、ベース基板内に第2の伝導領域(5、BL、SL、IL)とを含み、接触(I1、I2、IN、IP)は絶縁層を貫通して第1の領域と第2の領域を接続する。第2の側面によると、本発明は第1の側面に関する半導体デバイスの製作プロセスに関する。

(もっと読む)

キャパシタ、該キャパシタを備える半導体装置および半導体装置の製造方法

【課題】アスペクト比の高い電極を上下に接続して、静電容量の大きいキャパシタを形成する際、電極間の剥離を防止し、電極の倒壊を抑制する。

【解決手段】導電膜を外壁に有する下部電極30と、該下部電極の導電膜に対して、容量絶縁膜を介して形成された上部電極とを有するキャパシタにおいて、下部電極は少なくとも2層の積層構造であって、該積層構造は、下層側電極18に設けた掘り込み部に上層側電極22の底部が埋め込まれた構造であるキャパシタ。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】非オーミック性素子と抵抗変化層とを組み合わせたクロスポイント型構成において充分な電流容量を確保し、安定な作動が可能な不揮発性半導体記憶装置を提供する。

【解決手段】下層電極配線15を含む基板11上に形成された層間絶縁層16と、下層電極配線上の層間絶縁層に形成されたコンタクトホールと、下層電極配線15上に形成された非オーミック性素子17と、コンタクトホール中に埋め込まれ、非オーミック性素子17上に形成された抵抗変化層22と、抵抗変化層22と接続し、層間絶縁層16上に形成された上層電極配線23とを備え、非オーミック性素子17は、複数層の半導体層の積層構成、金属電極体層と半導体層との積層構成または金属電極体層と絶縁体層との積層構成のうちの半導体層又は絶縁体層を含む少なくとも1層はコンタクトホールより大きな形状を有し、コンタクトホール中に積層構成のその他の層が埋め込み形成されている。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的とする。

【解決手段】チャネル形成領域と、第1のゲート絶縁層と、第1のゲート電極と、第1のソース電極及び第1のドレイン電極と、を有する第1のトランジスタと、酸化物半導体層と、第2のソース電極及び第2のドレイン電極と、第2のゲート絶縁層と、第2のゲート電極と、を有する第2のトランジスタと、第2のソース電極または第2のドレイン電極の一方と、第2のゲート絶縁層と、第2のゲート絶縁層上に第2のソース電極または第2のドレイン電極の一方と重畳するように設けられた電極と、を有する容量素子と、を有し、第1のゲート電極と、第2のソース電極又は第2のドレイン電極の一方とは電気的に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】3次元レイアウトトランジスタにおいて、隣接するピラー間のビットラインを1本にして、微細化を図る。

【解決手段】隣接した第1および第2の半導体ピラー間に第1の絶縁膜7を介して形成されたビットライン8と、第1の半導体ピラーの側面および第1のビットライン上に形成され、第1のビットラインと第1の半導体ピラーとを電気的に接続する導電体10と、を備える半導体装置の製造方法において、導電体10を接続する第1の半導体ピラーの側面の第1の絶縁膜7を除去するため、第2の半導体ピラー側面に保護膜を残し、ビットライン8上の第1の絶縁膜7を選択的に除去する、あるいは第2の半導体ピラー側面に保護膜を残す際にビットライン8上の第1の絶縁膜7を除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】第1の領域中の層間絶縁膜を湿式エッチングにより除去する際に、使用する薬液が第2の領域に浸透することを防止する。これにより、第2の領域の特性の劣化がない、高性能の半導体装置を提供する。

【解決手段】第1の領域と、第1の領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた第2の領域と、を有する半導体装置。第1の領域は、導電性を有する第1の膜によって構成された第1の電極を有する。第1の領域中の第1の電極の表面は、第2の膜で覆われていない。ガードリングは、凹状の溝の内壁を覆う第1の膜と、凹状の溝の内部において少なくとも第1の膜の表面の一部を覆う絶縁性の第2の膜を有する。

(もっと読む)

凹型電極を有するキャパシタを備えるメモリデバイスを形成する方法

【解決手段】 凹型電極を有するMIMキャパシタを備えるメモリデバイスを形成する方法を説明する。一実施形態によると、凹型電極を有するMIMキャパシタを形成する方法は、底部を形成している下側部分および側壁を形成している上側部分によって画定される孔部を形成する段階を備える。当該方法は、孔部内に下側電極層を成膜して、下側電極層上に電気絶縁層を成膜して、電気絶縁層上に上側電極層を成膜して、MIMキャパシタを形成する段階を備える。当該方法は、MIMキャパシタの上側部分を除去して、下側電極層および上側電極層の上面を露出させて、下側電極層および上側電極層のうち一方を選択的にエッチングして、下側電極層および上側電極層のうち一方に凹部を形成する段階を備える。このようにして形成される凹部によって、上側電極および下側電極を互いから分離して、両電極間に電流漏れ経路が形成される可能性を低くする。 (もっと読む)

半導体素子及びその製造方法

【課題】キャパシタ間の誘電物質を互いに分離することのできる半導体素子及びその製造方法を提供する。

【解決手段】下部電極コンタクトプラグ120を含む半導体基板100上に誘電膜220の吸着防止層140を蒸着してキャパシタの間の誘電膜を互いに分離することにより、隣接したキャパシタのバイアス(bias)から影響を受けなくなり、セルのリフレッシュ特性が改善する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】電極に挟み込まれる強誘電体膜を特性のばらつきなく形成することのできる半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板Sと、半導体基板S上に形成された一対のソース/ドレイン拡散層11を有するセルトランジスタTと、セルトランジスタTに接続された強誘電体キャパシタCとを備える。セルトランジスタT及び強誘電体キャパシタCにより1つのメモリセルが構成される。強誘電体キャパシタCは、半導体基板Sの表面に垂直な方向を長手方向として延びる電極31と、電極31の側面に接するように設けられた強誘電体膜32と、半導体基板Sの表面に垂直な方向を長手方向として延び且つ電極31との間に強誘電体膜32を挟み込むように設けられた電極31とを備える。強誘電体膜32は、有機材料により構成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜を除去するエッチング中に、異常エッチングを防止する。エッチング工程において加わる水圧や風圧によりガードリングの形状が変形して剥離し、欠陥が発生することを防止する。

【解決手段】半導体装置は、メモリセル領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた周辺回路領域と、ガードリング及び周辺回路領域上に設けられた支持体膜と、周辺回路領域内に設けられたコンタクトプラグとを有する。ガードリングとコンタクトプラグは、同一の導電材料から構成される。

(もっと読む)

相変化構造物、相変化物質層の形成方法、相変化メモリ装置及び相変化メモリ装置の製造方法

【課題】抵抗マージンと維持特性を確保しながら優秀なステップカバレッジ、又は、ギャップフィル特性を有する、微小サイズの相変化物質層パターンをHARS(High_Aspect_Ratio_Structure、高縦横比構造)内に含む相変化構造物を提供すること。

【解決手段】相変化構造物はHARSを部分的に満たし、第1相変化物質を含む第1相変化物質層パターン、及び前記HARSの残りを満たし、前記第1相変化物質と相異なる組成を有する第2相変化物質を含む。インサイチュリフローメカニズムを通じてHARSを欠陥なく充分に満たす相変化物質層パターンを形成する。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトランジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

可変抵抗メモリ装置及びその製造方法

【課題】可変抵抗メモリ装置及びその製造方法を提供する。

【解決手段】可変抵抗メモリ装置及びその製造方法を提供する。基板上に複数の下部電極を構成し、前記下部電極を露出し、第1方向に延長されるトレンチを含む第1層間絶縁膜を構成し、前記第1層間絶縁膜上に前記第1方向と交差する第2方向に延長される上部電極を構成し、前記トレンチ内に前記上部電極の側壁にアライメントされる側壁を有する可変抵抗パターンを形成する。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

81 - 100 / 687

[ Back to top ]