Fターム[5F083ZA02]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリセルと周辺回路の関係 (1,873) | リセス構造 (33)

Fターム[5F083ZA02]に分類される特許

1 - 20 / 33

半導体装置の製造方法及び半導体装置

半導体装置及びその製造方法

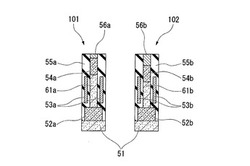

【課題】セルトランジスタが形成された第1領域と周辺回路トランジスタが形成された第2領域を有する半導体装置において、周辺回路トランジスタの上部拡散層のチャネル領域への導電型ドーパントの分布を抑制し、セルトランジスタと周辺回路トランジスタにおける駆動電流の閾値電圧依存性のばらつきを低減する半導体装置の製造方法を提供する。

【解決手段】基板を第1領域と第2領域に区分し、前記第2領域の前記基板上面を前記第1領域の前記基板上面より所定の掘り下げ量だけ掘り下げる工程と、前記第1領域に第1ピラーを、前記第2領域に前記第1ピラーよりも高さが前記掘り下げ量だけ低い第2ピラーを各々形成する工程と、前記第1及び第2ピラーの下部に第1拡散層を、上部に第2拡散層を各々形成する工程と、前記第1及び第2ピラーと前記第1拡散層の側面にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜側面にゲート電極を形成する工程とを有する。

(もっと読む)

記憶装置、及び半導体装置

【課題】高速動作を実現できる記憶装置、或いは、リフレッシュ動作の頻度が低減できる記憶装置を提供する。

【解決手段】セルアレイ101の内部において、メモリセル100に接続された配線に、駆動回路102から電位の供給が行われる。さらに、駆動回路102上にセルアレイ101が設けられており、セルアレイ101が有する複数の各メモリセル100は、スイッチング素子と、スイッチング素子により電荷の供給、保持、放出が制御される容量素子とを有する。そして、スイッチング素子として用いられるトランジスタは、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体を、チャネル形成領域に含んでいる。

(もっと読む)

不揮発性メモリ装置及びその製造方法

【課題】半導体基板のセル領域と周辺回路領域との間に段差をなくして、工程を容易かつ単純にしつつ、特に、コンタクトナットオープン(Contact not open)、下部構造物に対するアタック(Attack)などを防止し、工程歩留まり及び信頼性を向上させることができる不揮発性メモリ装置及びその製造方法を提供すること。

【解決手段】周辺回路領域及び該周辺回路領域より高さが低いセル領域を有する半導体基板と、該半導体基板の前記セル領域上に配置され、複数の層間絶縁膜及び複数の制御ゲート電極が交互に積層された制御ゲート構造物と、該制御ゲート構造物が形成された前記半導体基板の前記セル領域を覆う第1の絶縁膜と、該第1の絶縁膜上の選択ゲート電極と、前記半導体基板の前記周辺回路領域上の周辺回路素子とを備えることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】金属コンタクトを安定に形成できる半導体装置の製造方法を提供する。

【解決手段】セル領域にストレージノードコンタクトプラグ12を形成するステップと、第1の層間絶縁膜17を形成するステップと、周辺領域の第1の層間絶縁膜上に第1のビットライン20を形成するステップと、第2の層間絶縁膜22を形成するステップと、周辺領域の第2の層間絶縁膜上に第1のビットラインと電気的に接続された第2のビットライン25を形成するステップと、セル領域のストレージノードコンタクトプラグの上面を露出させるステップと、セル領域にストレージノードコンタクトプラグと接するキャパシタを形成するステップと、キャパシタが形成された基板の全面に第3の層間絶縁膜31を形成するステップと、周辺領域の第3の層間絶縁膜を貫通して第2のビットラインに接する金属コンタクト33を形成するステップとを含むことを特徴とする。

(もっと読む)

半導体メモリおよびその製造方法

【課題】素子分離トレンチ内の絶縁膜のエッチングとアライメントトレンチ内の絶縁膜のエッチングとを、1つのマスクを用いて同時に行える構造の半導体メモリを提供する。

【解決手段】シリコン基板2には、メモリセル領域70およびアライメントマーク領域80が設定されている。メモリセル領域70には、シリコン基板2の表層部に、アクティブ領域30を分離する素子分離トレンチ21が形成されている。アライメントマーク領域80には、シリコン基板2の表層部に、マスク合わせのためのアライメントトレンチ82が形成されている。素子分離トレンチ21内には、素子分離トレンチ21間のアクティブ領域30が突出するように、絶縁物(酸化膜)23が素子分離トレンチ21の深さ方向途中まで埋め込まれている。一方、アライメントトレンチ82内には、絶縁物23がアライメントトレンチ82の深さ方向途中まで埋め込まれている。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】デバイス特性の劣化を抑制した不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】第1ダミーセル領域121に設けられた素子分離絶縁層33と、第2ダミーセル領域122に設けられた素子分離絶縁層43と、第1ダミーセル領域121と第2ダミーセル領域122との間の境界に位置する素子分離絶縁層51とを備える。素子分離絶縁層33の上面は、浮遊電極層32の上面よりも低い高さに位置する。素子分離絶縁層43の上面は、浮遊電極層42の上面と同じ高さに位置する。浮遊電極層32に隣接する素子分離絶縁層51の上面の端部は、浮遊電極層32の上面よりも低い高さに位置する。素子分離絶縁層51の上面は、浮遊電極層32の側面から浮遊電極層42の側面へ向かって上昇する傾斜TLを有する。

(もっと読む)

半導体装置の製造方法

【課題】同一の半導体基板上にゲート絶縁膜の膜厚の異なる半導体素子領域を容易に形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板に素子分離絶縁膜を形成することにより、第1の半導体素子領域と第2の半導体素子領域とを画定する工程と、前記第2の半導体素子領域と前記第2の半導体素子領域を囲う前記素子分離絶縁膜を覆い、前記第1の半導体素子領域と前記第1の半導体素子領域を囲う前記素子分離絶縁膜を露出させるマスクを形成する工程と、前記マスクを用いて、前記第1の半導体素子領域を囲う前記素子分離絶縁膜をエッチングする工程と、前記素子分離絶縁膜をエッチングする工程の後、前記マスクを用いて前記第1の半導体素子領域に対して異方性エッチングを行う工程と、前記マスクを除去する工程と、前記マスクを除去した後に熱酸化により第1の半導体素子領域と第2の半導体素子領域とにゲート酸化膜を形成する工程と、を有することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

半導体装置の製造方法

【課題】メモリセル領域と高電圧トランジスタとの高濃度不純物拡散領域を同時にイオン注入で形成し、且つ高電圧トランジスタ側の方が浅くなるように形成する。

【解決手段】シリコン基板1にメモリセル領域にゲート電極MG、SGを形成し(図3(b))、周辺回路領域にゲート電極PG(図3(c))を形成する。周辺回路領域のゲート電極PGは、高電圧トランジスタについては厚い膜厚のゲート絶縁膜11が形成されている。ゲート絶縁膜11を残した状態でTEOS酸化膜9を成膜し、スペーサ加工をする。この時、スペーサ9aを形成すると共に、ゲート絶縁膜11を半分程度エッチングして11aとする。TEOS酸化膜10を形成後に高濃度不純物拡散領域1d、1eをイオン注入で深さd1、d2で形成する。高電圧トランジスタについてはゲート絶縁膜11aを介して行うので、浅く形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】PMOS領域における素子分離膜のライナー窒化膜の除去を行う従来技術による問題を解決した半導体装置およびその製造方法を提供すること。

【解決手段】半導体装置の製造方法は、基板20をエッチングして複数のトレンチを形成するステップと、複数のトレンチ内に第1絶縁膜24Aを埋め込んで第1素子分離膜を形成するステップと、一部のトレンチ(CELL又はPERI NMOS領域のトレンチ)内に埋め込まれた第1絶縁膜24Aをリセスするステップと、リセスされたトレンチの全面にライナー膜26A、27Aを形成するステップと、ライナー膜26A、27Aが形成されたトレンチ内に第2絶縁膜28を埋め込んで第2素子分離膜を形成するステップとを含む。

(もっと読む)

半導体装置の製造方法

【課題】不揮発性半導体記憶装置の周辺回路領域において用いられる高耐圧トランジスタの特性及び信頼性を向上させることのできる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、シリコン基板3に周辺回路の高耐圧トランジスタHVTr用のゲート絶縁膜29を形成する工程と、ゲート絶縁膜29上にゲート電極HVGを形成する工程と、ゲート電極HVGの両側部のシリコン基板3上に位置するゲート絶縁膜29を剥離する工程と、不純物拡散領域30を形成する工程と、ゲート電極HVG及び不純物拡散領域30の表面に亘りシリコン酸化膜を堆積する工程と、シリコン酸化膜をエッチングしてゲート電極HVGの側壁部に形成されるとともに、シリコン基板3表面に延長するようにスペーサ22を形成する工程と、スペーサ22の表面にシリコン窒化膜23を形成する工程とを備える。

(もっと読む)

半導体装置

【課題】ワード線引き出し部におけるワード線とシリコン基板との距離をセルアレイ領域内に比して長く確保でき、耐圧を向上させることができる半導体装置を提供する。

【解決手段】セルアレイ領域の半導体基板14上には、第1の膜厚を持つトンネル酸化膜18、及び第1ゲート電極を有するメモリセルトランジスタが形成されている。周辺回路領域の半導体基板14上には、第1の膜厚より厚い第2の膜厚を持つゲート酸化膜を有する高電圧トランジスタが形成される。ワード線3は、メモリセルトランジスタの第1ゲート電極に接続され、ワード線引き出し領域の半導体基板14上に延伸している。ワード線引き出し領域において、半導体基板14とワード線3との間には、第1の膜厚より厚く、第2の膜厚より薄い第3の膜厚を持つシリコン酸化膜15が形成されている。

(もっと読む)

相変化メモリのFEOLプロセスフローにおける回路及びメモリアレイの相対的高さの制御

【課題】相変化メモリのFEOLプロセスフローにおいて回路及びメモリアレイの相対的高さを制御する。

【解決手段】PCM部分が埋設されたCMOS論理部分は、ゲート酸化物及びポリシリコンゲートの厚みで測定されたゲート構造体の高さだけリセス加工されて、CMOS論理部分とPCM部分との平坦性を与える。

(もっと読む)

固体撮像素子、その動作方法、その製造方法及びデジタルカメラ

【課題】受光量に十分に対応(ばらつきの少ない線形又は非線形)したデータを不揮発性メモリセルから読み出すことができる固体撮像装置を実現すること。

【解決手段】入射光を受け信号電荷を発生させる受光素子と、一端が受光素子に接続され、他端が検出ノードに接続された第1のトランジスタと、一端が検出ノードに接続された第2のトランジスタと、検出ノードに制御ゲート又は一端が接続された電荷蓄積層を有するメモリセルトランジスタと、を具備することを特徴とする固体撮像装置。

(もっと読む)

半導体メモリ

【課題】半導体装置のプロセスマージンを向上できる。

【解決手段】本発明の例の半導体メモリは、同一の配線層内に設けられる2つのビット線BL1,BL2と、メモリセルアレイ内に設けられるアクティブ領域AA2と、アクティブ領域AA2と交差する2つのワード線WL1,WL2と、ゲートがワード線WL1,WL2にそれぞれ接続されアクティブ領域AA2上に設けられる第1及び第2のトランジスタTr1,Tr2と、ビット線BL2とトランジスタTr1のソース/ドレインとに接続される第1の抵抗性記憶素子MTJ1と、ビット線BL2とトランジスタTr2のソース/ドレインとに接続される第2の抵抗性記憶素子MTJ2と、ビット線BL1と2つのトランジスタTr1,Tr2の共有ノードに接続され、ワード線WL1,WL2間に配置される配線層M2とを具備し、アクティブ領域AA2はメモリセルアレイの一端から他端まで延在する。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の垂直方向より水平方向により厚くシリコン酸化膜又はシリコン窒化膜が形成される異方性酸化又は異方性窒化を行う半導体装置の製造方法を提供する。

【解決手段】半導体基板1の表面に、側壁部及び底部を有する素子分離溝を形成する工程と、マイクロ波、高周波、又は電子サイクロトロンのいずれかによって発生したプラズマに含まれる酸化性イオン、又はプラズマに含まれる窒化性イオンを、半導体基板1に所定電圧を印加して素子分離溝の側壁部及び素子分離溝の底部に供給し、素子分離溝の側壁部及び素子分離溝の底部に対して異方性酸化を行う、又は異方性窒化を行う工程とを備えることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜形成後のフォトリソグラフィ工程におけるプロセスマージンの低下を抑制することができる半導体装置の製造方法を提供する。

【解決手段】シリコン半導体基板11内においてメモリセルトランジスタが形成されるシリコン基板面を、セレクトゲートトランジスタが形成されるシリコン基板面より低く形成する。続いて、シリコン基板面上にMONOS絶縁膜13を形成する。さらに、シリコン基板面上に、MONOS絶縁膜13より膜厚が薄いゲート絶縁膜14を形成し、MONOS絶縁膜13とゲート絶縁膜14の表面を同じ高さにする。さらに、MONOS絶縁膜13上及びゲート絶縁膜14上にゲート電極15、17を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 深さの異なる複数のコンタクトホールを有する構造であって、簡易な製造工程の下、基板に対するエッチングダメージを招来せず製造することが可能な半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板1上の一部領域にフィールド酸化膜2を形成し、その後にフィールド酸化膜2の一部領域をエッチング処理して凹部構造32を形成し、その後に、少なくとも凹部構造32の底面を覆うように、フィールド酸化膜2の上層に下部電極7、酸化膜8、上部電極9を形成し、ソース・ドレイン拡散領域6を形成し、その後に全面に層間絶縁膜10を堆積する。そして、拡散領域6の上面が露出するように拡散領域6の上方領域に係る層間絶縁膜10をエッチングして第1コンタクトホール11aを形成すると共に、上部電極9の上面が露出するように凹部構造32の上方領域に係る層間絶縁膜10をエッチングすることで第2コンタクトホール11cを形成する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】SOI上に形成された半導体層上にメモリセルユニット及び選択トランジスタを形成した場合に、選択トランジスタの特性を向上できる半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板11と、前記半導体基板上に設けられ開口を有する絶縁層12と、前記絶縁層上に設けられた半導体層13とを備える支持基板15と、前記半導体層上に設けられ、電流経路が直列接続された複数のメモリセルを備えるメモリセルユニットMUと、前記メモリセルユニットに隣接し、かつ前記開口の上方の前記半導体層上に配置され、前記開口の上方の前記半導体層の上面は前記メモリセルユニットが設けられた前記半導体層よりも中央近傍のみが低いリセス構造17を有し、前記リセス構造上における前記半導体層上に設けられたゲート絶縁膜18と、前記ゲート絶縁膜上に設けられたゲート電極19とを備えた選択トランジスタSTとを具備する。

(もっと読む)

厚さが減少した半導体素子、これを採用する電子製品及びその製造方法

【課題】厚さが減少した半導体素子、これを採用する電子製品及びその製造方法を提供する。

【解決手段】この半導体素子の製造方法は第1及び第2活性領域を有する半導体基板を準備する工程を含む。前記第1活性領域に第1ゲートパターン及び第1不純物領域を含む第1トランジスタを形成する。前記第2活性領域に第2ゲートパターン及び第2不純物領域を含む第2トランジスタを形成する。前記第1トランジスタ上に第1導電性パターンを形成する。前記第1導電性パターンの少なくとも一部と前記第2ゲートパターンの少なくとも一部は前記半導体基板の上部表面から同一距離に配置される。前記第1導電性パターンは前記第2ゲートパターンを形成する間に形成される。

(もっと読む)

1 - 20 / 33

[ Back to top ]