半導体装置の製造方法

【課題】金属コンタクトを安定に形成できる半導体装置の製造方法を提供する。

【解決手段】セル領域にストレージノードコンタクトプラグ12を形成するステップと、第1の層間絶縁膜17を形成するステップと、周辺領域の第1の層間絶縁膜上に第1のビットライン20を形成するステップと、第2の層間絶縁膜22を形成するステップと、周辺領域の第2の層間絶縁膜上に第1のビットラインと電気的に接続された第2のビットライン25を形成するステップと、セル領域のストレージノードコンタクトプラグの上面を露出させるステップと、セル領域にストレージノードコンタクトプラグと接するキャパシタを形成するステップと、キャパシタが形成された基板の全面に第3の層間絶縁膜31を形成するステップと、周辺領域の第3の層間絶縁膜を貫通して第2のビットラインに接する金属コンタクト33を形成するステップとを含むことを特徴とする。

【解決手段】セル領域にストレージノードコンタクトプラグ12を形成するステップと、第1の層間絶縁膜17を形成するステップと、周辺領域の第1の層間絶縁膜上に第1のビットライン20を形成するステップと、第2の層間絶縁膜22を形成するステップと、周辺領域の第2の層間絶縁膜上に第1のビットラインと電気的に接続された第2のビットライン25を形成するステップと、セル領域のストレージノードコンタクトプラグの上面を露出させるステップと、セル領域にストレージノードコンタクトプラグと接するキャパシタを形成するステップと、キャパシタが形成された基板の全面に第3の層間絶縁膜31を形成するステップと、周辺領域の第3の層間絶縁膜を貫通して第2のビットラインに接する金属コンタクト33を形成するステップとを含むことを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造技術に関し、特に、金属コンタクト(Metal contact)を備える半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置を構成する要素のうち、金属コンタクト(Metal contact)は、金属配線と、金属配線の下部に形成された構造物(例えば、ゲート、ビットライン、キャパシタの上部電極など)との間を連結するためのコンタクトであって、主に、セル領域を除いた周辺領域に形成するようになる。

【0003】

一方、半導体装置が高集積化するに伴い、それぞれの構成要素が占める面積も次第に減少している。特に、DRAMでは、キャパシタが占める面積が減少するにつれて、十分な静電容量を確保するために、キャパシタの高さを益々増加させている。このため、周辺領域に形成される金属コンタクトの高さが増加し、金属コンタクトを形成するためのコンタクトホールの形成工程時、コンタクトナットオープン(contact not open)が生じたり、金属コンタクトの抵抗が増加するという問題が生じる。

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明は、上記のような従来技術の問題を解決するために提案されたものであって、その目的は、金属コンタクトを安定に形成できる半導体装置の製造方法を提供することにある。

【課題を解決するための手段】

【0005】

そこで、上記の目的を達成するための本発明に係る半導体装置の製造方法は、基板のセル領域にストレージノードコンタクトプラグを形成するステップと、前記基板上に第1の層間絶縁膜を形成するステップと、前記周辺領域の第1の層間絶縁膜上に第1のビットラインを形成するステップと、前記第1の層間絶縁膜上に第2の層間絶縁膜を形成するステップと、前記周辺領域の第2の層間絶縁膜上に前記第1のビットラインと電気的に接続された第2のビットラインを形成するステップと、前記第2の層間絶縁膜をエッチングして前記セル領域のストレージノードコンタクトプラグの上面を露出させるステップと、前記セル領域にストレージノードコンタクトプラグと接するキャパシタを形成するステップと、前記キャパシタが形成された基板の前面に第3の層間絶縁膜を形成するステップと、前記周辺領域の第3の層間絶縁膜を貫通して前記第2のビットラインに接する金属コンタクトを形成するステップと、前記第3の層間絶縁膜上に前記金属コンタクトと接する金属配線を形成するステップとを含むことを特徴とする。

【発明の効果】

【0006】

上述した課題解決手段に基づく本発明は、周辺領域のビットラインが複層構造を有するように、第1のビットライン及び第2のビットラインで形成することにより、金属コンタクトの高さを減少させることができる。また、制限された面積内で半導体装置が求める静電容量を確保するために、キャパシタの高さ(すなわち、ストレージノードの高さ)を増加させても第1の層間絶縁膜及び第2の層間絶縁膜の高さを調節する方法によって金属コンタクトの高さを減少させることができる。これにより、本発明は、金属コンタクトのためのコンタクトホールの形成工程時、コンタクトナットオープンが生じたり、金属コンタクトの抵抗が増加することを防止できるという効果がある。さらに、コンタクトホールの形成工程に対する工程難易度を減少させ、工程マージンを増加させることができるという効果がある。

【0007】

なお、本発明は、周辺領域のビットラインが複層構造を有するので、半導体装置の集積度が増加するにつれてビットラインが形成される空間が減少しても、周辺領域のビットラインを容易に実現できるという効果がある。

【図面の簡単な説明】

【0008】

【図1A】本発明の第1の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【図1B】本発明の第1の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【図1C】本発明の第1の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【図1D】本発明の第1の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【図1E】本発明の第1の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【図1F】本発明の第1の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【図2A】本発明の第2の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【図2B】本発明の第2の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【図2C】本発明の第2の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【図2D】本発明の第2の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【発明を実施するための形態】

【0009】

以下、本発明の属する技術分野における通常の知識を有した者が本発明の技術的思想を容易に実施できる程度に詳細に説明するために、本発明の最も好ましい実施形態を添付図面を参照して説明する。後述する本発明は、金属配線と、その下部構造物とを連結する金属コンタクト(Metal contact)を安定に形成できる半導体装置の製造方法を提供する。

【0010】

図1A〜図1Fは、本発明の第1の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【0011】

図1Aに示すように、セル領域と周辺領域を有して所定の構造物(例えば、素子分離膜、埋め込みゲートなど)が形成された基板11のセル領域にストレージノードコンタクトプラグ12を形成し、周辺領域には、周辺ゲート16を形成する。周辺ゲート16は、周辺ゲート絶縁膜13、周辺ゲート電極14、及び周辺ゲートハードマスク膜15が順次積層された積層構造物で形成することができる。

【0012】

次に、基板11の前面にストレージノードコンタクトプラグ12及び周辺ゲート16を覆う第1の層間絶縁膜17を形成する。第1の層間絶縁膜17は、酸化膜、窒化膜、及び酸化窒化膜からなる群より選ばれたいずれかで形成することができる。

【0013】

次いで、周辺領域の第1の層間絶縁膜17及び周辺ゲートハードマスク膜15を選択的にエッチングして周辺ゲート電極14を露出させる第1のコンタクトホール18を形成した後、第1のコンタクトホール18に導電物質を埋め込んで第1のビットラインコンタクトプラグ19を形成する。

【0014】

続いて、第1の層間絶縁膜17上に第1のビットラインコンタクトプラグ19と接する第1のビットライン20を形成する。

【0015】

図1Bに示すように、第1のビットライン20を備える構造物の表面に沿って第1のエッチング停止膜21を形成する。第1のエッチング停止膜21は、第1の層間絶縁膜17に対してエッチング選択比を有する物質で形成する。一例として、第1の層間絶縁膜17を酸化膜で形成した場合、第1のエッチング停止膜21は窒化膜で形成する。両者のエッチングレートは異なる。

【0016】

次に、第1のエッチング停止膜21上に第2の層間絶縁膜22を形成する。第2の層間絶縁膜22は、酸化膜、窒化膜、及び酸化窒化膜からなる群より選ばれたいずれかで形成することができ、第1のエッチング停止膜21に対してエッチング選択比を有する物質で形成する。一例として、第1のエッチング停止膜21を窒化膜で形成した場合、第2の層間絶縁膜22は酸化膜で形成する。

【0017】

次いで、周辺領域の第2の層間絶縁膜22及び第1のエッチング停止膜21を選択的にエッチングして第1のビットライン20を露出させる第2のコンタクトホール23を形成した後、第2のコンタクトホール23に導電物質を埋め込んで第2のビットラインコンタクトプラグ24を形成する。

【0018】

続いて、第2の層間絶縁膜22上に第2のビットラインコンタクトプラグ24と接する第2のビットライン25を形成する。

【0019】

図1Cに示すように、第2の層間絶縁膜22上に周辺領域を覆い、セル領域を露出するハードマスクパターン35を形成する。ハードマスクパターン35は、セルオープンマスク(cell open mask)を用いて形成することができる。ハードマスクパターンは、アモルファス炭素膜(Amorphous Carbon Layer)またはシリコンリーチカーボン膜(Si−rich carbon)とシリコン酸化窒化膜(SiON)とが積層された積層膜で形成することができる。このとき、シリコン酸化窒化膜は、反射防止膜として作用する。

【0020】

次に、ハードマスクパターン35をエッチングバリアとしてセル領域の第2の層間絶縁膜22、第1のエッチング停止膜21、及び第1の層間絶縁膜17の一部をエッチングし、ストレージノードコンタクトプラグ12の上面を露出させる。このとき、エッチング工程は、第1のエッチング停止膜21でエッチングが止まるようにオーバーエッチングを十分に行った後、第1のエッチング停止膜21及び第1の層間絶縁膜17の一部をエッチングしてストレージノードコンタクトプラグ12を露出させる。

【0021】

エッチング工程は、ドライエッチング法またはウェットエッチング法を利用して行うか、またはドライエッチング法とウェットエッチング法とを混用して行うことができる。ドライエッチング法を利用する場合には、フッ化炭素ガス(CxFy、1≦x≧5、1≦y≧8)またはフッ化メタンガス(CxHyFz、1≦x≧3、1≦y≧4、0≦z≧5)を用いて行うことができ、エッチング特性(エッチング比、エッチング速度など)を調節するために、フッ化炭素ガスまたはフッ化メタンガスにAr、He、Xe、O2、CO、COS、N2、H2、HBr、Cl2、SiCl4、SF6、及びNF3からなる群より選ばれたいずれか1つまたは2つ以上を添加して行うことができる。ウェットエッチング法を利用する場合には、BOE(Buffered Oxide Etchant)溶液またはフッ酸(HF)溶液を用いて行うことができる。

【0022】

次に、ハードマスクパターン35を除去する。

【0023】

図1Dに示すように、構造物の表面に沿って第2のエッチング停止膜26を形成した後、第2のエッチング停止膜26上にモールド膜27を形成する。モールド膜27は、酸化膜、窒化膜、及び酸化窒化膜からなる群より選ばれたいずれかで形成することができ、第2のエッチング停止膜26に対してエッチング選択比を有する物質で形成する。モールド膜27は、セル領域と周辺領域との間の段差を考慮して、流動性絶縁膜で形成することが好ましい。流動性絶縁膜としては、BPSG(Boro−Phospho Silicate Glass)、PSG(Phospho Silicate Glass)、SOD(Spin On Dielectric)、シリコンリーチカーボン膜などを用いることができる。

【0024】

次いで、第2のビットライン25上の第2のエッチング停止膜26が露出するまで平坦化工程を行う。このとき、平坦化工程を化学的機械的研磨法を利用して行うことができる。

【0025】

続いて、セル領域のモールド膜27及び第2のエッチング停止膜26を選択的にエッチングしてストレージノードコンタクトプラグ12を露出させるストレージノードホール28を形成する。ストレージノードホール28を形成するためのエッチング工程は、ストレージノードホール28の側壁が垂直なプロファイルを有するように、C3F8、C4F6、C4F8またはC5F8のようなフッ化炭素ガス(CxFy、xは3〜5、yは5〜8)をメインエッチングガスとして用い、CH2F2、CH3FなどのCHxFyガス(xは1〜5、yは1〜8)、COS、O2、SiCl4及びCH4からなる群より選ばれたいずれか1つまたは2つ以上を添加して行うことができる。また、プラズマを安定化させると同時に、エッチング選択比を増加させるために、Ar、Xe、He等の不活性ガスをさらに添加して行うことができる。

【0026】

一方、ストレージノードホール28の高さによってストレージノードの高さが決定されるところ、モールド膜27に対する平坦化工程を行った後、モールド膜27上に絶縁膜をさらに形成してストレージノードホール28の高さを増加させることもできる。

【0027】

図1Eに示すように、ストレージノードホール28の内部にストレージノード29を形成する。ストレージノード29は、図面に示されているように、シリンダー型で形成するか、またはピラー型で形成することができる。

【0028】

次に、ウェットディップアウト(wet dip out)工程を行ってモールド膜27を除去する。ウェットディップアウトは、BOE溶液またはフッ酸溶液を用いて行うことができる。ウェットディップアウトを行う過程で第2のエッチング停止膜26によって下部構造物が損傷することを防止することができる。

【0029】

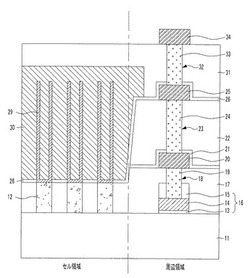

図1Fに示すように、ストレージノード29の表面に誘電膜(図示せず)を形成した後、ストレージノード29を覆うプレート電極30を形成する。これにより、セル領域にキャパシタが形成される。

【0030】

次に、プレート電極30が形成された基板11の前面に第3の層間絶縁膜31を形成する。第3の層間絶縁膜31は、酸化膜、窒化膜、及び酸化窒化膜からなる群より選ばれたいずれかで形成することができる。

【0031】

次いで、周辺領域の第3の層間絶縁膜31及び第2のエッチング停止膜26を選択的にエッチングして第2のビットライン25を露出させる第3のコンタクトホール32を形成した後、第3のコンタクトホール32に導電物質を埋め込んで金属コンタクト33を形成する。

【0032】

続いて、第3の層間絶縁膜31上に金属コンタクト33と接する金属配線34を形成する。

【0033】

上述した本発明の第1の実施形態に係る半導体装置の製造方法は、周辺領域のビットラインが複層構造を有するように、第1のビットライン及び第2のビットライン20、25で形成することにより、金属コンタクト33のための第3のコンタクトホール32の高さを減少させてコンタクトナットオープンが生じたり、金属コンタクト33の抵抗が増加することを防止することができる。また、第3のコンタクトホール32の形成工程に対する工程難易度を減少させ、工程マージンを増加させることができる。参考までに、従来にはストレージノード29の高さの分だけの層間絶縁膜を一度にエッチングして金属コンタクト33のためのコンタクトホールを形成するため、コンタクトナットオープンが生じたり、金属コンタクトの抵抗が増加するという問題が生じ、コンタクトホールが高縦横比を有するため、工程難易度が高く、工程マージンを確保するのが難しかった。

【0034】

また、周辺領域のビットラインが複層構造を有するので、半導体装置の集積度が増加するにつれてビットラインが形成される空間が減少しても、周辺領域のビットラインを容易に実現することができる。

【0035】

図2A〜図2Dは、本発明の第2の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【0036】

図2Aに示すように、本発明の第1の実施形態の図1A〜図1Dに示されたものと同様な方法によってセル領域と周辺領域を有し、所定の構造物(例えば、素子分離膜、埋め込みゲートなど)が形成された基板61のセル領域にストレージノードコンタクトプラグ62、第1のモールド膜77、及び第1のストレージノードホール78を形成し、周辺領域に周辺ゲート66、第1のビットライン70、第2のビットライン75を形成する。

【0037】

ここで、図示していない図面符号「63」は周辺ゲート絶縁膜、「64」は周辺ゲート電極、「65」は周辺ゲートハードマスク膜、「67」は第1の層間絶縁膜、「68」は第1のコンタクトホール、「69」は第1のビットラインコンタクトプラグ、「71」は第1のエッチング停止膜、「72」は第2の層間絶縁膜、「73」は第2のコンタクトホール、「74」は第2のビットラインコンタクトプラグ、「76」は第2のエッチング停止膜を示す。

【0038】

図2Bに示すように、第1のストレージノードホール78の内部に第1のストレージノード79を形成する。このとき、第1のストレージノード79はピラー型で形成する。

【0039】

次に、第1のモールド膜77上に第2のモールド膜80を形成する。第2のモールド膜80は、第1のモールド膜77と同じ物質で形成することができる。

【0040】

次いで、セル領域の第2のモールド膜80を選択的にエッチングして第1のストレージノード79を露出させる第2のストレージノードホール81を形成した後、第2のストレージノードホール81の内部に第2のストレージノード82を形成する。このとき、第2のストレージノード82は、ピラー型で形成するか、またはシリンダー型で形成することができる。

【0041】

第2のストレージノードホール81を形成するためのエッチング工程は、第2のストレージノードホール81の側壁が垂直なプロファイルを有するように、C3F8、C4F6、C4F8またはC5F8のようなフッ化炭素ガス(CxFy、xは3〜5、yは5〜8)をメインエッチングガスとして用い、CH2F2、CH3FなどのCHxFyガス(xは1〜5、yは1〜8)、COS、O2、SiCl4及びCH4からなる群より選ばれたいずれか1つまたは2つ以上を添加して行うことができる。また、プラズマを安定化させると同時に、エッチング選択比を増加させるために、Ar、Xe、Heなどの不活性ガスをさらに添加して行うことができる。

【0042】

図2Cに示すように、ウェットディップアウト(wet dip out)工程を行って第1のモールド膜及び第2のモールド膜77、80を同時に除去する。ウェットディップアウトは、BOE溶液またはフッ酸溶液を用いて行うことができる。ウェットディップアウトを行う過程において第2のエッチング停止膜76によって下部構造物が損傷することを防止することができる。

【0043】

図2Dに示すように、第1のストレージノード及び第2のストレージノード79、82の表面に誘電膜(図示せず)を形成した後、第1のストレージノード及び第2のストレージノード79、82を覆うプレート電極84を形成する。これにより、セル領域に本発明の第1の実施形態よりさらに大きい静電容量を有するキャパシタが形成される。

【0044】

次に、プレート電極84が形成された基板61の前面に第3の層間絶縁膜85を形成する。第3の層間絶縁膜85は、酸化膜、窒化膜、及び酸化窒化膜からなる群より選ばれたいずれかで形成することができる。

【0045】

次いで、周辺領域の第3の層間絶縁膜85及び第2のエッチング停止膜76を選択的にエッチングして第2のビットライン75を露出させる第3のコンタクトホール86を形成した後、第3のコンタクトホール86に導電物質を埋め込んで金属コンタクト87を形成する。

【0046】

続いて、第3の層間絶縁膜85上に金属コンタクト87と接する金属配線88を形成する。

【0047】

上述した本発明の第2の実施形態に係る半導体装置の製造方法は、周辺領域のビットラインが複層構造を有するように、第1のビットライン及び第2のビットライン70、75で形成することにより、金属コンタクト87のための第3のコンタクトホール86の高さを減少させることができる。また、制限された面積内で半導体装置が求める静電容量を確保するために、ストレージノードを第1のストレージノード及び第2のストレージノード79、82で形成して、高さを増加させても第1の層間絶縁膜及び第2の層間絶縁膜67、72の高さを調節する方法によって金属コンタクト87のための第3のコンタクトホール86の高さを減少させることができる。これにより、第3のコンタクトホール86の形成工程時、コンタクトナットオープンが生じたり、金属コンタクト87の抵抗が増加することを防止することができる。さらに、第3のコンタクトホール68の形成工程に対する工程難易度を減少させ、工程マージンを増加させることができる。

【0048】

また、周辺領域のビットラインが複層構造を有するので、半導体装置の集積度が増加するにつれてビットラインが形成される空間が減少しても周辺領域のビットラインを容易に実現することができる。

【0049】

本発明の技術思想は、上記好ましい実施形態によって具体的に記述されたが、上記の実施形態は、その説明のためのものであり、その制限のためのものでないことに注意すべきである。また、本発明の技術分野の通常の専門家であれば、本発明の技術思想の範囲内で様々な実施形態が可能であることが理解できるであろう。

【符号の説明】

【0050】

11 基板

12 ストレージノードコンタクトプラグ

13 周辺ゲート絶縁膜

14 周辺ゲート電極

15 周辺ゲートハードマスク膜

16 周辺ゲート

17 第1の層間絶縁膜

18 第1のコンタクトホール

19 第1のビットラインコンタクトプラグ

20 第1のビットライン

21 第1のエッチング停止膜

22 第2の層間絶縁膜

23 第2のコンタクトホール

24 第2のビットラインコンタクトプラグ

25 第2のビットライン

26 第2のエッチング停止膜

27 モールド膜

28 ストレージノードホール

29 ストレージノード

30 プレート電極

31 第3の層間絶縁膜

32 第3のコンタクトホール

33 金属コンタクト

34 ビットライン

【技術分野】

【0001】

本発明は、半導体装置の製造技術に関し、特に、金属コンタクト(Metal contact)を備える半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置を構成する要素のうち、金属コンタクト(Metal contact)は、金属配線と、金属配線の下部に形成された構造物(例えば、ゲート、ビットライン、キャパシタの上部電極など)との間を連結するためのコンタクトであって、主に、セル領域を除いた周辺領域に形成するようになる。

【0003】

一方、半導体装置が高集積化するに伴い、それぞれの構成要素が占める面積も次第に減少している。特に、DRAMでは、キャパシタが占める面積が減少するにつれて、十分な静電容量を確保するために、キャパシタの高さを益々増加させている。このため、周辺領域に形成される金属コンタクトの高さが増加し、金属コンタクトを形成するためのコンタクトホールの形成工程時、コンタクトナットオープン(contact not open)が生じたり、金属コンタクトの抵抗が増加するという問題が生じる。

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明は、上記のような従来技術の問題を解決するために提案されたものであって、その目的は、金属コンタクトを安定に形成できる半導体装置の製造方法を提供することにある。

【課題を解決するための手段】

【0005】

そこで、上記の目的を達成するための本発明に係る半導体装置の製造方法は、基板のセル領域にストレージノードコンタクトプラグを形成するステップと、前記基板上に第1の層間絶縁膜を形成するステップと、前記周辺領域の第1の層間絶縁膜上に第1のビットラインを形成するステップと、前記第1の層間絶縁膜上に第2の層間絶縁膜を形成するステップと、前記周辺領域の第2の層間絶縁膜上に前記第1のビットラインと電気的に接続された第2のビットラインを形成するステップと、前記第2の層間絶縁膜をエッチングして前記セル領域のストレージノードコンタクトプラグの上面を露出させるステップと、前記セル領域にストレージノードコンタクトプラグと接するキャパシタを形成するステップと、前記キャパシタが形成された基板の前面に第3の層間絶縁膜を形成するステップと、前記周辺領域の第3の層間絶縁膜を貫通して前記第2のビットラインに接する金属コンタクトを形成するステップと、前記第3の層間絶縁膜上に前記金属コンタクトと接する金属配線を形成するステップとを含むことを特徴とする。

【発明の効果】

【0006】

上述した課題解決手段に基づく本発明は、周辺領域のビットラインが複層構造を有するように、第1のビットライン及び第2のビットラインで形成することにより、金属コンタクトの高さを減少させることができる。また、制限された面積内で半導体装置が求める静電容量を確保するために、キャパシタの高さ(すなわち、ストレージノードの高さ)を増加させても第1の層間絶縁膜及び第2の層間絶縁膜の高さを調節する方法によって金属コンタクトの高さを減少させることができる。これにより、本発明は、金属コンタクトのためのコンタクトホールの形成工程時、コンタクトナットオープンが生じたり、金属コンタクトの抵抗が増加することを防止できるという効果がある。さらに、コンタクトホールの形成工程に対する工程難易度を減少させ、工程マージンを増加させることができるという効果がある。

【0007】

なお、本発明は、周辺領域のビットラインが複層構造を有するので、半導体装置の集積度が増加するにつれてビットラインが形成される空間が減少しても、周辺領域のビットラインを容易に実現できるという効果がある。

【図面の簡単な説明】

【0008】

【図1A】本発明の第1の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【図1B】本発明の第1の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【図1C】本発明の第1の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【図1D】本発明の第1の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【図1E】本発明の第1の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【図1F】本発明の第1の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【図2A】本発明の第2の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【図2B】本発明の第2の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【図2C】本発明の第2の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【図2D】本発明の第2の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【発明を実施するための形態】

【0009】

以下、本発明の属する技術分野における通常の知識を有した者が本発明の技術的思想を容易に実施できる程度に詳細に説明するために、本発明の最も好ましい実施形態を添付図面を参照して説明する。後述する本発明は、金属配線と、その下部構造物とを連結する金属コンタクト(Metal contact)を安定に形成できる半導体装置の製造方法を提供する。

【0010】

図1A〜図1Fは、本発明の第1の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【0011】

図1Aに示すように、セル領域と周辺領域を有して所定の構造物(例えば、素子分離膜、埋め込みゲートなど)が形成された基板11のセル領域にストレージノードコンタクトプラグ12を形成し、周辺領域には、周辺ゲート16を形成する。周辺ゲート16は、周辺ゲート絶縁膜13、周辺ゲート電極14、及び周辺ゲートハードマスク膜15が順次積層された積層構造物で形成することができる。

【0012】

次に、基板11の前面にストレージノードコンタクトプラグ12及び周辺ゲート16を覆う第1の層間絶縁膜17を形成する。第1の層間絶縁膜17は、酸化膜、窒化膜、及び酸化窒化膜からなる群より選ばれたいずれかで形成することができる。

【0013】

次いで、周辺領域の第1の層間絶縁膜17及び周辺ゲートハードマスク膜15を選択的にエッチングして周辺ゲート電極14を露出させる第1のコンタクトホール18を形成した後、第1のコンタクトホール18に導電物質を埋め込んで第1のビットラインコンタクトプラグ19を形成する。

【0014】

続いて、第1の層間絶縁膜17上に第1のビットラインコンタクトプラグ19と接する第1のビットライン20を形成する。

【0015】

図1Bに示すように、第1のビットライン20を備える構造物の表面に沿って第1のエッチング停止膜21を形成する。第1のエッチング停止膜21は、第1の層間絶縁膜17に対してエッチング選択比を有する物質で形成する。一例として、第1の層間絶縁膜17を酸化膜で形成した場合、第1のエッチング停止膜21は窒化膜で形成する。両者のエッチングレートは異なる。

【0016】

次に、第1のエッチング停止膜21上に第2の層間絶縁膜22を形成する。第2の層間絶縁膜22は、酸化膜、窒化膜、及び酸化窒化膜からなる群より選ばれたいずれかで形成することができ、第1のエッチング停止膜21に対してエッチング選択比を有する物質で形成する。一例として、第1のエッチング停止膜21を窒化膜で形成した場合、第2の層間絶縁膜22は酸化膜で形成する。

【0017】

次いで、周辺領域の第2の層間絶縁膜22及び第1のエッチング停止膜21を選択的にエッチングして第1のビットライン20を露出させる第2のコンタクトホール23を形成した後、第2のコンタクトホール23に導電物質を埋め込んで第2のビットラインコンタクトプラグ24を形成する。

【0018】

続いて、第2の層間絶縁膜22上に第2のビットラインコンタクトプラグ24と接する第2のビットライン25を形成する。

【0019】

図1Cに示すように、第2の層間絶縁膜22上に周辺領域を覆い、セル領域を露出するハードマスクパターン35を形成する。ハードマスクパターン35は、セルオープンマスク(cell open mask)を用いて形成することができる。ハードマスクパターンは、アモルファス炭素膜(Amorphous Carbon Layer)またはシリコンリーチカーボン膜(Si−rich carbon)とシリコン酸化窒化膜(SiON)とが積層された積層膜で形成することができる。このとき、シリコン酸化窒化膜は、反射防止膜として作用する。

【0020】

次に、ハードマスクパターン35をエッチングバリアとしてセル領域の第2の層間絶縁膜22、第1のエッチング停止膜21、及び第1の層間絶縁膜17の一部をエッチングし、ストレージノードコンタクトプラグ12の上面を露出させる。このとき、エッチング工程は、第1のエッチング停止膜21でエッチングが止まるようにオーバーエッチングを十分に行った後、第1のエッチング停止膜21及び第1の層間絶縁膜17の一部をエッチングしてストレージノードコンタクトプラグ12を露出させる。

【0021】

エッチング工程は、ドライエッチング法またはウェットエッチング法を利用して行うか、またはドライエッチング法とウェットエッチング法とを混用して行うことができる。ドライエッチング法を利用する場合には、フッ化炭素ガス(CxFy、1≦x≧5、1≦y≧8)またはフッ化メタンガス(CxHyFz、1≦x≧3、1≦y≧4、0≦z≧5)を用いて行うことができ、エッチング特性(エッチング比、エッチング速度など)を調節するために、フッ化炭素ガスまたはフッ化メタンガスにAr、He、Xe、O2、CO、COS、N2、H2、HBr、Cl2、SiCl4、SF6、及びNF3からなる群より選ばれたいずれか1つまたは2つ以上を添加して行うことができる。ウェットエッチング法を利用する場合には、BOE(Buffered Oxide Etchant)溶液またはフッ酸(HF)溶液を用いて行うことができる。

【0022】

次に、ハードマスクパターン35を除去する。

【0023】

図1Dに示すように、構造物の表面に沿って第2のエッチング停止膜26を形成した後、第2のエッチング停止膜26上にモールド膜27を形成する。モールド膜27は、酸化膜、窒化膜、及び酸化窒化膜からなる群より選ばれたいずれかで形成することができ、第2のエッチング停止膜26に対してエッチング選択比を有する物質で形成する。モールド膜27は、セル領域と周辺領域との間の段差を考慮して、流動性絶縁膜で形成することが好ましい。流動性絶縁膜としては、BPSG(Boro−Phospho Silicate Glass)、PSG(Phospho Silicate Glass)、SOD(Spin On Dielectric)、シリコンリーチカーボン膜などを用いることができる。

【0024】

次いで、第2のビットライン25上の第2のエッチング停止膜26が露出するまで平坦化工程を行う。このとき、平坦化工程を化学的機械的研磨法を利用して行うことができる。

【0025】

続いて、セル領域のモールド膜27及び第2のエッチング停止膜26を選択的にエッチングしてストレージノードコンタクトプラグ12を露出させるストレージノードホール28を形成する。ストレージノードホール28を形成するためのエッチング工程は、ストレージノードホール28の側壁が垂直なプロファイルを有するように、C3F8、C4F6、C4F8またはC5F8のようなフッ化炭素ガス(CxFy、xは3〜5、yは5〜8)をメインエッチングガスとして用い、CH2F2、CH3FなどのCHxFyガス(xは1〜5、yは1〜8)、COS、O2、SiCl4及びCH4からなる群より選ばれたいずれか1つまたは2つ以上を添加して行うことができる。また、プラズマを安定化させると同時に、エッチング選択比を増加させるために、Ar、Xe、He等の不活性ガスをさらに添加して行うことができる。

【0026】

一方、ストレージノードホール28の高さによってストレージノードの高さが決定されるところ、モールド膜27に対する平坦化工程を行った後、モールド膜27上に絶縁膜をさらに形成してストレージノードホール28の高さを増加させることもできる。

【0027】

図1Eに示すように、ストレージノードホール28の内部にストレージノード29を形成する。ストレージノード29は、図面に示されているように、シリンダー型で形成するか、またはピラー型で形成することができる。

【0028】

次に、ウェットディップアウト(wet dip out)工程を行ってモールド膜27を除去する。ウェットディップアウトは、BOE溶液またはフッ酸溶液を用いて行うことができる。ウェットディップアウトを行う過程で第2のエッチング停止膜26によって下部構造物が損傷することを防止することができる。

【0029】

図1Fに示すように、ストレージノード29の表面に誘電膜(図示せず)を形成した後、ストレージノード29を覆うプレート電極30を形成する。これにより、セル領域にキャパシタが形成される。

【0030】

次に、プレート電極30が形成された基板11の前面に第3の層間絶縁膜31を形成する。第3の層間絶縁膜31は、酸化膜、窒化膜、及び酸化窒化膜からなる群より選ばれたいずれかで形成することができる。

【0031】

次いで、周辺領域の第3の層間絶縁膜31及び第2のエッチング停止膜26を選択的にエッチングして第2のビットライン25を露出させる第3のコンタクトホール32を形成した後、第3のコンタクトホール32に導電物質を埋め込んで金属コンタクト33を形成する。

【0032】

続いて、第3の層間絶縁膜31上に金属コンタクト33と接する金属配線34を形成する。

【0033】

上述した本発明の第1の実施形態に係る半導体装置の製造方法は、周辺領域のビットラインが複層構造を有するように、第1のビットライン及び第2のビットライン20、25で形成することにより、金属コンタクト33のための第3のコンタクトホール32の高さを減少させてコンタクトナットオープンが生じたり、金属コンタクト33の抵抗が増加することを防止することができる。また、第3のコンタクトホール32の形成工程に対する工程難易度を減少させ、工程マージンを増加させることができる。参考までに、従来にはストレージノード29の高さの分だけの層間絶縁膜を一度にエッチングして金属コンタクト33のためのコンタクトホールを形成するため、コンタクトナットオープンが生じたり、金属コンタクトの抵抗が増加するという問題が生じ、コンタクトホールが高縦横比を有するため、工程難易度が高く、工程マージンを確保するのが難しかった。

【0034】

また、周辺領域のビットラインが複層構造を有するので、半導体装置の集積度が増加するにつれてビットラインが形成される空間が減少しても、周辺領域のビットラインを容易に実現することができる。

【0035】

図2A〜図2Dは、本発明の第2の実施形態に係る半導体装置の製造方法を示した工程断面図である。

【0036】

図2Aに示すように、本発明の第1の実施形態の図1A〜図1Dに示されたものと同様な方法によってセル領域と周辺領域を有し、所定の構造物(例えば、素子分離膜、埋め込みゲートなど)が形成された基板61のセル領域にストレージノードコンタクトプラグ62、第1のモールド膜77、及び第1のストレージノードホール78を形成し、周辺領域に周辺ゲート66、第1のビットライン70、第2のビットライン75を形成する。

【0037】

ここで、図示していない図面符号「63」は周辺ゲート絶縁膜、「64」は周辺ゲート電極、「65」は周辺ゲートハードマスク膜、「67」は第1の層間絶縁膜、「68」は第1のコンタクトホール、「69」は第1のビットラインコンタクトプラグ、「71」は第1のエッチング停止膜、「72」は第2の層間絶縁膜、「73」は第2のコンタクトホール、「74」は第2のビットラインコンタクトプラグ、「76」は第2のエッチング停止膜を示す。

【0038】

図2Bに示すように、第1のストレージノードホール78の内部に第1のストレージノード79を形成する。このとき、第1のストレージノード79はピラー型で形成する。

【0039】

次に、第1のモールド膜77上に第2のモールド膜80を形成する。第2のモールド膜80は、第1のモールド膜77と同じ物質で形成することができる。

【0040】

次いで、セル領域の第2のモールド膜80を選択的にエッチングして第1のストレージノード79を露出させる第2のストレージノードホール81を形成した後、第2のストレージノードホール81の内部に第2のストレージノード82を形成する。このとき、第2のストレージノード82は、ピラー型で形成するか、またはシリンダー型で形成することができる。

【0041】

第2のストレージノードホール81を形成するためのエッチング工程は、第2のストレージノードホール81の側壁が垂直なプロファイルを有するように、C3F8、C4F6、C4F8またはC5F8のようなフッ化炭素ガス(CxFy、xは3〜5、yは5〜8)をメインエッチングガスとして用い、CH2F2、CH3FなどのCHxFyガス(xは1〜5、yは1〜8)、COS、O2、SiCl4及びCH4からなる群より選ばれたいずれか1つまたは2つ以上を添加して行うことができる。また、プラズマを安定化させると同時に、エッチング選択比を増加させるために、Ar、Xe、Heなどの不活性ガスをさらに添加して行うことができる。

【0042】

図2Cに示すように、ウェットディップアウト(wet dip out)工程を行って第1のモールド膜及び第2のモールド膜77、80を同時に除去する。ウェットディップアウトは、BOE溶液またはフッ酸溶液を用いて行うことができる。ウェットディップアウトを行う過程において第2のエッチング停止膜76によって下部構造物が損傷することを防止することができる。

【0043】

図2Dに示すように、第1のストレージノード及び第2のストレージノード79、82の表面に誘電膜(図示せず)を形成した後、第1のストレージノード及び第2のストレージノード79、82を覆うプレート電極84を形成する。これにより、セル領域に本発明の第1の実施形態よりさらに大きい静電容量を有するキャパシタが形成される。

【0044】

次に、プレート電極84が形成された基板61の前面に第3の層間絶縁膜85を形成する。第3の層間絶縁膜85は、酸化膜、窒化膜、及び酸化窒化膜からなる群より選ばれたいずれかで形成することができる。

【0045】

次いで、周辺領域の第3の層間絶縁膜85及び第2のエッチング停止膜76を選択的にエッチングして第2のビットライン75を露出させる第3のコンタクトホール86を形成した後、第3のコンタクトホール86に導電物質を埋め込んで金属コンタクト87を形成する。

【0046】

続いて、第3の層間絶縁膜85上に金属コンタクト87と接する金属配線88を形成する。

【0047】

上述した本発明の第2の実施形態に係る半導体装置の製造方法は、周辺領域のビットラインが複層構造を有するように、第1のビットライン及び第2のビットライン70、75で形成することにより、金属コンタクト87のための第3のコンタクトホール86の高さを減少させることができる。また、制限された面積内で半導体装置が求める静電容量を確保するために、ストレージノードを第1のストレージノード及び第2のストレージノード79、82で形成して、高さを増加させても第1の層間絶縁膜及び第2の層間絶縁膜67、72の高さを調節する方法によって金属コンタクト87のための第3のコンタクトホール86の高さを減少させることができる。これにより、第3のコンタクトホール86の形成工程時、コンタクトナットオープンが生じたり、金属コンタクト87の抵抗が増加することを防止することができる。さらに、第3のコンタクトホール68の形成工程に対する工程難易度を減少させ、工程マージンを増加させることができる。

【0048】

また、周辺領域のビットラインが複層構造を有するので、半導体装置の集積度が増加するにつれてビットラインが形成される空間が減少しても周辺領域のビットラインを容易に実現することができる。

【0049】

本発明の技術思想は、上記好ましい実施形態によって具体的に記述されたが、上記の実施形態は、その説明のためのものであり、その制限のためのものでないことに注意すべきである。また、本発明の技術分野の通常の専門家であれば、本発明の技術思想の範囲内で様々な実施形態が可能であることが理解できるであろう。

【符号の説明】

【0050】

11 基板

12 ストレージノードコンタクトプラグ

13 周辺ゲート絶縁膜

14 周辺ゲート電極

15 周辺ゲートハードマスク膜

16 周辺ゲート

17 第1の層間絶縁膜

18 第1のコンタクトホール

19 第1のビットラインコンタクトプラグ

20 第1のビットライン

21 第1のエッチング停止膜

22 第2の層間絶縁膜

23 第2のコンタクトホール

24 第2のビットラインコンタクトプラグ

25 第2のビットライン

26 第2のエッチング停止膜

27 モールド膜

28 ストレージノードホール

29 ストレージノード

30 プレート電極

31 第3の層間絶縁膜

32 第3のコンタクトホール

33 金属コンタクト

34 ビットライン

【特許請求の範囲】

【請求項1】

基板のセル領域にストレージノードコンタクトプラグを形成するステップと、

前記基板上に第1の層間絶縁膜を形成するステップと、

前記周辺領域の第1の層間絶縁膜上に第1のビットラインを形成するステップと、

前記第1の層間絶縁膜上に第2の層間絶縁膜を形成するステップと、

前記周辺領域の第2の層間絶縁膜上に前記第1のビットラインと電気的に接続された第2のビットラインを形成するステップと、

前記第2の層間絶縁膜をエッチングして前記セル領域のストレージノードコンタクトプラグの上面を露出させるステップと、

前記セル領域にストレージノードコンタクトプラグと接するキャパシタを形成するステップと、

前記キャパシタが形成された基板の前面に第3の層間絶縁膜を形成するステップと、

前記周辺領域の第3の層間絶縁膜を貫通して前記第2のビットラインに接する金属コンタクトを形成するステップと、

前記第3の層間絶縁膜上に前記金属コンタクトと接する金属配線を形成するステップと、

を含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記金属コンタクトを形成するステップが、

前記周辺領域の第3の層間絶縁膜を選択的にエッチングして第2のビットラインを露出するコンタクトホールを形成するステップと、

前記コンタクトホールに導電物質を埋め込んで金属コンタクトを形成するステップと、

を含むことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第2のビットラインを形成するステップが、

前記第2の層間絶縁膜を貫通して前記第1のビットラインと接するビットラインコンタクトプラグを形成するステップと、

前記第2の層間絶縁膜上に前記ビットラインコンタクトと接する第2のビットラインを形成するステップと、

を含むことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項4】

前記ストレージノードコンタクトホールの上面を露出させるステップが、

ドライエッチング法またはウェットエッチング法を単独で用いて行われるか、またはドライエッチング法とウェットエッチング法とを混用して行われることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項5】

前記キャパシタを形成するステップが、

前記セル領域にストレージノードコンタクトプラグを備える基板の前面にエッチング停止膜を形成するステップと、

前記エッチング停止膜上にモールド膜を形成するステップと、

前記エッチング停止膜が露出するまで平坦化工程を行うステップと、

前記モールド膜及び前記エッチング停止膜を選択的にエッチングして前記ストレージノードコンタクトプラグを露出するストレージノードホールを形成するステップと、

前記ストレージノードホールの内部にストレージノードを形成するステップと、

前記モールド膜を除去するステップと、

前記ストレージノードの表面に沿って誘電膜を形成するステップと、

前記ストレージノードを覆うプレート電極を形成するステップと、

を含むことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項6】

ストレージノードホールを形成するステップで使用される選択的エッチングが、フッ化炭素ガスを用いることを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項7】

前記選択的エッチングが、フッ化炭素ガスの他に、フッ化メタンガスにAr、He、Xe、O2、CO、COS、N2、H2、HBr、Cl2、SiCl4、SF6、及びNF3からなる群より選ばれたいずれか1つまたは2つ以上を添加して行われることを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

前記選択的エッチングが、不活性気体をさらに用いることを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項9】

前記ストレージノードが、シリンダー型またはピラー型で形成されることを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項10】

前記モールド膜が、流動性絶縁膜を形成することを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項11】

前記キャパシタを形成するステップが、

前記セル領域にストレージノードコンタクトプラグを備える基板の前面にエッチング停止膜を形成するステップと、

前記エッチング停止膜上に第1のモールド膜を形成するステップと、

前記エッチング停止膜の一部が露出するまで平坦化工程を行うステップと、

前記第1のモールド膜及び前記エッチング停止膜を選択的にエッチングして前記ストレージノードコンタクトプラグの上面を露出する第1のストレージノードホールを形成するステップと、

前記ストレージノードホールの内部に第1のストレージノードを形成するステップと、

前記第1のモールド膜上に第2のモールド膜を形成するステップと、

前記第2のモールド膜を選択的にエッチングして前記第1のストレージノードの上面を露出する第2のストレージノードホールを形成するステップと、

前記第2のストレージノードホールの内部に第2のストレージノードを形成するステップと、

前記第1のモールド膜及び第2のモールド膜を除去するステップと、

前記第1のストレージノード及び第2のストレージノードの表面に沿って誘電膜を形成するステップと、

前記第1のストレージノード及び第2のストレージノードを覆うプレート電極を形成するステップと、

を含むことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項12】

前記第1のストレージノードが、ピラー型で形成されることを特徴とする請求項11に記載の半導体装置の製造方法。

【請求項13】

前記第2のストレージノードが、ピラー型またはシリンダー型で形成されることを特徴とする請求項11に記載の半導体装置の製造方法。

【請求項14】

前記第1のモールド膜及び第2のモールド膜が、互いに同じ物質で形成されることを特徴とする請求項11に記載の半導体装置の製造方法。

【請求項15】

前記第1のモールド膜及び第2のモールド膜が、流動性絶縁膜を備えることを特徴とする請求項11に記載の半導体装置の製造方法。

【請求項16】

第1の層間絶縁膜を形成するステップと第2の層間絶縁膜を形成するステップとの間に、第1のエッチング停止膜を形成するステップをさらに含むことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項17】

前記第2の層間絶縁膜をエッチングするステップが、

前記周辺領域にマスクを形成するステップと、

前記第2の層間絶縁膜をエッチングするステップと、

を含むことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項18】

前記マスクが、前記周辺領域の第2のビットラインが第2の層間絶縁膜のエッチング過程で損傷することを防止することを特徴とする請求項17に記載の半導体装置の製造方法。

【請求項19】

基板の周辺領域上に周辺ゲートを形成するステップと、

第1のビットラインコンタクトを形成するステップと、

をさらに含み、

前記周辺ゲートが、前記第1のビットラインコンタクトを介して第1のビットラインと接続されることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項1】

基板のセル領域にストレージノードコンタクトプラグを形成するステップと、

前記基板上に第1の層間絶縁膜を形成するステップと、

前記周辺領域の第1の層間絶縁膜上に第1のビットラインを形成するステップと、

前記第1の層間絶縁膜上に第2の層間絶縁膜を形成するステップと、

前記周辺領域の第2の層間絶縁膜上に前記第1のビットラインと電気的に接続された第2のビットラインを形成するステップと、

前記第2の層間絶縁膜をエッチングして前記セル領域のストレージノードコンタクトプラグの上面を露出させるステップと、

前記セル領域にストレージノードコンタクトプラグと接するキャパシタを形成するステップと、

前記キャパシタが形成された基板の前面に第3の層間絶縁膜を形成するステップと、

前記周辺領域の第3の層間絶縁膜を貫通して前記第2のビットラインに接する金属コンタクトを形成するステップと、

前記第3の層間絶縁膜上に前記金属コンタクトと接する金属配線を形成するステップと、

を含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記金属コンタクトを形成するステップが、

前記周辺領域の第3の層間絶縁膜を選択的にエッチングして第2のビットラインを露出するコンタクトホールを形成するステップと、

前記コンタクトホールに導電物質を埋め込んで金属コンタクトを形成するステップと、

を含むことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第2のビットラインを形成するステップが、

前記第2の層間絶縁膜を貫通して前記第1のビットラインと接するビットラインコンタクトプラグを形成するステップと、

前記第2の層間絶縁膜上に前記ビットラインコンタクトと接する第2のビットラインを形成するステップと、

を含むことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項4】

前記ストレージノードコンタクトホールの上面を露出させるステップが、

ドライエッチング法またはウェットエッチング法を単独で用いて行われるか、またはドライエッチング法とウェットエッチング法とを混用して行われることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項5】

前記キャパシタを形成するステップが、

前記セル領域にストレージノードコンタクトプラグを備える基板の前面にエッチング停止膜を形成するステップと、

前記エッチング停止膜上にモールド膜を形成するステップと、

前記エッチング停止膜が露出するまで平坦化工程を行うステップと、

前記モールド膜及び前記エッチング停止膜を選択的にエッチングして前記ストレージノードコンタクトプラグを露出するストレージノードホールを形成するステップと、

前記ストレージノードホールの内部にストレージノードを形成するステップと、

前記モールド膜を除去するステップと、

前記ストレージノードの表面に沿って誘電膜を形成するステップと、

前記ストレージノードを覆うプレート電極を形成するステップと、

を含むことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項6】

ストレージノードホールを形成するステップで使用される選択的エッチングが、フッ化炭素ガスを用いることを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項7】

前記選択的エッチングが、フッ化炭素ガスの他に、フッ化メタンガスにAr、He、Xe、O2、CO、COS、N2、H2、HBr、Cl2、SiCl4、SF6、及びNF3からなる群より選ばれたいずれか1つまたは2つ以上を添加して行われることを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

前記選択的エッチングが、不活性気体をさらに用いることを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項9】

前記ストレージノードが、シリンダー型またはピラー型で形成されることを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項10】

前記モールド膜が、流動性絶縁膜を形成することを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項11】

前記キャパシタを形成するステップが、

前記セル領域にストレージノードコンタクトプラグを備える基板の前面にエッチング停止膜を形成するステップと、

前記エッチング停止膜上に第1のモールド膜を形成するステップと、

前記エッチング停止膜の一部が露出するまで平坦化工程を行うステップと、

前記第1のモールド膜及び前記エッチング停止膜を選択的にエッチングして前記ストレージノードコンタクトプラグの上面を露出する第1のストレージノードホールを形成するステップと、

前記ストレージノードホールの内部に第1のストレージノードを形成するステップと、

前記第1のモールド膜上に第2のモールド膜を形成するステップと、

前記第2のモールド膜を選択的にエッチングして前記第1のストレージノードの上面を露出する第2のストレージノードホールを形成するステップと、

前記第2のストレージノードホールの内部に第2のストレージノードを形成するステップと、

前記第1のモールド膜及び第2のモールド膜を除去するステップと、

前記第1のストレージノード及び第2のストレージノードの表面に沿って誘電膜を形成するステップと、

前記第1のストレージノード及び第2のストレージノードを覆うプレート電極を形成するステップと、

を含むことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項12】

前記第1のストレージノードが、ピラー型で形成されることを特徴とする請求項11に記載の半導体装置の製造方法。

【請求項13】

前記第2のストレージノードが、ピラー型またはシリンダー型で形成されることを特徴とする請求項11に記載の半導体装置の製造方法。

【請求項14】

前記第1のモールド膜及び第2のモールド膜が、互いに同じ物質で形成されることを特徴とする請求項11に記載の半導体装置の製造方法。

【請求項15】

前記第1のモールド膜及び第2のモールド膜が、流動性絶縁膜を備えることを特徴とする請求項11に記載の半導体装置の製造方法。

【請求項16】

第1の層間絶縁膜を形成するステップと第2の層間絶縁膜を形成するステップとの間に、第1のエッチング停止膜を形成するステップをさらに含むことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項17】

前記第2の層間絶縁膜をエッチングするステップが、

前記周辺領域にマスクを形成するステップと、

前記第2の層間絶縁膜をエッチングするステップと、

を含むことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項18】

前記マスクが、前記周辺領域の第2のビットラインが第2の層間絶縁膜のエッチング過程で損傷することを防止することを特徴とする請求項17に記載の半導体装置の製造方法。

【請求項19】

基板の周辺領域上に周辺ゲートを形成するステップと、

第1のビットラインコンタクトを形成するステップと、

をさらに含み、

前記周辺ゲートが、前記第1のビットラインコンタクトを介して第1のビットラインと接続されることを特徴とする請求項1に記載の半導体装置の製造方法。

【図1A】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図2A】

【図2B】

【図2C】

【図2D】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図2A】

【図2B】

【図2C】

【図2D】

【公開番号】特開2012−134454(P2012−134454A)

【公開日】平成24年7月12日(2012.7.12)

【国際特許分類】

【出願番号】特願2011−227071(P2011−227071)

【出願日】平成23年10月14日(2011.10.14)

【出願人】(310024033)エスケーハイニックス株式会社 (122)

【氏名又は名称原語表記】SK hynix Inc.

【住所又は居所原語表記】2091, Gyeongchung−daero,Bubal−eub,Icheon−si,Gyeonggi−do,Korea

【Fターム(参考)】

【公開日】平成24年7月12日(2012.7.12)

【国際特許分類】

【出願日】平成23年10月14日(2011.10.14)

【出願人】(310024033)エスケーハイニックス株式会社 (122)

【氏名又は名称原語表記】SK hynix Inc.

【住所又は居所原語表記】2091, Gyeongchung−daero,Bubal−eub,Icheon−si,Gyeonggi−do,Korea

【Fターム(参考)】

[ Back to top ]