Fターム[5F033QQ04]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 露光 (971) | 反射防止に関するもの (535) | 絶縁膜の反射防止膜を用いるもの (242)

Fターム[5F033QQ04]に分類される特許

1 - 20 / 242

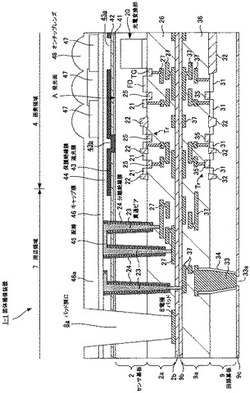

固体撮像装置、固体撮像装置の製造方法、および電子機器

【課題】裏面照射型の固体撮像装置において、受光面と遮光膜との距離を小さくすることにより、光電変換部での受光特性の向上を図る。

【解決手段】光電変換部が配列形成された画素領域を有するセンサ基板と、センサ基板において光電変換部に対する受光面とは逆の表面側に設けられた駆動回路と、画素領域における受光面上に設けられた遮光膜と、遮光膜を覆って設けられた保護絶縁膜と、画素領域の外側の周辺領域において、保護絶縁膜からセンサ基板にかけて埋め込まれ駆動回路に接続された複数の貫通ビアを備えた固体撮像装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】新規な構造のコンタクトプラグを有する半導体装置を提供する。

【解決手段】

半導体装置は、半導体基板と、半導体基板に形成され、ソース/ドレイン領域及びゲート電極を有するトランジスタと、トランジスタのソース/ドレイン領域及びゲート電極を覆う絶縁膜と、絶縁膜中に形成され、トランジスタのソース/ドレイン領域またはゲート電極に接されるコンタクトプラグとを有し、コンタクトプラグは、絶縁膜の厚さ方向に延在しトランジスタのソース/ドレイン領域またはゲート電極に接触する柱部と、柱部の上部から絶縁膜の表面と平行な方向に張り出し上面が平坦化された鍔部とを有する。

(もっと読む)

成膜方法、これを含む半導体装置の製造方法、成膜装置、及び半導体装置

【課題】柱状形状を有し密に配列される電極の倒壊を防ぐことが可能な半導体装置を提供する。

【解決手段】電界効果トランジスタと、柱状形状を有するキャパシタとを有する半導体装置であって、前記電界トランジスタの不純物拡散領域と電気的に接続し、柱状形状を有する第1の電極と、前記第1の電極の少なくとも側面に形成される誘電体膜と、前記誘電体膜上に形成される第2の電極と、前記柱状形状を有する前記第1の電極の長手方向と交差する方向に延び、前記第2の電極の少なくとも一部を貫通して前記第1の電極を連結するホウ素添加窒化シリコン膜により形成される支持膜とを備える半導体装置により、上記の課題が達成される。

(もっと読む)

半導体装置の製造方法

【課題】

本発明は、簡便に形成できて、チャージアップしにくいハードマスクを用いた半導体装置の製造方法を提供することを目的とする。

【解決手段】

半導体装置の製造方法であって、半導体基板上に形成された被加工膜上に、アミン化合物と水素化アルミニウムとの錯体を含有するアルミニウム膜形成用材料を塗布して、塗布膜を形成する工程と、前記塗布膜に対して、加熱処理および光照射処理から選ばれる少なくとも一種の処理を行いアルミニウム膜を形成する工程と、 該アルミニウム膜をエッチングしてハードマスクを形成する工程と、前記ハードマスクをマスクにして被加工膜をエッチングする工程を有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置における配線形状を改善すること。

【解決手段】半導体装置の製造方法は、溝領域を規定する第1パターンを有する第1マスクを、サイドウォール形状の転写により、半導体装置の層間膜に設けられた金属膜上に形成する工程と、前記第1パターンに重なる少なくとも一つの開口を有する第2マスクを、平面図で見た場合に、前記2マスクが前記第1マスクに重なり、前記開口が前記溝領域に重なるように、形成し、第2パターンを形成する工程と、前記第1及び第2マスクを介して、前記層間膜をエッチングし、前記第1パターンを前記層間膜に転写させる工程と、前記第2マスクを介して前記層間膜をエッチングし、前記第2パターンを前記層間膜に転写させる工程とを具備する。前記第1パターンは、前記第2パターンとは異なる深さで前記層間膜に形成される。

(もっと読む)

半導体装置の製造方法及び製造装置

【課題】半導体装置のエッチングを精度良く行い、再生率を低減させる

【解決手段】基板にトランジスタを形成し、トランジスタを覆うように第1層間絶縁膜22を形成する。さらに、第1層間絶縁膜22の上方に形成したレジスト膜27を用いて第1層間絶縁膜22をエッチングし、トランジスタのソース/ドレイン領域に到達するコンタクトホール31を形成する。この際、レジスト膜27の開口部27Aの半径rと、開口部27Aが設計位置からずれている位置ずれ量ΔXとを測定し、コンタクトホール31に必要な半径Rxと、コンタクトホール31を形成可能な限界距離Sとから、r+ΔX−S<ES<r−Rxを満たす半径差ESを決定し、半径差ESからエッチング条件を決定する。

(もっと読む)

側壁イメージ転写からパターンを作る改善された方法

【課題】実施の容易な、側壁イメージ転写により部分的に定義されるパターンを生成する方法を提供する。

【解決手段】基板1には、第1の材料2の層と、第1のエッチングマスク4と、カバリング層3と、第2のエッチングマスクとが設けられている。カバリング層3は、覆われた主領域と、覆われていない副領域とを有する。カバリング層3の副領域は、第2のエッチングマスクを介して部分的にエッチングされ、突出パターンが形成される。第3のエッチングマスクを定義する突出パターンの周囲に、横スペーサが形成される。第2のエッチングマスクは除去される。カバリング層3は、第3のエッチングマスクを用いてエッチングされ、カバリング層3における突出パターンが形成され、第1のエッチングマスク4および第1の材料2が露出される。第1の材料2の層は、エッチングされ、第1の材料2から作られるパターンが形成される。

(もっと読む)

光電変換装置およびその製造方法

【課題】 配線材料の層間絶縁膜への拡散を抑制する拡散抑制膜による多層配線構造を設けた光電変換装置において、工程を増加させることなく、受光効率を高める。

【解決手段】 本発明は、半導体基板に配された光電変換素子と、前記半導体基板上に層間絶縁膜を介して複数の配線層が配された多層配線構造を有する光電変換装置であって、最上配線層の上部に、前記最上配線層を構成する材料の拡散を抑制する拡散抑制膜が配され、前記拡散抑制膜は、前記最上配線層及び前記層間絶縁膜の前記光電変換素子に対応する領域を覆って配されており、前記拡散抑制膜の前記光電変換素子に対応する領域にレンズが配されていることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】金属コンタクトを安定に形成できる半導体装置の製造方法を提供する。

【解決手段】セル領域にストレージノードコンタクトプラグ12を形成するステップと、第1の層間絶縁膜17を形成するステップと、周辺領域の第1の層間絶縁膜上に第1のビットライン20を形成するステップと、第2の層間絶縁膜22を形成するステップと、周辺領域の第2の層間絶縁膜上に第1のビットラインと電気的に接続された第2のビットライン25を形成するステップと、セル領域のストレージノードコンタクトプラグの上面を露出させるステップと、セル領域にストレージノードコンタクトプラグと接するキャパシタを形成するステップと、キャパシタが形成された基板の全面に第3の層間絶縁膜31を形成するステップと、周辺領域の第3の層間絶縁膜を貫通して第2のビットラインに接する金属コンタクト33を形成するステップとを含むことを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の検査特性を向上させる。

【解決手段】本発明の半導体装置の製造方法は、(a)基板の上方にアルミニウムを含有する導電性膜(アルミニウム膜10b)を形成する工程と、(b)上記導電性膜をパターニングすることにより配線を形成する工程と、(c)上記配線の上部に第1絶縁膜(第1保護膜)を形成する工程と、を有する。さらに、(d)上記第1絶縁膜をエッチングすることにより、上記配線のパッド領域(Pd)を露出する工程と(e)上記パッド領域(Pd)に、窒素系のプラズマガスを用いたプラズマ処理を行う工程と、(f)上記(e)工程の後、上記パッド領域(Pd)にプローブ針を当接し、上記パッド領域(Pd)に通電する工程と、を有する。上記(e)工程により、上記パッド領域(Pd)に窒化アルミニウム層(15)が形成され、パッド領域(Pd)とプローブ針(N)との接触抵抗を低減することができる。

(もっと読む)

固体撮像装置及び電子機器

【課題】隣接カップリング容量を抑制した固体撮像装置及びこの固体撮像装置を備えたカメラ等の電子機器を提供する。

【解決手段】半導体チップ部が貼り合わされ、第1の半導体チップ部に画素アレイと第1多層配線層が形成され、第2の半導体チップ部にロジック回路と第2多層配線層が形成された積層半導体チップを有する。半導体チップ間を接続する複数の接続配線67と、一方向に隣り合う接続配線67間をシールドする第1シールド配線113とを有する。各接続配線67は、第1多層配線層内の所要の第1配線に繋がる第1の接続パッドに接続された接続導体68と、第1の半導体チップ部を貫通して第2多層配線層内の所要の第2配線に繋がる第2の接続パッドに接続された貫通接続導体69を有する。接続配線67は、接続導体68と貫通接続導体とを連結する連結導体とを有して形成される。固体撮像装置は、裏面照射型の固体撮像装置として構成される。

(もっと読む)

半導体装置の製造方法

【課題】より視認が容易なアライメントマークを簡素な工程で形成することが可能な、半導体装置の製造方法を提供する。

【解決手段】半導体基板SUBの主表面上に、主表面に対して段差を有するパターンMKが形成される工程と、パターンMK上に、半導体材料を含む第1の半導体層PS1が形成される工程と、第1の半導体層PS1上に、半導体材料を含む第2の半導体層PS2が形成される工程と、第2の半導体層PS2上にレジストパターンRSが形成される工程とを備えている。レジストパターンRSが形成される工程において、パターンMKが位置合わせマークとして用いられる。

(もっと読む)

半導体装置の製造方法

【課題】微細で良好な形状のコンタクトホールを有する半導体装置の製造方法を提供する。

【解決手段】絶縁膜36上にフォトレジスト膜42を形成する工程と、フォトレジスト膜42に開口部44を形成する工程と、開口部44が形成されたフォトレジスト膜42をマスクとして絶縁膜36をエッチングすることによりコンタクトホール48を形成する工程とを有し、コンタクトホール48を形成する工程は、開口部44が形成されたフォトレジスト膜42上に保護膜46を堆積しながら絶縁膜36をプラズマエッチングする第1の工程と、フォトレジスト膜42上に堆積された保護膜46を一旦除去する第2の工程と、保護膜46が一旦除去されたフォトレジスト膜42上に他の保護膜を新たに堆積しながら絶縁膜36を更にプラズマエッチングする第3の工程とを含んでいる。

(もっと読む)

半導体装置

【課題】抵抗値の温度依存性の小さい抵抗素子を有する半導体装置を提供する。

【解決手段】半導体装置は、金属抵抗素子層Rm1,Rm2を有する。金属抵抗素子層Rm1は、金属抵抗膜層Rm11を含む。金属抵抗素子層Rm2は、金属抵抗膜層Rm12を含む。金属抵抗膜層Rm11は、窒化チタン抵抗および窒化タンタル抵抗のうちの一方であり、金属抵抗膜層Rm12は、窒化チタン抵抗および窒化タンタル抵抗のうちの他方である。窒化チタン抵抗の抵抗値は正の温度係数を有する一方、窒化タンタル抵抗の抵抗値は負の温度係数を有する。コンタクトプラグCP2によって、金属抵抗膜層Rm11と金属抵抗膜層Rm12とが電気的に接続されるので、窒化チタン抵抗の温度係数と窒化タンタル抵抗との温度係数が相殺される。これにより温度係数を小さくすることができる。

(もっと読む)

半導体素子及びその半導体素子のパターン形成方法

【課題】 フォトリソグラフィ工程の解像限界内で、具現可能なサイズのパターンを利用して超微細な幅及び間隔を持つ高密度パターンを形成できる配置構造を持つ半導体素子及びその半導体素子パターン形成方法を提供する。

【解決手段】 半導体素子は、コネクション領域に隣接するメモリセル領域を含む基板、メモリセル領域からコネクション領域まで第1方向に延びて配され、第1ライン幅及び第1ライン間隔を持つ複数の第1導電ライン、第1導電ラインそれぞれに連結されるように配され、第2ライン幅及び第2ライン間隔を持つ複数の第2導電ライン、コネクション領域に配され、第1導電ラインに電気的に連結された複数のパッド、を備える。半導体素子上のパターン形成方法は、微細ライン幅及び間隔を提供するために2段階のスペーサ形成工程を含むことができる。

(もっと読む)

半導体装置の製造方法

【課題】ビット線材料埋設体の形状のばらつきに起因するビット線の配線抵抗値のばらつきを防ぐ半導体装置の製造方法を提供する。

【解決手段】製造方法は、第一溝4内に第一のビット線材料埋設体6および第二のビット線材料埋設体10からなるビット線11を形成する第一工程と、ビット線11に含まれる不純物を拡散させて第一不純物拡散領域13を形成する第二工程と、ピラー部1bを形成する第三工程と、ピラー部1bに対向する配線17を第二溝15内に形成する第四工程と、ピラー部1bの先端部に、第二不純物拡散領域19を形成する第五工程と、を具備し、第一工程が、第一溝4を完全に埋め込むように第一ビット線材料を形成した後に第一ビット線材料表面を平坦化し、第一溝4底部に残るように第一ビット線材料をエッチバックする工程を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜などの積層構造を低背化しつつ、アライメント用のマークが容易に形成された半導体装置、およびその製造方法を提供する。

【解決手段】半導体基板SUBに形成された光電変換素子PTOと、マーク部のストッパ膜AL1と、ストッパ膜AL1上および光電変換素子PTO上に形成された第1の層間絶縁膜II2と、第1の金属配線AL2と、第2の層間絶縁膜II3とを備える。層間絶縁膜II2、II3を貫通してストッパ膜AL1に達するスルーホールDTHが形成され、スルーホールDTH内の導電層DTの上面に第1の凹部CAVが形成される。第1の凹部CAVの上面の第2の金属配線AL3に、アライメントマークとなる第2の凹部MKを備える。

(もっと読む)

空隙組込みの構造体及び方法

【課題】 空隙を組み込んだ構造体及びその形成方法を提供する。

【解決手段】 VLSI及びULSI用の空隙含有金属・絶縁体相互接続構造体を、光パターン化可能低k材料を用いて作成する方法、及び形成した空隙含有金属・絶縁体相互接続構造体を開示する。より具体的には、本明細書で説明する方法は、内部に種々異なる深さの空隙がフォトリソグラフィにより画定された光パターン化可能低k材料の内部に構築される相互接続構造体を提供する。本発明の方法においては、空隙を形成するのにエッチ・ステップは必要としない。光パターン化可能低k材料内部の空隙を形成するのに、エッチ・ステップを必要としないで、本発明において開示する方法は、高信頼性の相互接続構造体を提供する。

(もっと読む)

半導体装置の製造方法

【課題】製造工程数及び製造コストを削減しつつ、信頼性の高い半導体装置を製造することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地層1上にTiを主成分とする密着層2を形成する工程と、密着層2上にWを主成分とする導電層3を形成する工程と、導電層3上にSiONを主成分とするハードマスク層4を形成する工程と、ハードマスク層4上にレジストパターン5を形成する工程と、レジストパターン5を保護膜とするエッチング処理により導電層3の一部3aを露出させる工程と、レジストパターン5及びハードマスク層4の残部4aを保護膜とするエッチング処理により密着層2の一部2aを露出させる工程と、その後、エッチング処理により下地層1の一部1aを露出させると共に、導電層3の残部3bを露出させる工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】簡易な追加工程を設けることで、基板のベベル部から膜が剥離することを抑制する。半導体装置の製造歩留まりの低下を抑制すると共に、製造コストの増加を抑制する。

【解決手段】半導体基板上の全面に、1以上の膜を有する構造を形成した後、膜構造上にパターンを有する第1のマスクを形成する。ベベル部上の第1のマスクを覆うように第2のマスクを形成する。第1のマスク及び第2のマスクを用いて、膜構造をエッチングした後、残留した第1のマスク及び第2のマスクを除去する。

(もっと読む)

1 - 20 / 242

[ Back to top ]