Fターム[5F092AB01]の内容

Fターム[5F092AB01]に分類される特許

201 - 220 / 645

電流センサの製造方法

【課題】少ない製造工程数でS/N比が良く、資源に無駄を生じない低コストの電流センサを提供する。

【解決手段】InSb等の単結晶基板1とフェライト基板2とを接着し、単結晶基板1の非接着面を厚みが5〜10[μm]になるまで研磨する。この研磨面に、ホール素子パターンとしての複数の感磁性部1aを形成した後、フェライト基板2ごと切断して複数のホール素子チップ5を分割形成する。次に、接着剤7を介しホール素子チップ5をフェライトコア6の段差部6aに接着し、感磁性部1aに電極8及び保護膜9を形成する。フェライトコア6及び感磁性部1aを含む磁気回路を他のLコア、Iコアを組み付けて構成し、電流センサを製造する。

(もっと読む)

磁気センサ

【課題】出力電圧の測定精度を高めることで、検出精度を向上させる磁気センサを提供する。

【解決手段】外部磁界の方向を検出するための磁気センサ1は、それぞれが少なくとも1つの磁気抵抗効果素子からなる4つの抵抗素子部11−14によって構成され、外部磁界の方向に応じて出力が変化するようになっているブリッジ回路10と、ブリッジ回路10の各出力端子A,Cにそれぞれ接続された2つの抵抗体21,22と、を有し、各抵抗素子部11−14の抵抗値が磁気抵抗変化により最小値となった時のブリッジ回路10の抵抗値に対する、各抵抗体21,22の抵抗値の比が2以上である。

(もっと読む)

電流センサの製造方法

【課題】ホール素子チップの厚さを均一化し、感度特性が均一で歩留まりや耐熱性に優れた電流センサの製造方法とする。

【解決手段】InSb単結晶基板13を、エポキシ接着剤12が塗布された支持基板11に接着する。単結晶基板13を面出し表面研磨し、その鏡面研磨面に感磁性部14を形成する。仮接着剤16を均一に塗布した支持基板15の一面と、感磁性部14が形成された単結晶基板13の一面とを仮接着し、支持基板11を除去する。単結晶基板13を感磁性部14が露出するまで研磨し、個々の感磁性部14を支持基板15ごと切断して多数のホール素子チップ17を分割形成する。エポキシ接着剤19を介しホール素子チップ17をフェライトコア18に接着して支持基板15を除去し、感磁性部14に電極21及び保護膜22を形成する。フェライトコア18及び感磁性部14を含む磁気回路を他のコアを組み付けて構成し、電流センサを製造する。

(もっと読む)

ホール素子

【課題】感磁面に対して平行な磁場を検出するホール素子において、磁気増幅効果を損なうことなく、小型化および薄型化を実現すること。

【解決手段】ホール素子100は、感磁面が化合物半導体で構成されたホール素子部110と、ホール素子部110の感磁面111と平行に配置された磁気収束板120とを備える。感磁面111の幅をW、磁気収束板120の幅をA、長さをB、厚みをDとする。感磁面111と磁気収束板120との間のギャップをCとする。磁気増幅率は長さBに比例しており、アスペクト比B/Aが3以上となる形状では磁気増幅率が1.5倍を超え、更にBを300μmとしたB/A=5の場合には磁気増幅率が3倍に達する。また、A/W<3を満足するよう磁気収束板120の幅Aを狭めてゆくと、磁束の集中する磁気収束板120の側面部が感磁面111に近づくため、磁気増幅率の増加が著しい。

(もっと読む)

磁気センサおよびその製造方法

【課題】コンパクトな構成でありながら磁場の検出性能に優れ、かつ容易に製造可能な磁気センサを提供する。

【解決手段】磁化固着層63と介在層62と磁化自由層61とを順にそれぞれ含むと共に、信号磁場によって互いに反対向きの抵抗変化を示す第1および第2のMR素子を備える。第1および第2のMR素子における磁化固着層63が、介在層62の側から順にピンド層631と、結合層632と、ピンド層631と反強磁性結合するピンド層633とを含むシンセティック構造を有する。第1のMR素子における磁化固着層63は、ピンド層361の総磁気モーメントがピンド層633の総磁気モーメントと一致もしくはピンド層633の総磁気モーメントよりも大きなものである。一方、第2のMR素子における磁化固着層63は、ピンド層633の総磁気モーメントがピンド層631の総磁気モーメントよりも大きなものである。

(もっと読む)

磁気センサの製造方法及び磁気センサ

【課題】少なくとも製造時のパッケージ工程においてセンサに熱が加えられたとしても、オフセット電圧のバラツキを軽減することができる磁気センサの製造方法及び磁気センサを提供する。

【解決手段】磁気センサの基板表面の絶縁層に、ブリッジ状に組んだ磁気抵抗10〜40を成膜する。磁気抵抗10〜40の成膜後、その表面に保護膜を成膜する。保護膜成膜後、その基板部品、即ち基板モジュールをアニールする。このアニール後、磁気抵抗10〜40の粗調部8をレーザトリミングによりカットすることで、磁気抵抗10〜40の抵抗値を調整する。そして、最後に基板モジュールをパッケージする。

(もっと読む)

磁界センサの診断動作モードを生成するための回路および方法

磁界センサは、磁界センサの中で使用される磁界検知素子のセルフテストを含めて磁界センサの回路の大部分またはすべてのセルフテストを可能にする診断回路を含む。磁界センサは、磁界センサが応答する診断磁界を発生することができる。  (もっと読む)

(もっと読む)

磁気センサ及び磁場強度測定方法

【課題】従来よりも構成が簡単であり、全体の形状の小型化を図ることができ、製造コストの低い磁気センサ、及び、そのような磁気センサを用いた磁場強度測定方法を提供する。

【解決手段】本発明に係る磁気センサ50は、磁化自由層3と、非磁性層5と、磁化固定層7とがこの順に積層された積層体2を有し、その積層方向と垂直な一方向を長手方向とする磁気抵抗効果素子14と、磁気抵抗効果素子14と積層方向に離間するように磁気抵抗効果素子14に絶縁層18を介して設けられ、電流が供給されることにより磁場を発生させる電流経路層22とを備え、電流経路層22は、積層方向から見て磁気抵抗効果素子14の長手方向と0度以上45度以下の角度をなす方向に沿って伸びている。

(もっと読む)

磁性素子の製造法及び記憶媒体

【課題】磁性膜又は反磁性膜をエッチングする際に発生するパーティクルの混入を抑制し、高性能なTMR素子を製造する方法を提供する。

【解決手段】炭化水素類、アルコール類、エーテル類、アルデヒド類、カルボン酸類、エステル類及びジオン類からなるガス化化合物群から選択された少なくとも一種のガス化化合物を0.5×1017分子数/分・m2以上、好ましくは2×1017分子数/分・m2以上の分子流速の条件下において形成したプラズマ雰囲気下で、磁性膜又は反磁性膜をエッチングする。

(もっと読む)

二重障壁強磁性トンネル接合および磁気デバイス

【課題】室温で1000%以上のTMR効果が得られる低抵抗の二重障壁強磁性トンネル接合と、この二重障壁強磁性トンネル接合を用いた磁気デバイスを提供する。

【解決手段】下地層/強磁性層1/絶縁層1/強磁性層2/絶縁層2/強磁性層3/上部層の構造が基板材料上に積層され、下地層により強磁性層1の磁化が、上部層により強磁性層3の磁化が固定され、強磁性層2が磁化自由層として機能する構造の二重障壁強磁性トンネル接合において、強磁性層2をCoFeB合金とし、かつ、その厚さを0.5〜1.4nmに薄膜化し、絶縁層1および2をMgOとし、250〜400℃程度の熱処理プロセスを経ることで低抵抗、かつ、1000%を超える巨大なTMR比が得られる。

(もっと読む)

磁性素子の製造法及び記憶媒体

【課題】磁性体層又は反磁性体層をエッチングする際のパーティクルの混入を抑制し、高性能なTMR素子を提供する。

【解決手段】炭化水素類ガス、アルコール類ガス、エーテル類ガス、アルデヒド類ガス、カルボン酸類ガス、エステル類ガス及びジオン類ガスからなる化合物ガス群から選択された少なくとも一種の化合物ガス、及び酸素ガスを有する混合ガス中の全炭素原子数Cnと全酸素原子数OnとがOn/Cn>1の関係を満たし、該混合ガスを用いて形成したプラズマ雰囲気下で、磁性体層又は反磁性体層をエッチングする。

(もっと読む)

磁気積層体設計

磁気積層体は、磁化の向きを切換えることができる自由層と、磁化の向きが固定された基準層と、これらの間にあるバリア層とを有する。この積層体は、自由層から電気的に分離されるとともに基準層と物理的に接触する環状反強磁性ピニング層を含む。ある実施の形態では、基準層は自由層よりも大きい。  (もっと読む)

(もっと読む)

磁気センサ

【課題】 1チップ内に作製できる構造の磁気センサを提供する。

【解決手段】 基板11に磁気センサ素子12e〜12h(12i〜12l)から配線に接続するビア部と、この配線から外部に出力を取り出すパッド部とを備えるとともに、基板11上に複数の突部15を連続して備え、複数の突部15は2つの連続する傾斜面15a,15bを有しており、同じ角度で傾斜する一方の傾斜面15a上に磁気センサ素子12eが形成されていて、傾斜面15a上に形成された複数の磁気センサ素子12e-2,12e-3は傾斜面15a上に形成されたリードおよびこのリードに連続する他方の傾斜面15b上に形成されたリード12e-6,12e-7により直列に接続されており、リードは配線を介してパッドに接続されている。

(もっと読む)

地磁気センサ

【課題】 特に外乱磁場に強く且つ安定した検出精度を得ることができるとともに、外部磁場環境下においても出力の変化を抑制できる磁気センサを提供することを目的とする。

【解決手段】 素子部12と永久磁石層60,65とで素子連設体61が構成され、感度軸方向が素子幅方向(Y方向)である。複数の素子連設体61が素子幅方向に間隔を空けて並設され、隣接する素子連設体同士が接続されてミアンダ状を成している。各素子連設体61の間、及び素子幅方向の両側に位置する素子連設体61の外側には、素子連設体61と非接触の軟磁性体18が設けられている。素子連設体61の素子長さ寸法はL1で、軟磁性体18の素子連設体61の素子長さ方向と同方向の長さ寸法はL2であり、長さ寸法L2は、素子長さ寸法L1の1倍〜1.5倍に設定されている。

(もっと読む)

磁電変換素子の製造方法

【課題】磁電変換素子を極めて容易に短時間で作業性の優れた連続方法で製造することを可能とする。

【解決手段】基板が磁性体の磁電変換素子用ペレットを、リードフレームに接続する工程を備える磁電変換素子の製造方法は、複数の半導体素子を形成したウエハの裏面に樹脂層を設ける工程と、樹脂層を設けたウエハをダイシングして個別の磁電変換素子用ペレットにする工程と、磁電変換素子用ペレットを、樹脂層を介してリードフレームに固着する工程と、磁電変換素子用ペレット上の電極をリードフレームと結線する工程とを具え、該樹脂層が厚み1〜50μmであり、前記樹脂層の樹脂がガラス転移点60〜160℃、接着活性温度170〜350℃、および熱伝導率0.2〜3.5W/m/℃を有している。

(もっと読む)

磁気センサ

【課題】 従来に比べてギャップ依存性を小さくし、安定した検出精度を得ることが可能な磁気センサを提供することを目的とする。

【解決手段】 磁気センサ12は、外部磁界を生じる磁石(磁界発生手段)13と非接触に設けられ、前記外部磁界を検知する磁気検出素子を備えている。磁気センサ12と磁石13間にはギャップGが設けられている。磁気センサ12には、前記磁気検出素子と非接触の位置に、前記磁気検出素子に外部から作用する磁束密度を制御する軟磁性体14が設けられている。これにより、従来に比べてギャップ依存性を小さくし、安定した検出精度を得ることができる。

(もっと読む)

半導体装置

【課題】 従来、外付け抵抗の電圧降下から検出していたパワーN型MOSFETに流れる電流を、高感度のホール素子に発生するホール電圧VHにより検出する。

【解決手段】 アースラインに向かって配線されたソース配線層8の一部をN型層1に形成したトレンチ20内に配設する。これによりトレンチ20内に配設されたソース配線層8a近傍のN型層1に発生する磁束密度Bを高める。この高い磁束密度Bが発生しているトレンチ20内のソース配線層8a近傍のN型層1を横切るホール電流IH成分を増やし、ホール素子Hに発生するホール電圧VHを高くする。このように、高い磁束密度Bの発生領域にホール素子Hを配置することにより、パワーN型MOSFETのソース電流Iが数A程度でも大きなホール電圧VHを発生する。

(もっと読む)

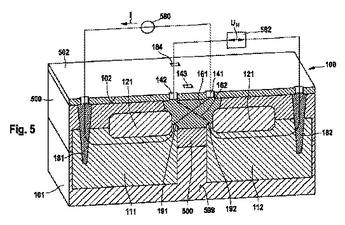

ホールセンサ素子および磁界を測定する方法

本発明は、ホールセンサ素子に関する。当該基板は、主要表面を備えた基板と、前記主要表面から前記基板内まで延在している、導電性のアクティブ領域と、前記アクティブ領域と、第1の下方のコンタクト面で接触している、基板内の導電性の第1埋設層とを有している。別の観点では、本発明は、上記のホールセンサ素子を用いた磁界の測定方法を実現する。ここでは、電気的な測定電流は主要表面での第1の上方コンタクト電極と第1の下方コンタクト面との間で、アクティブ領域を通って導かれる。第1の下方コンタクト面と第1の上方コンタクト電極との間の接続線に対して傾斜して延在する区間に沿って、アクティブ領域でホール電圧が検出される。択一的に、測定電流が上記の区間に亘って、アクティブ領域を通って導かれ、ホール電圧が第1の上方コンタクト電極と第1の下方コンタクト面との間で検出される。  (もっと読む)

(もっと読む)

スピン伝導素子

【課題】スピンの散乱を抑制しつつ、良好なスピン伝導性及び電気抵抗特性を実現可能なスピン伝導素子を提供すること。

【解決手段】スピン伝導素子100Aは、半導体材料からなるチャンネル7と、チャンネル7上に第1絶縁層81を介して配置された磁化固定層12Bと、チャンネル7上に第2絶縁層82を介して配置された磁化自由層12Cと、チャンネル7上に配置された第1電極20A及び第2電極20Dと、を備え、チャンネル7のうちの第1絶縁層81との接触面を含む第1領域71、第2絶縁層82との接触面を含む第2領域72、第1電極20Aとの対向面を含む第3領域74、及び第2電極20Dとの対向面を含む第4領域75のキャリア濃度は、チャンネル7全体の平均のキャリア濃度よりも高いことを特徴とする。

(もっと読む)

半導体装置

【課題】従来、外付け抵抗の電圧降下から検出していたパワーN型MOSFETに流れる電流を、ホール素子に発生するホール電圧VHにより検出する。

【解決手段】アースラインに向かって配線されたソース配線層8の直下の絶縁膜7aを数10nm程度の厚さとする。これにより、ソース電流Iにより、ソース配線層8の直下領域または該ソース配線層8の両側面部のN型層1に発生する磁束密度Bを高くする。この高い磁束密度Bの発生領域にホール素子Hを配置することにより、パワーN型MOSFETのソース電流Iが数A程度でも大きなホール電圧VHを発生する。

(もっと読む)

201 - 220 / 645

[ Back to top ]