Fターム[5F092BA22]の内容

ホール/MR素子 (37,442) | ホール素子 (486) | ホール素子の動作部の平面形状 (84) | 十字形 (39)

Fターム[5F092BA22]に分類される特許

1 - 20 / 39

半導体装置、および、その製造方法

【課題】電流により発生する磁場を化合物半導体回路で集約して検出することができる小型で、高感度かつ高精度な電流センサを実現すること。

【解決手段】半導体回路(LSI回路)と化合物半導体回路(ホール素子を有する化合物半導体素子)とが形成された基板に、さらに、化合物半導体素子の直上に、該直下の化合物半導回路に対して磁束密度を増加させるための所定の形状からなる電気配線(コ字型または馬蹄型の形状を呈した金属配線)を形成し、この電気配線に被検出電流を流すようにした。

(もっと読む)

電流センサ

【課題】所望のS/Nとなる電流センサを提供する。

【解決手段】被測定電線21が挿通される磁気コア2と、磁気コア2に配置されたホール素子3と、磁気コア2に巻回された負帰還コイル4と、ホール素子3の電流入力端子3a,3aに直流定電流I2を供給する電源部5と、ホール素子3の電圧出力端子3b,3b間に発生する出力電圧V1に基づいて負帰還コイル4に負帰還電流I3を供給する電流生成部6と、負帰還コイル4に接続されて負帰還電流I3を検出電圧V2に変換して出力する終端抵抗7とを備え、測定電流I1の非検出時における検出電圧V2に含まれる予め規定された周波数でのノイズのパワースペクトル密度を算出しつつ、電源部5に対する制御を実行して直流定電流I2の電流値を変更することにより、算出しているパワースペクトル密度を予め規定された基準密度DErefに一致させる補正処理を実行する処理部9を備えている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】モールド成型によりパッケージ化されてなる半導体装置において、パッケージからのストレスに起因する半導体デバイスの特性変化のさらなる抑制を図る。

【解決手段】Si−LSI202a、202b全体をSiO2膜205とSiN膜206とで覆い、2つのSi−LSI202a、202b間のSi基板201表面に、化合物半導体デバイスからなるホール素子208の感磁部を形成する。ホール素子208とSi−LSI202a、202bとを金属配線210で接続した後、SiN膜211、SiO2膜212を形成して平坦化し、その上にAl配線213を形成する。基板上面からみて、Al配線213の、ホール素子208と重なる領域にエッチング溶液注入穴214を形成しここからエッチング溶液を注入してAl配線213の下部のSiO2膜212を除去し中空部215を形成する。

(もっと読む)

磁気センサ

【課題】感磁部と磁気感度および抵抗の調整を可能とするトリミング部とを備えた磁気センサを提供すること。

【解決手段】磁気センサは、基板26に設けられた化合物半導体からなる十字形状パターンの感磁部21を備え、入力端子21a,21bと出力端子21c,21dの少なくとも一方の端子21a,21dに、化合物半導体を有するトリミング部23a,23bが接続電極24を介して直列接続されている。ウェハプロービングを行いながら、接続電極24を介して感磁部21に直列接続された入力端子側のトリミング部23aを、レーザートリミングすることにより、定電圧駆動における磁気感度の調整を可能とし、同様に出力端子側のトリミング部23bをトリミングすることにより出力抵抗の調整を可能にした。

(もっと読む)

ホールセンサ

【課題】チップサイズの増加がなく、高感度でオフセット電圧の除去が可能なホール素子を提供する。

【解決手段】ホール素子は十字形状のホール素子感受部を有し、4つの凸部先端中央部にホール電圧出力端子を配置し、各凸部側面にはホール電圧出力端子とは独立に制御電流入力端子を配置する。このときホール電圧出力端子幅を小さくし、制御電流入力端子幅を大きくする。

(もっと読む)

複合半導体素子、その製造方法、磁気センサ及び画像形成装置

【課題】化合物半導体ウェハー素材を用いてホール素子などを作成するに当たり、無駄となる部分が多くコストの増加を招いていた。

【解決手段】 複合半導体素子が、基板(11)と、基板上(11)に備えられ有機材料を主材料とする平坦化層(14)と、例えばホール素子を構成する化合物半導体素子を含み平坦化層(14)上にボンディングされた半導体薄膜(12)を有する。化合物半導体薄膜(12)との電気的接続のための金属配線膜(23)をさらに備え、化合物半導体薄膜(12)と金属配線膜(23)との間に、より高い不純物濃度の化合物半導体層(17)を介在させても良い。

(もっと読む)

ホール素子

【課題】従来の位置検出装置では、第1のホール素子および第2のホール素子をそれぞれ別のチップ内に形成していた。従って、2チップを使用しているため、コストが高く、パッケージを小さくできないという問題があった。また、ダイボンドの位置ずれにより、前記第1のホール素子と前記第2のホール素子との間のギャップ精度が悪いという問題もあった。

【解決手段】本発明に係るホール素子では、前記第1のホール素子および前記第2のホール素子が1チップ内に形成される。また、適正なレイアウトによりチップサイズを縮小することができる。これにより、パッケージサイズを小さくすることができる。さらに、本発明に係るホール素子では、前記第1のホール素子および前記第2のホール素子がリソグラフィーにより同一チップに同時に形成されるので、前記第1のホール素子と前記第2のホール素子との間のギャップ精度を向上させることができる。

(もっと読む)

ゲルマニウム・ホール・プレートを有する集積ホール効果素子

集積回路及びその集積回路を製造する方法は、ゲルマニウム・ホール・プレートを有するホール効果素子を提供する。このゲルマニウム・ホール・プレートは、シリコンと比較して増大した電子移動度を提供し、それ故、より高感度なホール効果素子を提供する。 (もっと読む)

方位角計測装置

【課題】ホール素子を用いて検出された地磁気に基づいて、方位を計測する。

【解決手段】補正値記憶部7には、x軸ホール素子HExおよびy軸ホール素子HEyの基準値Lx、Lyが携帯端末10の使用状態ごとに記憶され、補正計算部6は、携帯端末10の使用状態に対応した基準値Lx、Lyを用いることにより、x軸ホール素子HExおよびy軸ホール素子HEyの出力増幅値Dx、Dyを補正し、地磁気の各軸成分に比例した値α、βだけを取り出す。

(もっと読む)

磁界センサ

【課題】 調整可能なグラフェンを用いた磁界センサを提供する。

【解決手段】 グラフェンセンス層を採用する磁界センサであって、センス層内を移動する電荷キャリアに作用するローレンツ力が、グラフェン層内を移動する電荷キャリアの経路に変化をもたらす。磁界の存在を示すこの経路の変化を検出することができる。センサは、非磁性の電気的絶縁材料によってグラフェン層から分離される1つまたは複数のゲート電極を含む。ゲート電極へのゲート電圧の印加により、グラフェン層の電気抵抗が変化し、このゲート電圧の印加を用いて、センサの感度および速度を制御することができる。

(もっと読む)

ホール素子

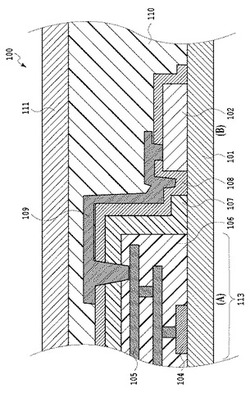

【課題】感磁面に対して平行な磁場を検出するホール素子において、磁気増幅効果を損なうことなく、小型化および薄型化を実現すること。

【解決手段】ホール素子100は、感磁面が化合物半導体で構成されたホール素子部110と、ホール素子部110の感磁面111と平行に配置された磁気収束板120とを備える。感磁面111の幅をW、磁気収束板120の幅をA、長さをB、厚みをDとする。感磁面111と磁気収束板120との間のギャップをCとする。磁気増幅率は長さBに比例しており、アスペクト比B/Aが3以上となる形状では磁気増幅率が1.5倍を超え、更にBを300μmとしたB/A=5の場合には磁気増幅率が3倍に達する。また、A/W<3を満足するよう磁気収束板120の幅Aを狭めてゆくと、磁束の集中する磁気収束板120の側面部が感磁面111に近づくため、磁気増幅率の増加が著しい。

(もっと読む)

磁電変換素子の製造方法

【課題】磁電変換素子を極めて容易に短時間で作業性の優れた連続方法で製造することを可能とする。

【解決手段】基板が磁性体の磁電変換素子用ペレットを、リードフレームに接続する工程を備える磁電変換素子の製造方法は、複数の半導体素子を形成したウエハの裏面に樹脂層を設ける工程と、樹脂層を設けたウエハをダイシングして個別の磁電変換素子用ペレットにする工程と、磁電変換素子用ペレットを、樹脂層を介してリードフレームに固着する工程と、磁電変換素子用ペレット上の電極をリードフレームと結線する工程とを具え、該樹脂層が厚み1〜50μmであり、前記樹脂層の樹脂がガラス転移点60〜160℃、接着活性温度170〜350℃、および熱伝導率0.2〜3.5W/m/℃を有している。

(もっと読む)

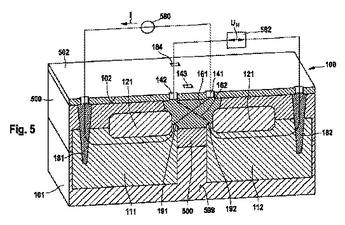

ホールセンサ素子および磁界を測定する方法

本発明は、ホールセンサ素子に関する。当該基板は、主要表面を備えた基板と、前記主要表面から前記基板内まで延在している、導電性のアクティブ領域と、前記アクティブ領域と、第1の下方のコンタクト面で接触している、基板内の導電性の第1埋設層とを有している。別の観点では、本発明は、上記のホールセンサ素子を用いた磁界の測定方法を実現する。ここでは、電気的な測定電流は主要表面での第1の上方コンタクト電極と第1の下方コンタクト面との間で、アクティブ領域を通って導かれる。第1の下方コンタクト面と第1の上方コンタクト電極との間の接続線に対して傾斜して延在する区間に沿って、アクティブ領域でホール電圧が検出される。択一的に、測定電流が上記の区間に亘って、アクティブ領域を通って導かれ、ホール電圧が第1の上方コンタクト電極と第1の下方コンタクト面との間で検出される。  (もっと読む)

(もっと読む)

半導体ホール素子

【課題】デザインルールを変更することなく電極パッドの配置を変更することによって、ペレット取数を増加させることを可能にすること。

【解決手段】基板11上に設けられた導電層からなる十字型パターンである感磁部の周辺に電極パッド14a,14b,14c,14dが配置されている。基板上11の素子形状は長方形であり、この長方形の平面内に配置された感磁部12の十字型パターンの一方の一対の端子12a,12bは、引き回し電極13a,13bを介して電極パット14a,14bに接続されている。十字型パターンの他方の一対の端子12c,12dは、引き回し電極を介することなく電極パット14c,14dに接続されている。長方形の長辺に沿って、電極パット14aと、電極パット14cと、電極パット14dと、電極パット14bが、この順に横一列に配置されている。

(もっと読む)

半導体磁気センサー

【課題】従来よりも高感度かつ小面積の半導体磁気センサーを低コストで提供すること。

【解決手段】半導体基板上に化合物半導体から構成されたエピタキシャル成長層を分割することにより形成された3つのメサ領域が形成されている。メサ10Cはホール素子部100として使用される。メサ10A及びメサ10Bは、それぞれホール素子部100からの出力を増幅するための電界効果トランジスタ部200A、200Bとして使用される。メサ10Cとメサ10B、メサ10Cとメサ10Aはそれぞれ隣接して設けられているが、これらのメサ同士はエッチングにより分断されることによって絶縁されている。電圧検出用電極20A及び20Bは、それぞれ電界効果トランジスタ部200A及び200Bのゲート電極40A、40Bに直接接続されている。

(もっと読む)

オフセットが低減されている集積センサアレイ

【課題】コストを大幅に増加させることなく精度を向上したCMOSセンサを提供する。

【解決手段】一実施形態におけるCMOSセンサシステムにおいて向上した精度を提供する方法及びシステムは、相補型金属酸化膜半導体基板112上の第1の端子114及び第2の端子116を有する複数のセンサ素子と、第1の端子114を電源に選択的に接続すると共に、該第1の端子114を読出し回路108に選択的に接続するように構成される第1の複数のスイッチと、第2の端子116を電源に選択的に接続すると共に、該第2の端子116を読出し回路108に選択的に接続するように構成される第2の複数のスイッチとを含む。

(もっと読む)

磁場センサ

【課題】平面的・空間的に分布し且つ動的な磁場の測定を実現可能とする磁気センサを提供する。

【解決手段】薄膜ホール効果素子THD、駆動回路DV、読出回路RD、検出制御配線SL1からSLm、検出出力配線RL1からRLnで構成された複数の要素回路PX11からPXmnをマトリクス状に配置して磁場センサ1を構成する。

(もっと読む)

半導体薄膜素子の製造方法

【課題】電子移動度の低下を最小限に抑えつつ、抵抗の温度依存性を低減させ、さらに薄膜製作の再現性や制御性に優れた、n型ドーパントとしてSnを含むInSb薄膜を用いた半導体薄膜素子の製造方法を提供する。

【解決手段】基板上に直接的にまたは有機物接着層もしくはバッファ層を介して間接的に積層されたInSbを含む化合物半導体薄膜層からなる動作層中もしくは該動作層に隣接したIII−V族化合物半導体層をMBE法により形成する際に、ドーパントとしてSnを、基板温度380℃〜400℃の範囲、SnのKセル温度500℃以上かつ1000℃以下の範囲でドーピングする。

(もっと読む)

電流センサ

【課題】オフセットを動的に除去できかつ応答性が高い電流センサを提供すること。

【解決手段】電流センサ1は、第1ホール素子11から出力される信号Sig(HE1)のゲインに、第2ホール素子21から出力される信号Sig(HE2)のゲインが一致するように、信号Sig(HE2)のゲインを調整する補正値演算回路33および波形修正回路34と、ゲインを調整した信号Sig(HE2)および極性が反転されてかつゲインを調整した信号dSig(HE2)に基づいて、オフセット量を検出する第2センサ信号オフセット検出回路35と、信号Sig(HE2)からオフセット量を除去する減算器37と、オフセット量が除去された信号Sig(HE2)に基づいて、信号Sig(HE1)のオフセット量を検出する第1センサ信号オフセット検出回路38と、信号Sig(HE1)からオフセット量を除去する減算器40と、を備える。

(もっと読む)

電流センサ

【課題】オフセットを動的に除去でき、かつ、応答性が高い電流センサを提供すること。

【解決手段】電流センサ1は、出力導線2に流れる電流を検出して出力する第1電流センサ10と、第1電流センサの出力信号を第1デジタルデータとして記憶する第1記憶部32と、第1デジタルデータが所定値以下となる第1区間を検出する第1区間検出部33と、出力導線2に流れる電流を検出して所定のオフセット量を除去して出力する、トリミング方式の第2電流センサ20と、第2電流センサ20の出力信号を第2デジタルデータとして記憶する第2記憶部42と、第1区間に相当する第2区間の第2デジタルデータに基づいてオフセット量を演算するオフセット演算部43と、このオフセット量を所定のオフセット量として設定するオフセット設定部44と、を備える。

(もっと読む)

1 - 20 / 39

[ Back to top ]