Fターム[5F101BA12]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | FG型 (6,485) | FG形状構造 (858)

Fターム[5F101BA12]の下位に属するFターム

埋め込みFG、溝 (45)

CG側壁 (37)

FGの突起 (84)

複数FG(単一メモリセル内) (90)

FG接続 (271)

PN接合(FG内の) (5)

Fターム[5F101BA12]に分類される特許

321 - 326 / 326

分離領域上に消去ゲートを有する不揮発性メモリ

本発明は、不揮発性メモリ装置及びそのような装置の製造方法を提供する。この装置は、浮遊ゲート(16)と、制御ゲート(19)と、分離した消去ゲート(10)とを備える。消去ゲート(10)は、基板(1)内に設けられた分離領域(2)中に、又はその上に設けられる。そのため消去ゲート(10)は、セル・サイズを増加させない。消去ゲート(10)と浮遊ゲート(16)との間の容量は、制御ゲート(19)と浮遊ゲート(16)との間の容量に比べて小さく、消去ゲート(10)と浮遊ゲート(16)との間の酸化物層を介してファウラー・ノルドハイム・トンネルによって浮遊ゲート(16)の帯電が消去される。  (もっと読む)

(もっと読む)

ナノ構造単層の形成方法および形成デバイスならびにかかる単層を含むデバイス

ナノ構造配列の形成またはパターニング法が提供される。この方法は、ナノ構造会合基を含んでなるコーティング上での配列形成、レジストを使用するパターニングおよび/または配列形成を促進するデバイスの使用を含む。またナノ構造配列を含むデバイス(例えばメモリーデバイス)のように、ナノ構造配列の形成のための関連デバイスも提供される。 (もっと読む)

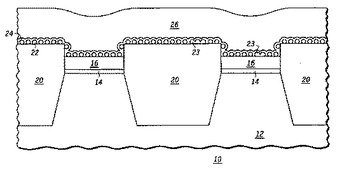

改良された表面形状を用いるメモリ構造の形成方法及びその構造。

半導体装置10のゲートカップリング比を増大させるため、超微細結晶等の個別素子22が浮遊ゲート16上に析出される。一実施形態において、個別素子22は、蒸気相中で予め形成され、静電気力によって半導体装置10に吸着される。一実施形態において、個別素子22は、それらが吸着されるチャンバとは異なるチャンバ内で予め形成される。更に別の実施例において、同じチャンバが全ての析出工程に使用される。界面層17は、必要に応じて、浮遊ゲート16と個別素子22との間に形成される。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置、その製造方法、電子カード及び電子装置

【課題】 カップリング比のばらつきを小さくできるNAND型EEPROMを提供する。

【解決手段】 メモリセルの電荷蓄積層17の上層導電部23は、互いに間を設けて形成された一対の立上り部27により構成される内側面29及び外側面31を有する。内側面29側には底面高さ調節層43があり、外側面31側には素子分離絶縁層5がある。このため、半導体基板9の位置(A)のメモリセルと位置(B)のメモリセルとで、立上り部27の高さが異なっていても、電荷蓄積層17と制御ゲートCGとが対向する領域の面積を同じにできる。

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

垂直方向の突起部を有するフローティングゲート構造

基板面から離れて延在する突起部を有するフローティングゲート構造を開示する。この突起部によって、フローティングゲートとコントロールゲートとを結合するための増加した表面積をフローティングゲートに提供することが可能となる。1つの実施形態では、フローティングゲートの個々の側面でワードラインが下方へ延在して、同じ列の隣接するフローティングゲートを遮蔽する。別の実施形態では、突起部を有するフローティングゲートの組立て製造処理工程を開示する。残りのフローティングゲートに対して自己位置合せを行うために突起部を形成してもよい。  (もっと読む)

(もっと読む)

321 - 326 / 326

[ Back to top ]