Fターム[5F101BB04]の内容

不揮発性半導体メモリ (42,765) | 制御 (5,368) | 制御装置 (5,154) | CGを有するもの (4,139) | オフセットゲート (220)

Fターム[5F101BB04]に分類される特許

1 - 20 / 220

半導体装置

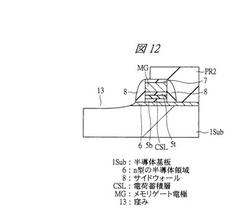

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置(不揮発性メモリを有する半導体装置)の特性を向上させる。

【解決手段】本発明の半導体装置は、制御ゲート電極CGと半導体基板との間に形成された絶縁膜3と、メモリゲート電極MGと半導体基板との間および制御ゲート電極CGとメモリゲート電極MGとの間に形成された絶縁膜5であって、その内部に電荷蓄積部を有する絶縁膜5と、を有する。この絶縁膜5は、第1膜5Aと、第1膜5A上に配置された電荷蓄積部となる第2膜5Nと、第2膜5N上に配置された第3膜5Bと、を有し、第3膜5Bは、制御ゲート電極CGとメモリゲート電極MGとの間に位置するサイドウォール膜5sと、メモリゲート電極MGと半導体基板との間に位置するデポ膜5dとを有する。かかる構成によれば、絶縁膜5の角部における距離D1を大きくすることができ、電界集中を緩和できる。

(もっと読む)

半導体記憶装置およびデータ書込み方法

【課題】MOS構造を有する各メモリセルにおいて信頼性が高い2ビットのデータの記憶が容易な半導体記憶装置およびデータ書込み方法を提供する。

【解決手段】MOS構造を有するメモリセル10は、ゲート電極13の第1半導体領域121側に設けられた第1記憶部141と、ゲート電極13の第2半導体領域122側に設けられた第2記憶部142とを有する。第1記憶部141に電子を保持させる第1電荷移動ステップと、第2記憶部142に電子を保持させる第2電荷移動ステップとを交互に行うことで、第1記憶部141および第2記憶部142の双方に所定量の電子を保持させる。

(もっと読む)

半導体不揮発性メモリ及びデータ書き込み方法

【課題】データ書き込み時における書き込み回数を減らし、且つ読み出し精度を高めることが可能な半導体不揮発性メモリ及びデータ書き込み方法を提供する。

【解決手段】書き込むべきデータの値に対応した量の電荷を電荷蓄積部に注入することによって書き込みを行うデータ書き込み手段を有し、データ書き込み手段によるデータの書き込みに先立ち、電荷蓄積部各々から読み出し電流を送出させ、読み出し電流が最大読み出し電流閾値よりも大となる電荷蓄積部に、この読み出し電流が最大読み出し電流閾値を下回るまで電荷を注入する初期化書き込みを行う。

(もっと読む)

双方向分割ゲートNANDフラッシュメモリ構造及びアレイ、そのプログラミング方法、消去方法及び読み出し方法、並びに、製造方法

【課題】NANDフラッシュメモリ構造において、各セルについてのライン数を削減して、不揮発性メモリデバイスのピッチを改善すること。

【解決手段】分割ゲートNANDフラッシュメモリ構造が、第1伝導型の半導体基板上に形成される。このNAND構造は、第2伝導型の第1領域と、基板内にこの第1領域から間隔をおいて配置されてこの第1領域との間にチャネル領域を定める、第2伝導型の第2領域と、を備える。各々が上記チャネル領域から絶縁された複数の浮動ゲートが、互いに間隔をおいて配置される。各々が上記チャネル領域から絶縁された複数の制御ゲートが、互いに間隔をおいて配置される。該制御ゲートの各々は、1対の浮動ゲートの間にあって該1対の浮動ゲートに容量的に接続される。各々が上記チャネル領域から絶縁された複数の選択ゲートが、互いに間隔をおいて配置される。該選択ゲートの各々は、1対の浮動ゲートの間にある。

(もっと読む)

導電性側壁スペーサを有する不揮発性メモリ装置及びその製造方法

【課題】従来の窒化膜側壁を電荷トラップ媒体に利用する場合の信頼性劣化を改善した不揮発性メモリ装置を提供する。

【解決手段】半導体基板21上のゲート絶縁膜22Aと、該ゲート絶縁膜上に順に積層して形成された第1電極膜23、第2電極膜24、及びハードマスク膜25を有するゲート100と、該ゲートの第1電極膜23及び第2電極膜24の両側壁に形成された一対の再酸化側壁スペーサ27と、該再酸化側壁スペーサ及びゲート100のハードマスク膜25の両側壁上に形成された一対の側壁スペーサ28Aと、一対の側壁スペーサ28A上に形成された、電荷を捕獲及び放出する一対の導電性側壁スペーサ29Bと、半導体基板21内に形成された一対のLDD領域26と、半導体基板21内に形成されたソース/ドレイン領域30とを備え、導電性側壁スペーサ29Bが、ゲート100及び側壁スペーサ28Aよりも低い高さを有する。

(もっと読む)

半導体装置

【課題】消去特性と消去ディスターブ特性との双方を向上することが可能な、MONOS型メモリセルなどの半導体装置を提供する。

【解決手段】半導体基板SUBの主表面に形成される第1のゲート電極CGと、主表面上において第1のゲート電極CGと隣接するように形成された第2のゲート電極MGと、第2のゲート電極MGと半導体基板SUBとに挟まれた領域から、第1のゲート電極CGと第2のゲート電極MGとに挟まれた領域に連なるように延びる絶縁膜ONOと、第1および第2のゲート電極CG,MGの真下のチャネル領域を挟むように、主表面に形成される1対のソース/ドレイン領域NR1,NR2とを備える。上記ソース領域NR1は、第1のソース領域N11および第2のソース領域N12を含んでいる。上記第2のソース領域N12は第1のソース領域N11よりも主表面から深い領域に形成されている。上記第1のソース領域N11と第2のソース領域N12とに含まれる不純物の材質が異なっている。

(もっと読む)

半導体装置およびその製造方法

【課題】選択用トランジスタのゲート電極と記憶用トランジスタのゲート電極との間の耐圧を確保し、かつ閾値電圧の変動が抑制されたMONOS型メモリセルを提供する。

【解決手段】主表面SBSを有する半導体基板SUBと、主表面SBS上に形成された第1のゲート電極CGと、主表面SBS上において第1のゲート電極CGと隣接するように形成された第2のゲート電極MGと、第2のゲート電極MGと半導体基板SUBとに挟まれた領域から、第1のゲート電極CGと第2のゲート電極MGとに挟まれた領域に連なるように延びる第1の絶縁膜ONOとを備える半導体装置である。上記第2のゲート電極MGの最上面MGSは第1のゲート電極CGの最上面CGSより低くなっている。上記第2のゲート電極MGの最上面MGSは主表面SBSに沿うように形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の電気的性能および信頼性を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGは、金属膜6aと金属膜6a上のシリコン膜6bとの積層膜で形成されたメタルゲート電極であり、金属膜6aの上端部には、金属膜6aの一部が酸化することで金属酸化物部分17が形成されている。スプリットゲート型の不揮発性メモリの制御ゲート電極は、金属膜4aと金属膜4a上のシリコン膜6bとの積層膜で形成されたメタルゲート電極である。

(もっと読む)

半導体装置およびその製造方法

【課題】FMONOSメモリセルとCMOSトランジスタが共存する半導体装置において、トランジスタの駆動電流を高めるとともにFMONOSメモリセルとしての機能を確保する半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、主表面上に形成された、チャネルを有するMONOS型メモリセルと、主表面上に形成されたnチャネル型トランジスタと、主表面上に形成されたpチャネル型トランジスタとを備える半導体装置である。上記MONOS型メモリセル、nチャネル型トランジスタおよびpチャネル型トランジスタの上面に接するように窒化膜CS1、CS2が形成されている。上記窒化膜CS1、CS2はMONOS型メモリセル、nチャネル型トランジスタおよびpチャネル型トランジスタのチャネルに応力を付加する。

(もっと読む)

不揮発性半導体記憶装置とその製造方法

【課題】メモリセルが3次元的に積層された不揮発性半導体記憶装置で、メモリセルの投影面積を小さくすることができ、従来の平面型のフローティングゲート構造と類似の構造の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、シート状のチャネル半導体膜111の高さ方向に複数のメモリセルMCを有するメモリストリングが基板上にほぼ垂直に配置される。フローティングゲート電極膜109は、第2の方向に延在し、トンネル誘電体膜110を介してチャネル半導体膜111の第1の主面上に形成される。制御ゲート電極膜103は、第1の方向に延在する共通接続部1031と、共通接続部1031から第2の方向に突出し、フローティングゲート電極膜109の上部または下部に電極間絶縁膜108を介してメモリセルMCごとに設けられる電極構成部1032と、を有する。

(もっと読む)

半導体記憶装置

【課題】総工程数を低減することができ、コストを低廉なものにする半導体記憶装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体記憶装置10は、半導体基板13と、第1不純物領域17と、第2不純物領域15と、第1不純物領域17と第2不純物領域15との間に形成されたチャネル領域75と、チャネル領域75が位置する半導体基板13の主表面上のうち、第1不純物領域17側の主表面上に形成された第1ゲート42と、チャネル領域75が位置する半導体基板13の主表面上にうち、第2不純物領域側15の主表面上に第2絶縁膜44を介して形成された第2ゲート45と、第1ゲート45に対して第2ゲート42と反対側に位置する半導体基板の主表面上に位置し、第1ゲート42の側面上に形成された第3絶縁膜46と、第3絶縁膜46とその直下に位置する半導体基板13との界面が、第2絶縁膜44とその直下に位置する半導体基板の主表面との界面より上方に位置する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】特性を向上させる不揮発性メモリを有する半導体装置を提供する。

【解決手段】半導体装置を、制御ゲート電極CGと、制御ゲート電極CGと隣合うように配置されたメモリゲート電極MGと、絶縁膜3と、その内部に電荷蓄積部を有する絶縁膜5と、を有するよう構成する。このうち、メモリゲート電極MGは、絶縁膜5上に位置する第1シリコン領域6aと、第1シリコン領域6aの上方に位置する第2シリコン領域6bと、を有するシリコン膜よりなり、第2シリコン領域6bは、p型不純物を含有し、第1シリコン領域6aのp型不純物の濃度は、第2シリコン領域6bのp型不純物の濃度よりも低く構成する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】対向する二つの記憶素子のコントロールゲートのゲート長に起因する記憶素子の特性のばらつきを抑制する。

【解決手段】上記の課題を解決するために、不揮発性半導体記憶装置(1)を以下のように構成する。第1不揮発性メモリセル(1a)は、第1チャネル領域(11a)と、第1フローティングゲート(5a)と、第1コントロールゲート(6a)とを含むものとする。また、第2不揮発性メモリセル(1b)は、第2チャネル領域(11b)と、第2フローティングゲート(5b)と、第2コントロールゲート(6b)とを含むものとする。ここにおいて、第1チャネル領域(11a)は、第1フローティングゲート側チャネル領域(13a)と、第1コントロールゲート側チャネル領域(12a)とを備え、第1コントロールゲート側チャネル領域(12a)は不純物濃度が濃い高濃度ポケット領域(10)を備える。

(もっと読む)

電界効果トランジスタ、その使用、およびその製造方法

【課題】好適な電界効果トランジスタ、その使用、およびその製造方法を提供すること。

【解決手段】窪み(72)に沿ってドープチャネル領域が配置された半導体基板(10)を有する、縦型電界効果トランジスタが説明される。「埋め込まれた」接続領域(18、54)は、半導体基板(10)の表面に達する。第2の接続領域(16)が、同一の表面の窪みの開口部の近傍内に配置される。好ましくは、分離窪み(70、74、76)が、チャネル領域と導電性配線(54)との間、および電界効果トランジスタと隣接する電気部品との間に製造される。電界効果トランジスタは優れた電気特性を有し、容易に製造される。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGとp型ウエルPW1との間および制御ゲート電極CGとメモリゲート電極MGとの間には、絶縁膜5が形成されている。この絶縁膜5のうち、メモリゲート電極MGの下面と半導体基板1の上面との間の部分は、酸化シリコン膜9a,9bと酸化シリコン膜9a,9bに挟まれた窒化シリコン膜10aとを有している。絶縁膜5のうち、制御ゲート電極CGの側面とメモリゲート電極MGの側面との間の部分は、酸化シリコン膜6aからなり、窒化シリコン膜10aを有していない。

(もっと読む)

半導体不揮発性メモリ

【課題】 本発明は、不揮発性メモリ・セルにおける電荷貯蔵層を論理工程において形成する方法を提供する。

【解決手段】 論理工程において不揮発性メモリ・セルにおける電荷貯蔵層を形成する方法は、基板のアクティブ領域の上にセレクト・ゲートを形成するステップ、その基板のアクティブ領域に部分的に重なる長いポリシリコン・ゲートを形成するステップ、及びその長いポリシリコン・ゲートの間に電荷貯蔵層を充填するステップを含む。

(もっと読む)

半導体装置

【課題】不揮発性メモリと容量素子を有し、性能を向上させる半導体装置を提供する。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MG6nとp型ウエルPW1との間および制御ゲート電極CG4nとメモリゲート電極MG6nとの間には、内部に電荷蓄積層5bを有する絶縁膜5が形成されている。この絶縁膜5は、酸化シリコン膜5aと、その上に形成された窒化シリコン膜5bと、その上に形成された酸化シリコン膜5cと、その上に形成されかつ酸化シリコン膜5cよりも薄い絶縁膜5dとの積層膜からなる。この絶縁膜5dは、ポリシリコンからなるメモリゲート電極MG6nに接している。絶縁膜5dは、Hf,Zr,Al,Ta,Laのうちの少なくとも1種を含む金属化合物により形成されているため、フェルミピニングを生じることができ、誘電率が高い。

(もっと読む)

不揮発性半導体記憶装置

【課題】ホットキャリア注入によって書き換えを行うスプリットゲート型MONOSメモリにおいて、リテンション特性を向上させる。

【解決手段】メモリセルM00の選択ゲート電極は選択ゲート線SG0に接続され、メモリゲート電極はメモリゲート線MG0に接続される。また、ドレイン領域はビット線BL0に接続され、ソース領域はソース線SL0に接続される。さらに、メモリセルM00が形成されたp型ウエル領域にはウエル線WL0が接続される。メモリセルM00に書き込みを行うときは、ウエル線WL0を通じてp型ウエル領域に負電圧を印加しながら、ソースサイド注入方式による書込みを行う。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】不揮発性メモリのメモリセルは、p型ウエルPWの上部に絶縁膜3を介して形成された制御ゲート電極CGと、p型ウエルPWの上部に形成されて制御ゲート電極CGと隣合うメモリゲート電極MGと、メモリゲート電極MGとp型ウエルPWとの間および制御ゲート電極CGとメモリゲート電極MGとの間に形成されかつ内部に電荷蓄積部を有する絶縁膜5とを有している。メモリゲート電極MGは、ノンドープのシリコン膜6aと不純物を導入したシリコン膜6bとの積層膜により形成されている。シリコン膜6bの不純物濃度を高くすることでメモリゲート電極MGの抵抗を低くして不揮発性メモリの動作速度を向上させ、シリコン膜6aの不純物濃度を低くすることで、不揮発性メモリのデータ保持特性を向上させることができる。

(もっと読む)

1 - 20 / 220

[ Back to top ]