Fターム[5F101BB05]の内容

不揮発性半導体メモリ (42,765) | 制御 (5,368) | 制御装置 (5,154) | CGを有するもの (4,139) | スタックゲート(同一端部) (1,873)

Fターム[5F101BB05]に分類される特許

21 - 40 / 1,873

半導体装置の製造方法

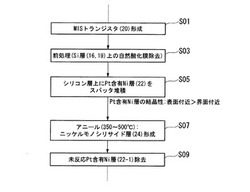

【課題】本発明は、シリコン層上に、抵抗値が低く、かつ平坦性の良好なニッケルモノシリサイド層を形成可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】基板に形成されたシリコン層を覆ように白金を含むニッケル層を堆積する工程であって、シリコン層に近い部分では遠い部分と比較して結晶性が低くなるように、白金を含むニッケル層を堆積する工程S05と、基板を加熱することで、シリコン層と白金を含むニッケル層との界面にニッケルモノシリサイド層を形成する工程S07と、を有する。

(もっと読む)

基板処理装置、半導体装置の製造方法及びプログラム

【課題】 酸素含有層を窒素濃度が高い酸窒化層又は窒化層に改質することで、ポリシリコン膜の耐酸化性を向上させる。

【解決手段】 酸素含有層が形成されたポリシリコン膜を有する基板が搬入される処理室と、処理室内に設けられ、基板を加熱する加熱部と、処理室内に窒素及び水素を含む処理ガスを供給するガス供給部と、処理室内に供給された処理ガスを励起する励起部と、加熱部により基板を所定の温度に加熱させ、ガス供給部により供給させた処理ガスを励起部により励起させ、励起した処理ガスを基板に供給させ、酸素含有層を酸窒化層又は窒化層に改質させるように、少なくとも加熱部、ガス供給部及び励起部を制御する制御部と、を備える。

(もっと読む)

半導体装置

【課題】微細化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、上面に、一方向に延び上方に突出した複数本のアクティブエリアが形成された半導体基板と、前記アクティブエリア間のトレンチの下部に埋め込まれた素子分離絶縁体と、第1の絶縁材料からなり、前記素子分離絶縁体の直上域に配置され、下部が前記トレンチ内に配置され、上部が前記アクティブエリアの上端よりも上方に突出した絶縁ブロックと、前記第1の絶縁材料とは異なる第2の絶縁材料からなり、前記半導体基板及び前記絶縁ブロックの上方に設けられた層間絶縁膜と、前記層間絶縁膜内に形成され、下端が前記アクティブエリアの上面に接続されたコンタクトと、を備える。前記コンタクトにおける前記絶縁ブロックの直上域に位置する部分の下面は、前記コンタクトにおける前記アクティブエリアの直上域に位置する部分の下面よりも上方に位置している。

(もっと読む)

メモリのプログラミング方法及びメモリアレイ

【課題】クリティカル・ディメンションの変動に鈍感であり且つ高速なメモリプログラミング方法等を提供する。

【解決手段】メモリの複数のメモリセルの夫々は、ウェルと、ソース及びドレイン領域と、記憶レイヤと、ゲートとを有する。メモリセルはマトリクス状である。同じ列ドレイン領域は同じビットラインへ接続し、同じ行ゲートは同じワードラインへ接続し、同じ列ソース領域は同じソースラインへ接続する。メモリは、いずれかのメモリセルへ電気的に接続されたワードラインへ第1の電圧を印加し、そのメモリセルへ電気的に接続されたビットラインへ少なくともプログラミング閾値だけ第1の電圧と異なる第2の電圧を印加し、そのメモリセルへ電気的に接続されたソースラインへ少なくともプログラミング閾値だけ第1の電圧と異なる第3の電圧を印加し、複数のメモリセルへ基板電圧を印加することによって、プログラミングされる。

(もっと読む)

半導体装置の製造方法

【課題】スプリットゲート構造の不揮発性メモリセルを有する半導体装置の製造歩留まりを向上させる。

【解決手段】半導体基板1のメモリセル領域に形成された選択ゲート電極CGの上部に酸化シリコン膜24および窒化シリコン膜25を形成した後、メモリマットのゲート長方向の最も外側(ダミーセル領域)に位置する選択ゲート電極CGの上部の酸化シリコン膜24および窒化シリコン膜25を除去することにより、メモリマットの端部を覆う下層レジスト膜12の段差をなだらかにし、下層レジスト膜12の上に形成されるレジスト中間層13の厚さの均一性を向上させ、局所的な薄膜化または消失を防止する。

(もっと読む)

半導体記憶装置

【課題】消費電力を低減出来る半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、選択トランジスタ、メモリセル、ワード線、セレクトゲート線、ドライバ回路12、ロウデコーダ11−0、及び検知回路16を備える。ドライバ回路12は、第1電圧Vss,Vccを出力する。ロウデコーダ11−0内の第1転送トランジスタは、ワード線及びセレクトゲート線の各々に関連付けられ、ドライバ回路12から出力された第1電圧を、ワード線及びセレクトゲート線に転送する。検知回路16は、データの消去時において、ビット線及び/またはソース線に印加される第2電圧を検知して、検知結果に応じてフラグを生成する。ドライバ回路12は、フラグが生成されたことに応答して第1電圧の値を変更して、第1転送トランジスタをカットオフさせる。

(もっと読む)

半導体装置

【課題】MONOS型不揮発性メモリの信頼性を向上させる。

【解決手段】メモリセルは、選択ゲート6とその一方の側面に配置されたメモリゲート8とを有している。メモリゲート8は、一部が選択ゲート6の一方の側面に形成され、他部がメモリゲート8の下部に形成されたONO膜7を介して選択ゲート6およびp型ウエル2と電気的に分離されている。選択ゲート6の側面にはサイドウォール状の酸化シリコン膜12が形成されており、メモリゲートの側面にはサイドウォール状の酸化シリコン膜9と酸化シリコン膜12とが形成されている。メモリゲート8の下部に形成されたONO膜7は、酸化シリコン膜9の下部で終端し、酸化シリコン膜12の堆積時にメモリゲート8の端部近傍の酸化シリコン膜12中に低破壊耐圧領域が生じるのを防いでいる。

(もっと読む)

半導体記憶装置及び半導体記憶素子

【課題】素子の面積を増大させることなく、かつ、コントロールゲート電圧を制御しなくとも、低電圧で書き込み量を大幅に増やすことが可能であり、また、安定して十分な書き込みを行うことが可能である不揮発性半導体装置を提供すること。

【解決手段】ドレインアバランシェホットエレクトロンにより書き込みを行う半導体記憶素子であって、第1導電型の半導体基板に形成された第2導電型の第1の半導体層と、前記第1の半導体層上に絶縁膜を介して設けられたフローティングゲートと、前記フローティングゲート下部の前記第1の半導体層の表面に形成されたチャネル領域と、前記チャネル領域に接触するように前記第1の半導体層上に設けられた第1導電型のソース領域及びドレイン領域とを有するMOSトランジスタであって、前記チャネル領域が2種類以上のキャリア濃度の分布をもつ半導体記憶素子とした。

(もっと読む)

酸化膜の形成方法

【課題】シリコン表面のプラズマ酸化により、界面準位密度が低くリーク電流の少ない高品質な酸化膜をシリコン表面上に形成する。

【解決手段】

酸化膜の形成方法は、KrとO2の混合ガス中にプラズマを形成することにより原子状酸素O*を発生させ、前記原子状酸素O*によりシリコン表面をプラズマ酸化するプラズマ酸化工程を含み、前記プラズマ酸化工程は、800〜1200mTorrの圧力範囲において実行される。

(もっと読む)

半導体装置の製造方法

【課題】

実施形態は、ゲート配線の抵抗が増大することを防止可能な半導体装置の製造方法を提供する。

【解決手段】

本実施形態の半導体装置の製造方法は、第1領域及び第2領域の半導体素子を形成するために、半導体基板、前記半導体基板上の第1絶縁膜、前記第1絶縁膜上の電荷蓄積層を積層し、所望のトレンチを形成する工程と、前記トレンチに素子分離膜を形成する工程と、前記素子分離膜及び前記電荷蓄積層上にストッパー膜30を形成する工程と、前記第2領域を第2絶縁膜で被膜し、前記第1領域の前記ストッパー膜30と前記素子分離膜をエッチバックする工程と、前記エッチバックされた素子分離膜、前記電荷蓄積層、第2領域の前記ストッパー膜30上に第3絶縁膜を介して配線を形成する工程とを備えることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】注入した導電性不純物により形成される結晶欠陥の密度を低減し、歩留まり率が向上するような半導体装置の製造方法を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板を加熱することにより、半導体基板の基板温度を200から500℃の間の所望の温度に維持すると同時に、半導体基板に導電性不純物をイオン注入法もしくはプラズマドーピング法を用いてドーピングし、ドーピングした導電性不純物を活性化させるための活性化処理を行う。

(もっと読む)

半導体装置

【課題】頻繁なリフレッシュ動作が不要で、正常な読み出しを行うことのできる2トランジスタ型のDRAMを備えた半導体装置を提供する。

【解決手段】本実施形態の半導体装置は、ゲートが第1配線に接続され、第1ソース/ドレインの一方が第2配線に接続された第1トランジスタと、ゲート絶縁膜、ゲート電極、および前記ゲート絶縁膜と前記ゲート電極との間に設けられしきい値を変調するしきい値変調膜を有するゲート構造と、第2ソース/ドレインとを備え、前記ゲート電極が前記第1トランジスタの前記第1ソース/ドレインの他方に接続され、前記第2ソース/ドレインの一方が第3配線に接続され、前記第2ソース/ドレインの他方が第4配線に接続された第2トランジスタと、を備えている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ワード線抵抗を低減し、かつ、周辺回路のトランジスタの特性変化を抑制することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、複数のメモリセルと、周辺回路とを備える。メモリセルは、半導体基板の上方に設けられたフローティングゲートと、フローティングゲート上に設けられたゲート間絶縁膜と、ゲート間絶縁膜上に設けられたコントロールゲートとを含む。周辺回路は、互いに電気的に接続されたフローティングゲートおよびコントロールゲートと、少なくともフローティングゲートとコントロールゲートとの間の電気的接触部分に設けられ該フローティングゲートと該コントロールゲートとの間の電気的接続を妨げない絶縁薄膜とを含むトランジスタを含む。複数のメモリセルは、コントロールゲート内に絶縁薄膜を含まない。メモリセルおよび周辺回路において、コントロールゲートの少なくとも上部はシリサイド化されている。

(もっと読む)

不揮発性半導体記憶装置の製造方法及び不揮発性半導体記憶装置

【課題】メモリセルの制御性を向上した不揮発性半導体記憶装置の製造方法及び不揮発性半導体記憶装置を提供する。

【解決手段】基板上に、第1積層体及び第2積層体を形成する工程と、第1積層体及び第2積層体を貫通する貫通孔を形成する工程と、貫通孔の第1部分の側壁にメモリ膜を形成し、貫通孔の第2部分及び第3部分の側壁にゲート絶縁膜を形成し、メモリ膜及びゲート絶縁膜の内側にチャネルボディを形成する工程と、チャネルボディの内側に酸化シリコンを含む第3絶縁層を形成し、第2部分と第3部分との境界部分を第3絶縁層により閉塞する工程と、第3部分の内側にシリコンを含む第1埋め込み部を形成する工程と、第1埋め込み部の一部と第3絶縁層の一部とを除去してチャネルボディを露出させる工程と、第3部分の内側における第1埋め込み部の上に、第1埋め込み部よりも不純物濃度が高いシリコンを含む第2埋め込み部を埋め込む工程と、を備える。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】メモリセルアレイおよび周辺回路の両方において、ワード線またはゲート電極を適切にシリサイド化することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板、半導体基板の上方に設けられたフローティングゲートと、フローティングゲート上に設けられたゲート間絶縁膜と、ゲート間絶縁膜上に設けられたコントロールゲートとを含む複数のメモリセル、および、互いに電気的に接続されたフローティングゲートおよびコントロールゲートを含むゲート電極と、ゲート電極のうちフローティングゲートの側面を被覆する側壁膜と、ゲート電極のうちコントロールゲートの側面を被覆し側壁膜上に設けられたスペーサとを備えたトランジスタを含む周辺回路、を備え、メモリセルおよび周辺回路において、コントロールゲートの上部はシリサイド化されている。

(もっと読む)

半導体装置

【課題】高品質な半導体装置を提供する。

【解決手段】第1の絶縁膜111、第1の電極112、第2の絶縁膜113、及び第2の電極114を含むゲート構造を有するメモリセルMCが複数設けられた記憶部11と、少なくとも外部100からのデータを受信し、記憶部にデータを供給する端子15と、第1の絶縁膜、第1及び第2の電極とを含むゲート構造を有し、電流経路の一端に第1の電圧が印加される第1導電型の第1のトランジスタ16a、一端が第1のトランジスタの電流経路の他端に接続され、他端が端子に接続される第1の抵抗素子16b、一端が端子及び第1の抵抗素子の他端に接続される第2の抵抗素子16c及び、ゲート構造を有し、電流経路の一端が第2の抵抗素子の他端に接続され、電流経路の他端に第2の電圧が印加される第2導電型の第2のトランジスタ16dを含む第1の回路16と、を備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】低いビットコストで積層化可能な不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、平行に配列された所定方向に延びる複数の半導体層と、半導体層の上に形成されたゲート絶縁層と、ゲート絶縁層の上に形成され所定方向に配列された複数の浮遊ゲートと、浮遊ゲートに隣接するゲート間絶縁層と、ゲート間絶縁層を介して所定方向の両側から浮遊ゲートに対向し複数の半導体層と交差する方向に延びる複数の制御ゲートとを有するセルアレイ層を複数層積層した不揮発性半導体記憶装置であって、積層方向に隣接するセルアレイ層において、下層のセルアレイ層の制御ゲートと、その上層のセルアレイ層の制御ゲートとが直交し、下層のセルアレイ層の浮遊ゲートと、その上層の半導体層との位置が整合している。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択メモリセルトランジスタに電荷を蓄積する際の電圧を従来よりも自由に設定し得る不揮発性半導体記憶装置を提案する。

【解決手段】不揮発性半導体記憶装置1では、選択メモリセルトランジスタ115に電荷を蓄積させる際、電圧の高い書き込み禁止電圧をP型MOSトランジスタ9bから印加し、電圧の低い書き込み電圧をN型MOSトランジスタ15aから印加して、選択メモリセルトランジスタ115又は非選択メモリセルトランジスタ116へ電圧を印加する役割分担を、P型MOSトランジスタ9b及びN型MOSトランジスタ15aに分けたことで、P型MOSトランジスタ9b及びN型MOSトランジスタ15aそれぞれのゲート電圧やソース電圧を個別に調整でき、最終的にゲート基板間電圧を例えば4[V]等に設定し得る。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置において、隣接するメモリセル積層構造間、及び、メモリセル積層構造−選択ゲート積層構造間のショートを防ぐことができる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコン基板上にゲート絶縁膜、浮遊ゲート電極、電極間絶縁膜および制御ゲート電極が順に積層されたメモリセル積層構造が複数隣接して配置され、隣接する前記メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置であって、前記メモリセル積層構造間のシリコン基板上に、前記メモリセル積層構造の側壁に形成されたシリコン酸化膜より厚いシリコン酸化膜が形成されている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】信頼性および読み出し速度の向上を図ることができる半導体記憶装置及びその製造方法を提供する。

【解決手段】電極膜WLと層間絶縁膜14を交互に複数積層して積層体を形成する工程と、前記積層体の積層方向に延びる複数の貫通孔18を形成する工程と、前記貫通孔の内部に電荷蓄積膜23と、絶縁膜24aと、ゲルマニウムを用いた第1の膜25と、アルミニウムを用いた第2の膜27を形成する工程と、置換熱処理で、前記第1の膜と前記第2の膜を置換し前記第2の膜の前記絶縁膜とは反対の側にゲルマニウムを成長させて半導体ピラーSPを形成する工程と、前記積層体の上方に配線を形成する工程と、前記置換された第2の膜を選択的に除去することで、前記絶縁膜と前記半導体ピラーとの間に空隙24bを形成する工程と、を備えている。前記半導体ピラーの上端部は、前記積層体の上方に形成された前記配線により支えられる。

(もっと読む)

21 - 40 / 1,873

[ Back to top ]