Fターム[5F101BB05]の内容

不揮発性半導体メモリ (42,765) | 制御 (5,368) | 制御装置 (5,154) | CGを有するもの (4,139) | スタックゲート(同一端部) (1,873)

Fターム[5F101BB05]に分類される特許

81 - 100 / 1,873

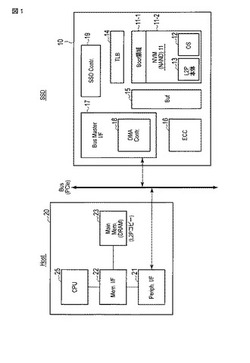

情報処理装置及び半導体記憶装置

【課題】製造コストの低減に対して有利な情報処理装置及び半導体記憶装置を提供する。

【解決手段】実施形態によれば、ホスト装置と、前記ホスト装置にバスを介して接続された半導体記憶装置とを備える情報処理装置であって、前記ホスト装置は、メインメモリを備え、前記半導体記憶装置は、第1の論物変換テーブル及びデータを格納する不揮発性半導体メモリと、前記第1の論物変換テーブルの一部である第2の論物変換テーブルを格納する記憶部と、前記第2の論物変換テーブルを参照し前記不揮発性半導体メモリにアクセスする制御部とを備え、前記第1の論物変換テーブルの少なくとも一部が前記メインメモリ上にコピーされ、前記第2の論物変換テーブルに前記制御部がアクセスする論理アドレス又は物理アドレスが登録されていない場合、前記メインメモリ上の第3の論物変換テーブルの一部が前記第2の論物変換テーブルにコピーされる。

(もっと読む)

不揮発性半導体記憶装置

【課題】高速で動作し得る不揮発性半導体記憶装置を提供する。

【解決手段】選択トランジスタとメモリセルトランジスタMTとを有するメモリセルMCがマトリクス状に配列されて成るメモリセルアレイ10と、ビット線BLの電位を制御する列デコーダ12と、第1のワード線WL1の電位を制御する電圧印加回路14と、第2のワード線WL2の電位を制御する第1の行デコーダ16と、ソース線SLの電位を制御する第2の行デコーダ18とを有し、列デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されており、第1の行デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されている。ビット線と第2のワード線とが高速で制御され得るため、メモリセルトランジスタに書き込まれた情報を高速で読み出すことができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】ビット線接続部の微細化を実現する不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、p型の半導体基板101と、半導体基板101内に形成され、メモリセルのビット線とセンスアンプ部を接続するビット線接続トランジスタHTkが形成されるp型の第1のPウェル102と、第1のPウェル102を囲み、第1のPウェル102を半導体基板101から電気的に分離するn型の第1のNウェル103と、を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】正確に書き込み動作を行うことができる不揮発性半導体記憶装置を提供する。

【解決手段】

複数の素子分離絶縁膜は、半導体層中に形成され、第1方向を長手方向とする。複数の素子形成領域は、素子分離絶縁膜により分離して形成される。素子形成領域にはメモリストリングが形成される。複数の素子形成領域群が素子形成領域により構成される。メモリセルアレイは、第1方向と直交する第2方向において、前記素子形成領域群の間隔が前記素子形成領域群の中の前記素子形成領域の間隔より大きくされている。制御回路は、前記メモリセルアレイに対する書き込み動作を、前記素子形成領域群ごとに実行する。

(もっと読む)

半導体装置の製造方法

【課題】ラインスペースパターンと幅の広いパターンが混在する場合であっても、両パターンを精度よく加工する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、被加工層上にハードマスク層を形成する。その上に第1のマスク層を形成し、第1のマスク層をパターニングする。第1のマスク層が除去された領域にカーボン層を形成しパターニングする。カーボン層を部分的にエッチングし、カーボン層のパターン幅を縮小する。第1のマスク層と同一材料の第2のマスク層を形成し、エッチングによりカーボン層のパターンの両側面に第2のマスク層を残存させる。第2のマスク層のパターンに挟まれるカーボン層を除去する。第1および第2のマスク層のパターンをマスクにハードマスク層をパターニングする。第1および第2のマスク層のパターンを除去する。ハードマスク層のパターンをマスクに被加工層をパターニングする。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択ゲートトランジスタのゲート電極間の間隔の縮小を実現する不揮発性半導体記憶装置を提供する。

【解決手段】実施の形態の不揮発性半導体記憶装置は、半導体基板と、第1の方向に伸長する複数の第1の素子領域と、第1の素子領域を互いに分離する第1の素子分離領域と、第1の方向に伸長する複数の第2の素子領域と、第2の素子領域を互いに分離する第2の素子分離領域と、第1の素子領域と第2の素子領域との間に設けられ、第1および第2の素子領域に接続され、第1の方向と直交する第2の方向に伸長する第3の素子領域と、第1および第3の素子領域上にまたがり、第2の方向に伸長する第1の選択ゲート電極と、第2および第3の素子領域上にまたがり、第1の選択ゲート電極に隣接して平行に配置される第2の選択ゲート電極と、第1および第2の選択ゲート電極間の第3の素子領域に接続されるコンタクト電極を有する。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】SiN膜等の犠牲膜の残存を防止する。

【解決手段】一の実施形態による不揮発性半導体記憶装置の製造方法では、基板上に、複数のメモリセルトランジスタと、複数の選択トランジスタとを形成する。さらに、前記方法では、前記メモリセルトランジスタ間と、前記メモリセルトランジスタと前記選択トランジスタとの間と、前記選択トランジスタ間に、第1から第5の絶縁膜を順に埋め込む。さらに、前記方法では、前記選択トランジスタ間の前記第2及び第4の絶縁膜が一部残存するように、第1のエッチング処理により、前記第2及び第4の絶縁膜を除去する。さらに、前記方法では、前記選択トランジスタ間に残存した前記第2及び第4の絶縁膜を、前記第1のエッチング処理後に行う第2のエッチング処理により除去する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高集積化に適した不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第3のフィン型積層構造Fin1〜Fin3を有する。第1乃至第3のフィン型積層構造Fin1〜Fin3は、第1の方向に積み重ねられる第1及び第2の半導体層Sm1,Sm2を備える。第1及び第2のアシストゲート電極AG1,AG2は、第3の方向に並んで配置され、第3のフィン型積層構造Fin3の第1の方向にある表面上で互いに分断される。第1のアシストゲートトランジスタAGT1は、第1及び第3のフィン型積層構造Fin1,Fin3内に形成され、第2のアシストゲートトランジスタAGT2は、第2及び第3のフィン型積層構造Fin2,Fin3内に形成される。

(もっと読む)

半導体記憶装置

【課題】 ビット線選択回路の小型化を図るとともにビット線の駆動時間を高速に行うことができる半導体記憶装置を提供する。

【解決手段】 フラッシュメモリ10は、セルユニットNUが行列状に複数配置されたメモリアレイ100と、セルユニットNUに接続されたビット線を選択するビット線選択回路200とを有する。ビット線選択回路200は、偶数ビット線GBL_e、奇数ビット線GBL_oをセンス回路に選択的に接続するための選択トランジスタSEL_e、SEL_o、BLSを含む第1の選択部210と、偶数ビット線GBL_eおよび奇数ビット線GBL_oに選択的にバイアス電圧を印加するためのバイアストランジスタYSEL_e、YSEL_oとを含む第2の選択部220とを有する。第2の選択部220のバイアストランジスタYSEL_e、YSEL_oは、記憶素子と共通のウエル内に形成される。

(もっと読む)

半導体記憶装置

【課題】制御ゲート電極と浮遊ゲート電極との間のカップリングを確保しつつ、浮遊ゲート電極間の干渉を抑制することができる半導体記憶装置を提供する。

【解決手段】アクティブエリア12上に設けられたトンネル膜13と、前記トンネル膜上に設けられた浮遊ゲート電極14と、前記浮遊ゲート電極上に設けられ、前記第1方向に対して交差した第2方向に延びる電極間絶縁膜18と、制御ゲート電極19と、前記第2方向において隣り合う前記アクティブエリア間、前記トンネル膜間及び前記浮遊ゲート電極間に設けられた下側絶縁部16と、前記下側絶縁部と前記電極間絶縁膜との間に設けられ、上面が前記浮遊ゲート電極の上面よりも上方に位置している上側絶縁部17と、を備える。前記下側絶縁部は気体部分を有する。そして、前記上側絶縁部の比誘電率は前記下側絶縁部の比誘電率よりも高く、前記電極間絶縁膜の比誘電率は前記上側絶縁部の比誘電率よりも高い。

(もっと読む)

メモリ回路

【課題】電源投入時における誤書き込みが発生しにくいメモリ回路を提供する。

【解決手段】メモリ回路10は、書き込み時のみにソース・ドレイン間に電圧を印加されて書き込まれる、書き込み用のPチャネル型不揮発性メモリ素子15と、コントロールゲート及びフローティングゲートがPチャネル型不揮発性メモリ素子15のコントロールゲート及びフローティングゲートとそれぞれ共通にされ、読み出し時のみにソース・ドレイン間に電圧を印加されて読み出される、読み出し用のNチャネル型不揮発性メモリ素子16と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】スプリットゲート構造の不揮発性メモリセルを有する半導体装置において、メモリアレイのレイアウト面積を低減する。

【解決手段】給電領域において、メモリゲートシャント部が形成される領域の素子分離部に溝25が形成されており、選択ゲートシャント部に備わる選択ゲートシャント電極VCは、メモリセル形成領域に形成された選択ゲート電極CGに繋がる第1導電膜からなり、メモリゲートシャント部に備わるメモリゲートシャント電極VMは、給電領域に形成された選択ゲート電極CGの延長部の片側面の一部および素子分離部に形成された溝25の側面の一部に絶縁膜6b,6tおよび電荷蓄積層CSLを介してサイドウォール状に形成され、メモリセル形成領域に形成されたメモリゲート電極MGに繋がる第2導電膜からなる。

(もっと読む)

半導体装置

【課題】浮遊状態の配線と洗浄水との間において高い密度で電荷が移動することに起因する配線の高抵抗化を防ぐ。

【解決手段】半導体製造装置の製造工程中において、半導体基板1Sなどと絶縁された浮遊状態となる銅配線である第1層配線L1の上面に、電気的に機能する接続ビアPL2と電気的に機能しないダミービアDP2とを接続させて形成する。これにより、第1層配線L1の上面に接続ビアPL2を形成するためのビアホールを形成した後の洗浄工程中に、第1層配線L1に溜まった電荷が洗浄水中に移動する際、前記電荷をダミービアDP2形成用のビアホールにも分散させることで、接続ビアPL2形成用のビアホールの底部のみに前記電荷が集中することを防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】スループットを低下させずに異なるメモリセルの誘電体膜とキャパシタの誘電体膜を同時に形成するための半導体装置の製造方法を提供する。

【解決手段】第1酸化膜18、窒化膜19、第2酸化膜20を順に形成した第1の誘電体膜を第1の半導体膜16上に形成する工程と、第1領域I内の第1の誘電体膜21をエッチングする工程と、第1領域Iの半導体基板1の表面に第3酸化膜25を形成する工程と、第1領域VI及び第2領域IIIに開口部28a、28bを有し、さらに第3領域II内の第1の誘電体膜21を覆う形状を有するマスク28を半導体基板1の上方に形成する工程と、マスク28の開口部28a、28bを通して、第1領域VI内の前記第3酸化膜25と前記第2領域III内の第1の誘電体膜21の第2酸化膜20を同時にエッチングする工程を含む。

(もっと読む)

メモリストリングにダイオードを有する3次元アレイのメモリアーキテクチャ

【課題】信頼でき、非常に小型の3次元集積回路メモリ用の構造を低い製造コストで提供する。

【解決手段】3次元アレイは第1の端部と第2の端部を含む2つの端部を有し、第1の端部と第2の端部の一方はビット線BLに接続され、第1の端部と第2の端部の他方はソース線CSLに接続される不揮発性メモリセルのNANDストリングのスタック1412、1413、1414と、ビット線BL及びソース線SLの一方をメモリセルのストリング1412、1413、1414に接続させるダイオード1492を有する。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲートトランジスタのゲート電極間の間隔の縮小を実現する不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板に、複数の第1の素子領域と、素子分離領域と、第2の素子領域を形成する。第1の素子領域上に、メモリセルゲート電極、2本の選択ゲート電極を形成し、第2の素子領域に周辺ゲート電極を形成する。第1の絶縁膜を形成し、周辺ゲート電極の側壁部上が開口される第1のレジストパターンを形成し、第1のエッチング処理を行い、側壁絶縁膜を形成する。第2のレジストパターンを形成し、第2のエッチング処理を行い、選択ゲート電極側壁部の第1の絶縁膜を除去する。第2の絶縁膜を堆積し、第3の絶縁膜を堆積する。2本の選択ゲート電極間上が開口される第3のレジストパターンを形成し、第3のエッチングおよび第4のエッチング処理を行い、コンタクトホールを形成する。

(もっと読む)

半導体メモリ装置

【課題】酸化物半導体のようなバンドギャップが大きな半導体を用いたメモリ装置の保持特性を高める。

【解決手段】ビット線の一端にバックゲートを有するトランジスタ(バックゲートトランジスタ)を直列に挿入し、そのバックゲートの電位は常に十分な負の値となるようにする。また、ビット線の最低電位はワード線の最低電位よりも高くなるようにする。電源が切れた際には、ビット線はバックゲートトランジスタによって遮断され、ビット線に蓄積された電荷が流出することが十分に抑制される。この際、セルトランジスタのゲートの電位は0Vであり、一方で、そのソースやドレイン(ビット線)の電位は、ゲートよりも十分に高いので、セルトランジスタは十分なオフ状態であり、データを保持できる。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

デュアル機能を有する不揮発性半導体メモリセル

【課題】デュアル機能を有する不揮発性半導体メモリセルは、基板、第1ゲート、第2ゲート、第3ゲート、電荷蓄積層、第1拡散領域、第2拡散領域及び第3拡散領域を有する。

【解決手段】第2ゲート及び第3ゲートは、デュアル機能のワンタイムプログラミング機能に対応する第1電圧及びデュアル機能のマルチタイムプログラミング機能に対応する第2電圧を受けるために用いられる。第1拡散領域は、ワンタイムプログラミング機能に対応する第3電圧及びマルチタイムプログラミング機能に対応する第4電圧を受けるために用いられる。第2拡散領域は、マルチタイムプログラミング機能に対応する第5電圧を受けるために用いられる。

(もっと読む)

半導体装置

【課題】電力供給がない状況で記憶保持が可能で、書き込み回数に制限が無い、新たな半導体装置を提供する。

【解決手段】チャネル領域と第1のゲート絶縁層と第1のゲート電極と第1のソース及びドレイン電極とを有する第1のトランジスタと、酸化物半導体層140と第2のソース電極142a及び第2のドレイン電極142bと第2のゲート絶縁層146と第2のゲート電極148aとを有する第2のトランジスタ162と、第2のソース電極142aまたは第2のドレイン電極142bの一方と第2のゲート絶縁層146と第2のゲート絶縁層146上に第2のソース電極142a又は第2のドレイン電極142bの一方と重なるように設けられた第3の電極148bとを有する容量素子164と、を有し、第1のゲート電極と第2のソース電極142a又は第2のドレイン電極142bの一方とは接続され、第3の電極148bは酸化物半導体層140と重なる領域を有する。

(もっと読む)

81 - 100 / 1,873

[ Back to top ]