Fターム[5F101BB05]の内容

不揮発性半導体メモリ (42,765) | 制御 (5,368) | 制御装置 (5,154) | CGを有するもの (4,139) | スタックゲート(同一端部) (1,873)

Fターム[5F101BB05]に分類される特許

141 - 160 / 1,873

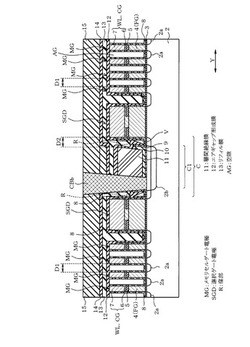

半導体記憶装置および半導体記憶装置の製造方法

【課題】隣接するメモリセルゲート電極間に空隙を形成することで結合容量を抑制し、複数のコンタクト同士の短絡を防止しメモリの信頼性を向上する。

【解決手段】半導体記憶装置は、複数の選択ゲート電極間に形成され、選択ゲート電極に近接した側の側面と当該選択ゲート電極との第2間隔が第1間隔より広い層間絶縁膜11と、複数のメモリセルゲート電極間に空隙AGを備えるよう当該空隙AGの上部を被覆し、複数の選択ゲート電極間においては当該選択ゲート電極の側面および層間絶縁膜11の側面に沿って形成され、その上部に窪部Rを備えて形成されたエアギャップ形成膜12と、複数のメモリセルゲート電極上のエアギャップ形成膜12上に形成され、複数の選択ゲート電極間ではエアギャップ形成膜12の窪部Rの内側に埋込まれたリフィル膜13と、複数の素子領域に接触するように層間絶縁膜11に形成された複数のコンタクトCBa,CBbを備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁膜の不要な部分を除去するときのエッチングとして、ウェットエッチングを用いても、浮遊ゲート絶縁膜がサイドエッチングされることを抑制する。

【解決手段】選択ゲート絶縁膜172は浮遊ゲート絶縁膜110の隣に位置している。選択ゲート電極170は選択ゲート絶縁膜172上に位置しており、側面が第2絶縁膜152を介して浮遊ゲート電極120の第1側面に接続している。消去ゲート電極180は、第3絶縁膜160を介して浮遊ゲート電極120に接続している。第2絶縁膜152の下端は、浮遊ゲート絶縁膜110の上面よりも、半導体基板100の表面の近くに位置している。第2絶縁膜152の下端から半導体基板100の表面までの距離は、選択ゲート絶縁膜172の厚さよりも大きい。

(もっと読む)

不揮発性メモリ装置

【課題】 パストランジスタ間の空間確保が可能な不揮発性メモリ装置を提供する

【解決手段】 不揮発性メモリ装置100が備える行デコーダ120は、パストランジスタ部123_L、123_Rを含む。パストランジスタ部123_L、123_Rは、メモリブロック110の左右に配列される。ブロック選択信号BLKWL1によって共通ゲートを形成するパストランジスタ端Pass TR 0とパストランジスタ端Pass TR 8とは、選択的に活性化される第1駆動信号ラインSI1及び第2駆動信号ラインSI2によって独立して駆動される。互に異なるブロック選択信号BLKWLによって駆動されるパストランジスタは、1つの活性領域の上に形成され得る。これにより、1つの活性領域の上に2つのパストランジスタを形成する場合、パストランジスタ部123_L、123_Rのチャンネル方向の大きさを減らすことができる。

(もっと読む)

電界効果トランジスタおよびそれを用いたメモリおよび半導体回路

【課題】微細化した半導体集積回路において用いられる、オフ電流の小さな電界効果トランジスタ(FET)を提供する。

【解決手段】絶縁表面に略垂直に形成された厚さが1nm以上30nm以下の薄片状の酸化物半導体と、前記酸化物半導体を覆って形成されたゲート絶縁膜と、前記ゲート絶縁膜を覆って形成されたストライプ状の幅10nm以上100nm以下のゲートを有する電界効果トランジスタ。この構成では、薄片状の酸化物半導体の三方の面をゲートが覆うこととなるため、ソース、ドレインから注入される電子を効率的に排除し、ソースとドレインの間をほぼ空乏化領域とでき、オフ電流を低減できる。

(もっと読む)

トンネル障壁の上に電界分布層を有する電荷捕獲装置

【課題】チャネル幅寸法に沿った電荷捕獲構造の電荷密度が一様でない場合でもチャネル幅寸法に沿ってしきい値電圧を一様に維持したフラッシュメモリセルおよびフラッシュメモリセルの製造方法を提供する。

【解決手段】ソース領域及びドレイン領域を有する表面を有し、前記ソース領域及び前記ドレイン領域がチャネル領域によって分離された半導体基板と、前記チャネル領域の上の前記基板の表面上に配置された3nmを超える実質的なゲート絶縁膜厚を有するトンネル障壁絶縁体構造105、前記トンネル障壁絶縁体構造及び前記チャネル領域の上に配置された導電層101、前記導電層及び前記チャネル領域の上に配置された電子捕獲構造106、並びに前記電子捕獲構造及び前記チャネル領域の上に配置された上側絶縁体構造107を有する、前記チャネル上の多層スタックと、前記上側絶縁体構造及び前記チャネル領域の上に配置された上側導電層108とを具える。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、少なくとも酸化物半導体膜中に希ガスイオンを注入する注入工程を行い、減圧下、窒素雰囲気下、又は希ガス雰囲気下において、希ガスイオンを注入した酸化物半導体膜に加熱工程を行って希ガスイオンを注入した酸化物半導体膜中に含まれる水素若しくは水を放出させ、酸化物半導体膜を高純度化する。

(もっと読む)

NAND型不揮発性メモリのデータ消去方法

【課題】NAND型不揮発性メモリを提供する。

【解決手段】ビット線と、ソース線と、複数の不揮発性メモリが直列に接続されたNAND型セルと、選択トランジスタと、を有し、不揮発性メモリは、第1の絶縁膜を介した半導体上の電荷蓄積層と、第2の絶縁膜を介した電荷蓄積層上の制御ゲートと、を有し、NAND型セルの一方の端子は、選択トランジスタを介して、ビット線に接続され、NAND型セルの他方の端子は、ソース線に接続されたNAND型不揮発性メモリであって、第1の絶縁膜は、半導体に酸素雰囲気で高密度プラズマ処理を行った後、窒素雰囲気で高密度プラズマ処理を行うことで形成されるNAND型不揮発性メモリ。

(もっと読む)

半導体装置の製造方法

【課題】 セレクトゲート部におけるゲート閾値電圧が安定した半導体装置の製造方法を提供する。

【解決手段】 実施形態に係る半導体装置の製造方法では、メモリセル部及びセレクトゲート部が形成される。半導体基板上にトンネル絶縁膜が形成され、前記トンネル絶縁膜上に電荷蓄積層が形成される。前記電荷蓄積層、前記トンネル絶縁膜、及び前記半導体基板のエッチングにより素子分離溝部が形成され、前記電荷蓄積層の側面に接するように前記素子分離溝部に素子分離絶縁膜が埋め込まれる。前記電荷蓄積層及び前記素子分離絶縁膜上に電極間絶縁膜が形成され、前記セレクトゲート部において、前記電極間絶縁膜がエッチングされる。前記電極間絶縁膜を覆い、前記電荷蓄積層に接続するシリコン膜が形成され、前記シリコン膜上に金属膜が形成される。熱処理により、前記セレクトゲート部において、前記トンネル絶縁膜に接する前記電荷蓄積層がシリサイド化される。

(もっと読む)

半導体集積回路

【課題】不揮発性メモリを搭載した半導体集積回路において、外部端子を通して不揮発性メモリの特性テストを実施し、更に、その外部端子にサージ電圧が印加された場合であっても、そのサージ電圧が不揮発性メモリに伝わることを防止する。

【解決手段】半導体集積回路は、不揮発性メモリと、不揮発性メモリに対するデータ書き込み時、書き込み電圧が印加される書き込み制御線と、書き込み制御線に接続された第1ノードと、第1スイッチ回路を介して第1ノードに接続された外部端子と、スイッチ回路を介さずに外部端子に接続された第1ESD保護回路と、動作モードに応じて第1スイッチ回路をON/OFF制御する制御回路と、を備える。動作モードは、外部端子を用いて不揮発性メモリの特性テストを行うテストモードと、外部端子を使用しないユーザモードと、を含む。テストモードにおいて、制御回路は、第1スイッチ回路をONする。ユーザモードにおいて、制御回路は、第1スイッチ回路をOFFする。

(もっと読む)

半導体装置

【課題】従来は、外部機器側で情報の書き込みが正常に成されたか否かを判断していた。また、半導体装置ないに大掛かりな回路を構成しなければ、正しく書き込みを判断できなかった。

【解決手段】外部機器から入力される書込パルスのうち、そのパルス長で、搭載する不揮発性記憶手段に情報が正しく書き込まれたか否かの判定を行なう判断手段を設けた。判断手段は、書込パルスのパルス長が所定の範囲にあるか否かや、書込パルスの到来と同時に時間を計測する計時手段などを用いることで、パルス長が正しいか否かを判定する。これにより、簡便な構成で、正しい情報の書き込みを判断できる。

(もっと読む)

フィン型不揮発性メモリ素子

【課題】不揮発性メモリ素子は小型化や低消費電力化の要求がある。不揮発性メモリ素子をフィン型とすれば小型化できるが、バルク領域に正しく電位を印加できないので正しく情報の書き込みと消去とができなかった。

【解決手段】本発明のフィン型不揮発性メモリ素子は、不揮発性メモリ素子のゲート電極とは別に、バルク領域に直接電位を印加するバルク電極を設けた。これにより、バルク領域の電位を自由に印加できるようになり、正しく情報が書き込み及び消去できるようになる。また、バルク電位を自由に可変できるので、書き込みや消去にかかる電圧を低下させることもでき、低消費電力化を行える。

(もっと読む)

不揮発プログラマブルロジックスイッチ

【課題】 誤動作を防ぐとともに、サイズが小さい不揮発プログラマブルロジックスイッチを提供すること。

【解決手段】 本発明の実施形態による不揮発プログラマブルロジックスイッチは、制御ゲートが第1の配線に接続され、第1のソースドレイン端が第2の配線に接続され、電荷を蓄積する膜を有する第1のメモリセルトランジスタと、制御ゲートが前記第1の配線に接続され、第3のソースドレイン端が前記第1のメモリセルトランジスタの第2のソースドレイン端に接続され、第4のソースドレイン端が第3の配線に接続され、電荷を蓄積する膜を有する第2のメモリセルトランジスタと、前記第1のメモリセルトランジスタの前記第2のソースドレイン端と前記第2のメモリセルトランジスタの前記第3のソースドレイン端にゲート電極が接続されたパストランジスタと、前記パストランジスタのウェルに基板電圧を印加する第1の基板電極を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタの高容量化と面積の低減を可能とした半導体装置及びその製造方法を提供する。

【解決手段】EEPROMメモリセル50は、シリコン基板1のメモリセル領域に設けられたN-層21aと、トンネル絶縁膜13aと、浮遊ゲート電極15aと、電極間絶縁膜

17aと、制御ゲート電極19aと、を有する。また、キャパシタ60は、シリコン基板1のキャパシタ領域に設けられた下部電極層24aと、第1の誘電体膜13cと、共通電極15cと、第2の誘電体膜17cと、上部電極19cと、を有する。下部電極層24aと第1の誘電体膜13cと共通電極15cとにより第1のキャパシタ61が構成されると共に、共通電極15cと第2の誘電体膜17cと上部電極19cとにより第2のキャパシタ62が構成されており、第1のキャパシタ61と第2のキャパシタ62とが並列に接続されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】3次元に積層されたメモリセルトランジスタにおける誤動作を防止する。

【解決手段】不揮発性半導体記憶装置は、半導体基板20と、半導体基板の上方に形成された第1導電層40と、第1導電層の上方に順に積層された第2導電層43、電極間絶縁膜53’、および第3導電層43と、一対の貫通ホール49の内面上、および一対の貫通ホールの下端を連結させる連結ホール50の内面上に形成されたブロック絶縁膜53と、電荷蓄積層54と、トンネル絶縁膜55と、半導体層SPと、一対の貫通ホールの間に位置し、第2導電層、電極間絶縁膜、および第3導電層を分断するスリット46内に埋め込まれた絶縁材59と、第2導電層および第3導電層の表面上に形成されたシリサイド層58と、を具備し、スリットの内面に沿った第2導電層と第3導電層との間の距離は、積層方向に沿った第2導電層と第3導電層との距離よりも大きい。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】クラックや結晶欠陥の発生なしに高電圧トランジスタの素子領域間の耐圧を向上できるようにした不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリセル領域の第1素子分離絶縁層が当該メモリセル領域の第1素子分離溝内に第1の酸化膜を埋め込んで構成され、第1の酸化膜の上面が半導体基板の上面と第1ゲート電極の上面との間に存在するように構成されている。

周辺領域の第2素子分離絶縁層は、周辺領域の第2素子分離溝内の全体に埋込まれると共にその上面が半導体基板の上面の上方に突出した第1の酸化膜と、当該第1の酸化膜上に積層され、その上面が第1導電膜の上面より上方に突出している第2の酸化膜とで構成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体集積回路内の抵抗素子の抵抗値のばらつきを抑制した半導体装置を提供する。

【解決手段】半導体装置は基板を備える。第1の絶縁膜は基板上に設けられる。第1の抵抗部は第1の絶縁膜上に設けられる。境界膜は第1の抵抗部上に設けられる。第2の抵抗部は境界膜上に設けられる。第2の絶縁膜は、第2の抵抗部上に設けられている。第1の導電部および第2の導電部は、第2の絶縁膜上に設けられ、互いに絶縁されている。第1の導電部は、第2の絶縁膜および第2の抵抗部を貫通して境界膜の表面に接触する第1のコネクト部を含む。第2の導電部は、第2の絶縁膜および第2の抵抗部を貫通して境界膜の表面に接触する第2のコネクト部を含む。第1の抵抗部は、一端において第1のコネクト部を介して第1の導電部に電気的に接続され、かつ、他端において第2のコネクト部を介して第2の導電部に電気的に接続された抵抗素子である。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】製造工程数の削減が可能な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1、第2積層体、第1、第2半導体ピラー、第1、第2メモリ膜、接続部及び分断部を備えた不揮発性半導体記憶装置が提供される。第1、第2積層体は、第1軸に沿って積層された複数の第1、第2電極膜と、第1、第2電極膜間に設けられた第1、第2電極間絶縁膜と、をそれぞれ含む。第1、第2半導体ピラーは第1、第2積層体を第1軸に沿って貫通する。第2積層体は、第1積層体と並置される。接続部は第1、第2半導体ピラーを接続する。第1メモリ膜は、第1、第2電極膜と、第1、第2半導体ピラーとの間に設けられる。分断部は、第1、第2半導体ピラー間で第1、第2電極膜を分断し、接続部に接し、第1メモリ膜に用いられる材料を含む積層膜を含む。

(もっと読む)

膜形成方法および不揮発性記憶装置

【課題】より良質な膜を形成する。

【解決手段】実施形態の膜形成方法は、下地の上に設けられた酸素及び窒素の少なくともいずれかを含む膜の表面に、酸素及び窒素の少なくともいずれかを含むイオン化されたガスクラスタを照射して、前記ガスクラスタを照射した後の前記膜の密度を前記ガスクラスタを照射する前の前記膜の密度よりも高くする。

(もっと読む)

有機分子メモリ

【課題】電荷保持特性に優れた有機分子メモリを提供する。

【解決手段】実施の形態の有機分子メモリは第1の導電層と、第2の導電層と、第1の導電層と第2の導電層との間に設けられ、電荷蓄積型分子鎖または抵抗変化型分子鎖を含み、電荷蓄積型分子鎖または前記抵抗変化型分子鎖が縮合多環系の基を備える有機分子層と、を備えている。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】コンタクトと素子領域間にかかる電界を緩和し絶縁破壊を防ぐ。

【解決手段】実施形態の半導体装置は、基板上第1方向に延伸し並列し高さが同じ第1〜4分離、第1、2分離間の低い第1領域、高さが等しい第2、3分離間の第2領域、第3、4分離間の第3領域、第1領域上面、第1分離の第2分離に対向した側面および上面の一部、第2分離の第1分離に対向した側面および上面の一部に接する第1電極15−1、その第2方向で第3領域上面、第3分離の第4分離に対向した側面および上面の一部、第4分離の第3分離に対向した側面および上面の一部に接する第2電極15−2を有す。半導体装置は、第1電極の第2方向とは異なる方向に位置し第2領域上面、第2分離の第3分離に対向した側面および上面の一部、第3分離の第2分離に対向した側面および上面の一部に接する第3電極を有す。

(もっと読む)

141 - 160 / 1,873

[ Back to top ]